電力を賢く配分する「C2VR」

チップ全体の効率を最大化するインテルの将来戦略

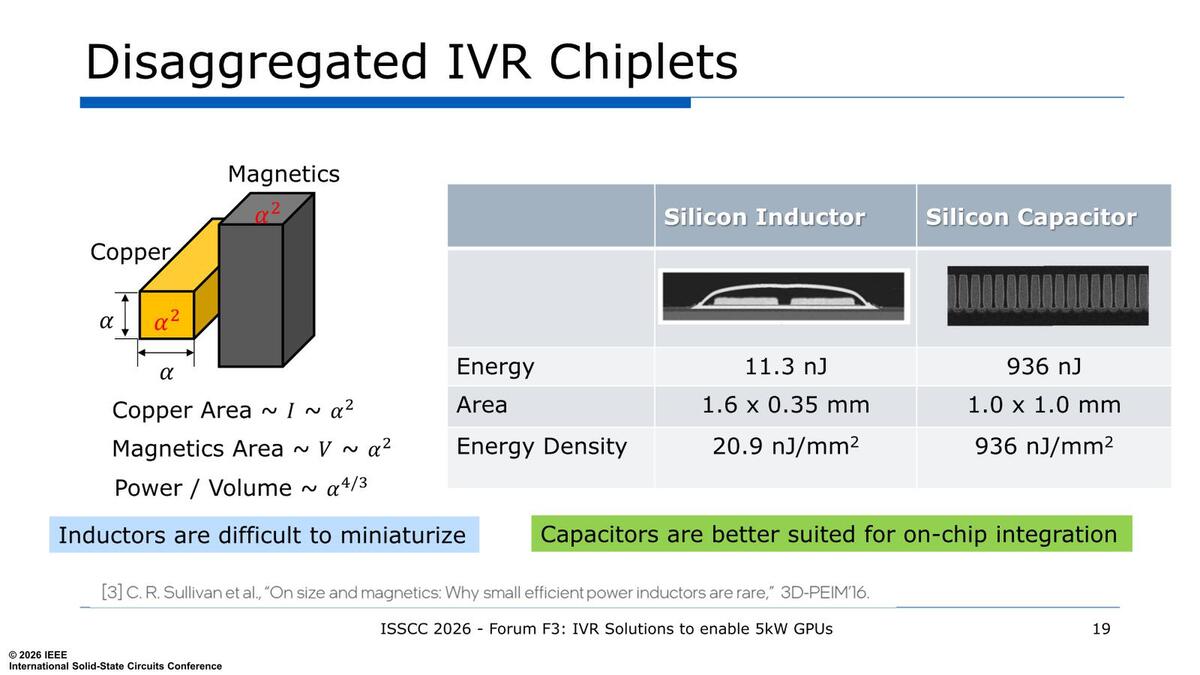

もう1つ考慮すべきなのがインダクタンスで、先にも述べたが磁性体を入れてもやはりインダクタンスを大きくするのには限界がある。

インダクターは、流れてきた電流で磁場を形成し、逆にその磁場から電流を出力する(コンデンサーは電流を電荷として蓄え、再び電荷から電流を出力する)仕組みであるが、その際に蓄えられるエネルギーはことシリコンベースで言えばキャパシターの足元にもおよばない

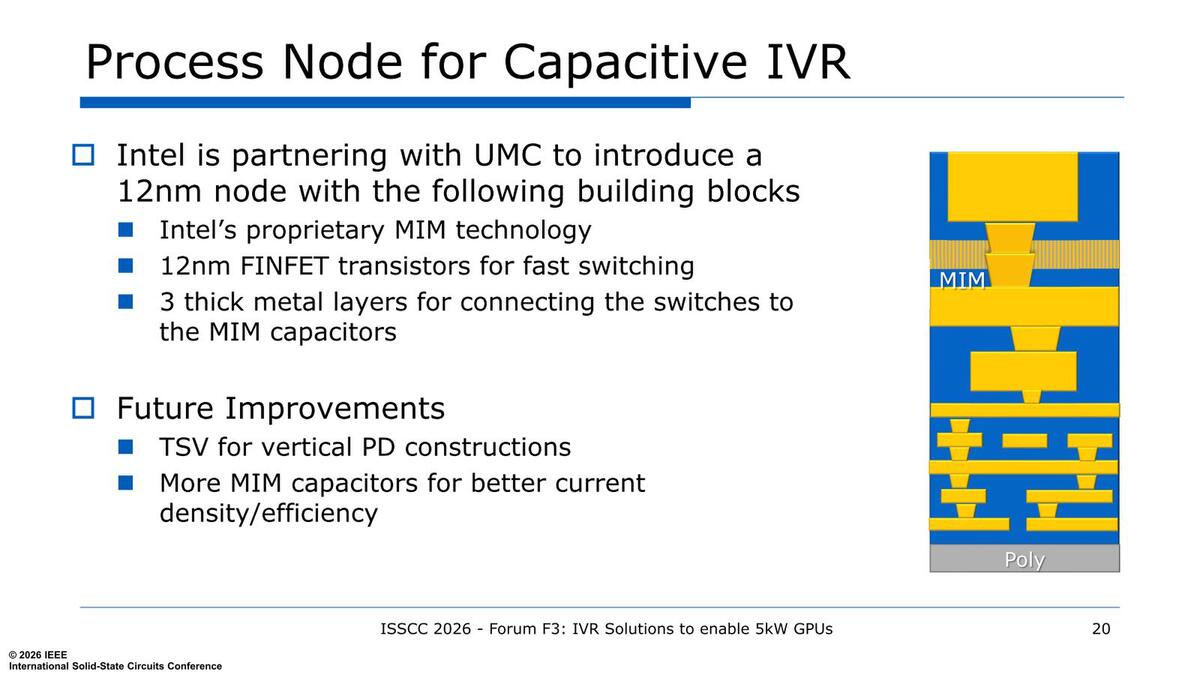

その一方でキャパシターの方は比較的伸びが期待できる。もともとIntel 10の世代にMIMキャパシターを統合し、Intel 4世代では容量をおおむね倍増させた話があったが、これに加えインテル/UMC共同の12nmプロセスにもMIMキャパシターを統合することが今回発表された。

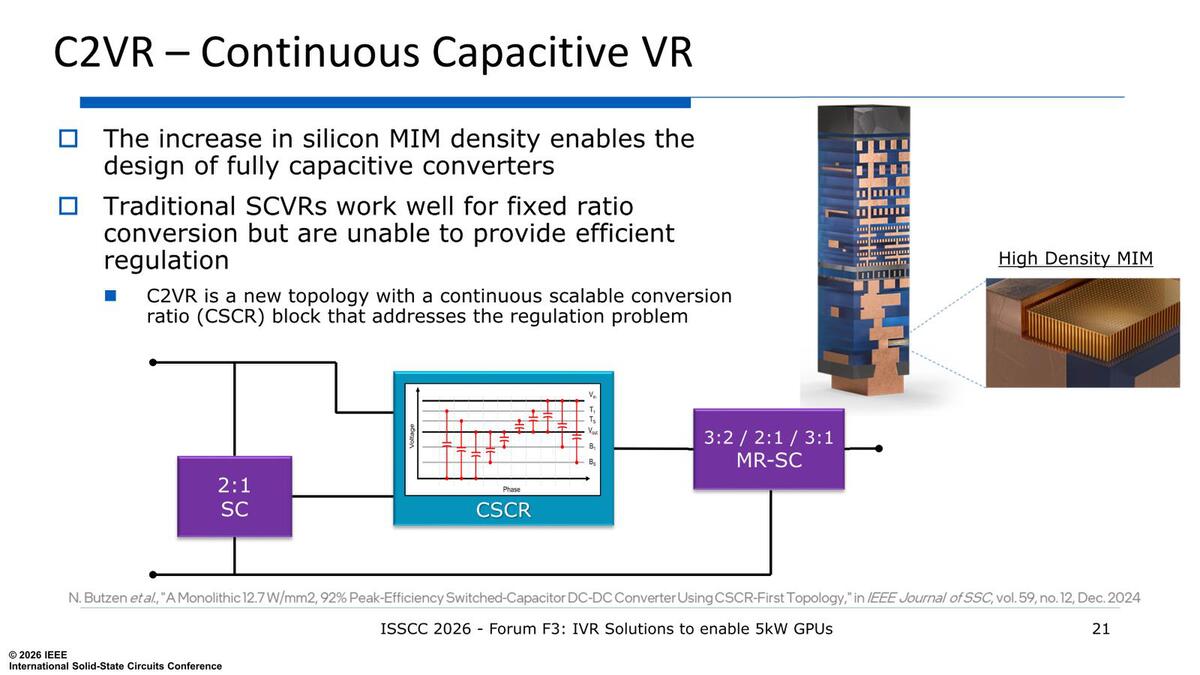

要するに、配線層を利用したMIMキャパシターはかなり広範なノードで利用可能になっている。このMIMキャパシターを利用したものとしてインテルが提唱するのがC2VRである。

C2VR。Vin/Voutという定格電圧以外にT1...TS/B1...BSという複数の出力電圧レベルにあわせてMIM キャパシターを配することで、電圧を変更しても効率を高く維持しようという仕組みである

一般にVRでは一番効率を高めたい出力に合わせて設計するので、そこから外れるとどうしても効率が落ちる。効率を高めるにはコンデンサーやインダクタンスの容量を変化させることが必要だが、インダクタンスはともかくコンデンサーに関してはチップ全体に配された配線層のMIMキャパシターを利用することで、幅広い最適化ポイントに対応した容量を提供できるようにするというのがこのC2VRの骨子となる。

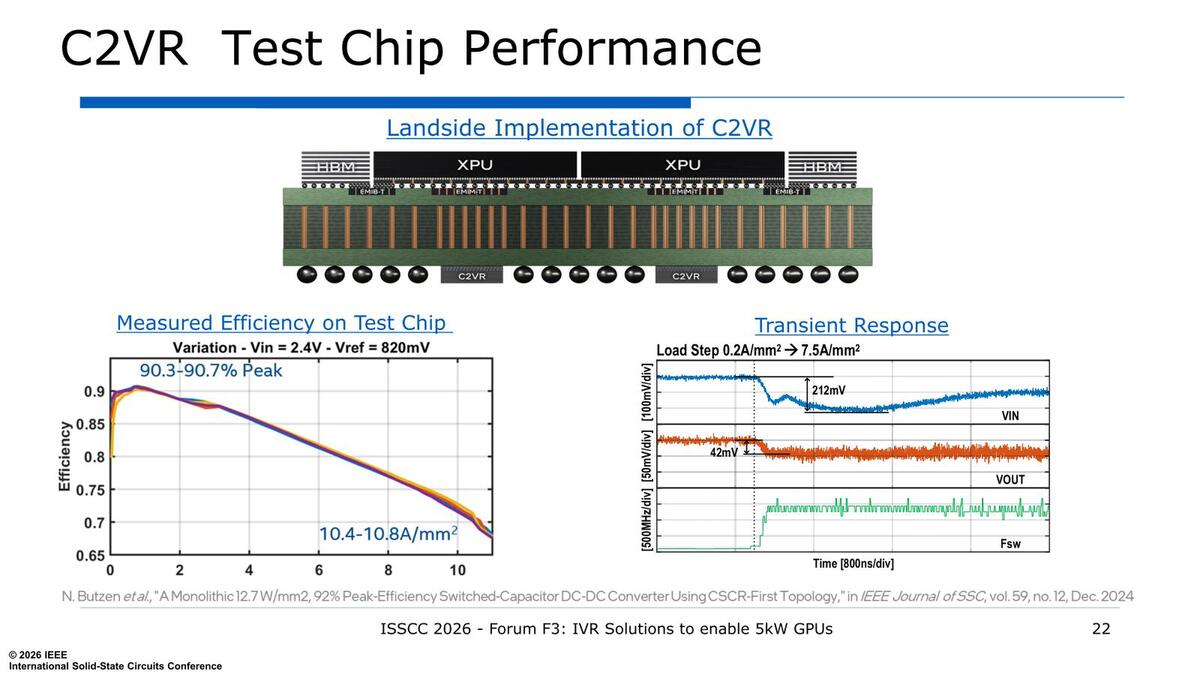

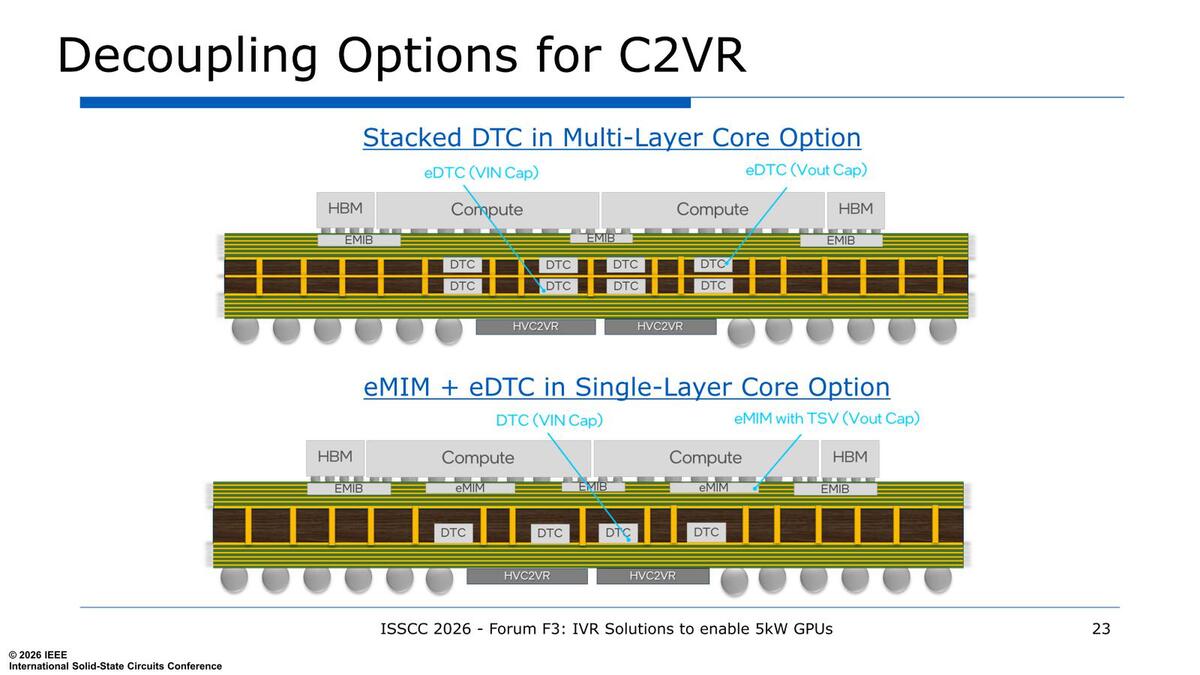

実際にテストチップを製造した結果は良好とされる。将来的には配線層のMIMキャパシターに加えてEMIB-T内のeMIMやインターポーザー内にeDTCを統合することでさらに容量を稼ぎやすい。

C2VRテストチップの性能。少しわかりにくいが、左グラフの横軸は電流密度(A/mm2)、グラフは入力2.4Vに対して出力が0.82Vの場合を複数測定した結果の模様。右グラフは出力を0.2A/mm2→7.5A/mm2に増加させたときの入出力の電圧降下と追従時間を示したものだ

どちらかといえばインターポーザー内にDTCを埋め込む方が容量は稼げるだろうが、インターポーザーの厚みが増すのが問題だろうか? あとはコスト増だが、チップそのものが超高価なので、それに比べれば大した問題ではないだろう

これを組み合わせた場合の電力供給(2ページ目最初の画像で示したもの)の改善案が下の画像だ。まだ多いといえば多いのだが、2ページ目最初の画像に比べると大分マシになっているのがわかる。

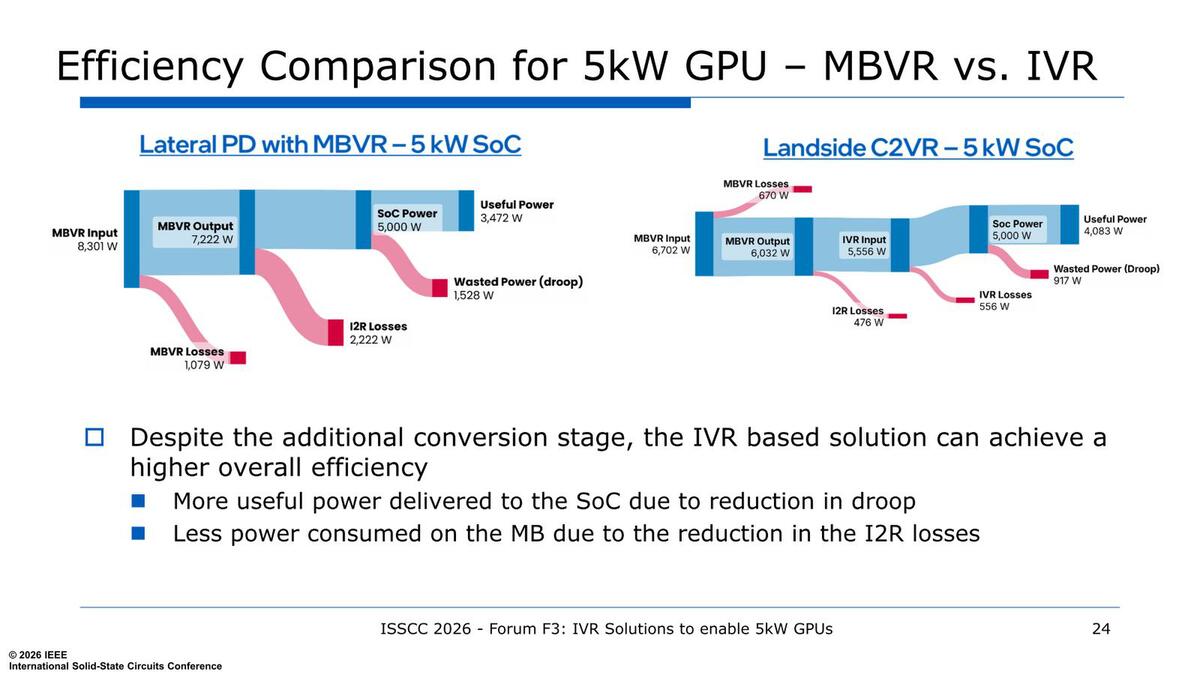

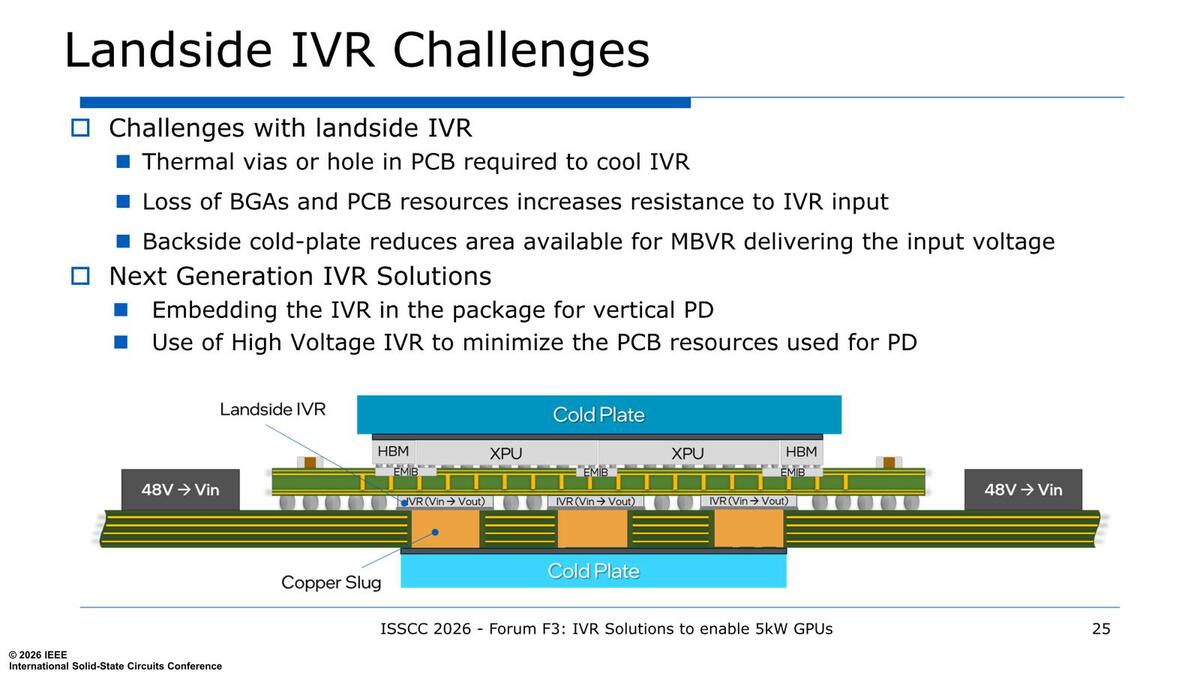

もちろん問題もあって、そのIVRの冷却はどうするんだ? という話だが、1つの案として出されているのが下の画像である。基板中に銅柱を埋め込み、これを経由して基板裏側のコールドプレートで放熱するという、なかなかの力業である。

今回の問題は、パッケージ単体のソリューションではないことだろう。つまり配線層にMIMキャパシターを構築できることを前提にC2VRを構築しているわけで、これはつまりインテルのプロセスでしか利用できないソリューションになっているわけだ。

とはいえ、VRをチップにどう統合していくかというのは、今後各社のGPU/AIプロセッサーソリューションでは欠かせない要素になっていくものと思われる。あるいはインテルはこのC2VRを武器にデザインウインを獲りたいのかもしれない。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります