パッケージにコンデンサーを埋め込む

一度は廃止されたFIVR(チップ内電圧レギュレーター)への再挑戦

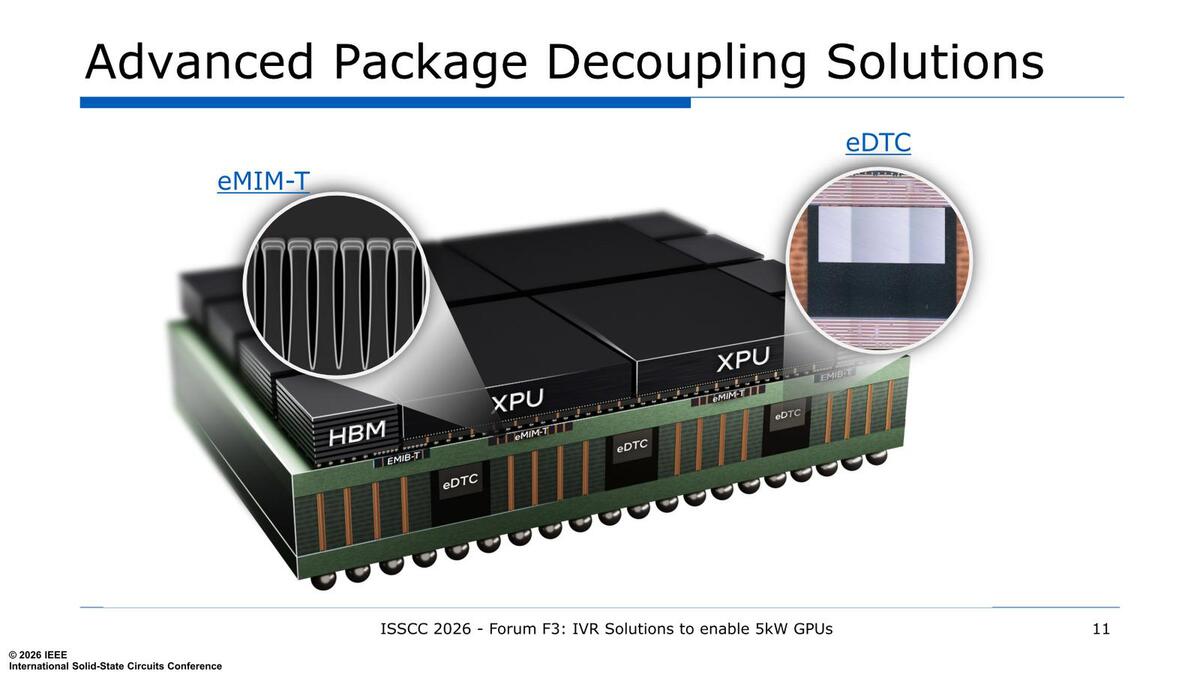

さてここからが講演の本題である。VPDを前提に、どうパッケージ基板はあるべきかという話である。先にも触れたが、VPDではパスコンを配しにくいのは事実だが、ナシというわけもいかない。そこで効いてくるのが、パッケージ内にコンデンサーを実装しようという発想だ。

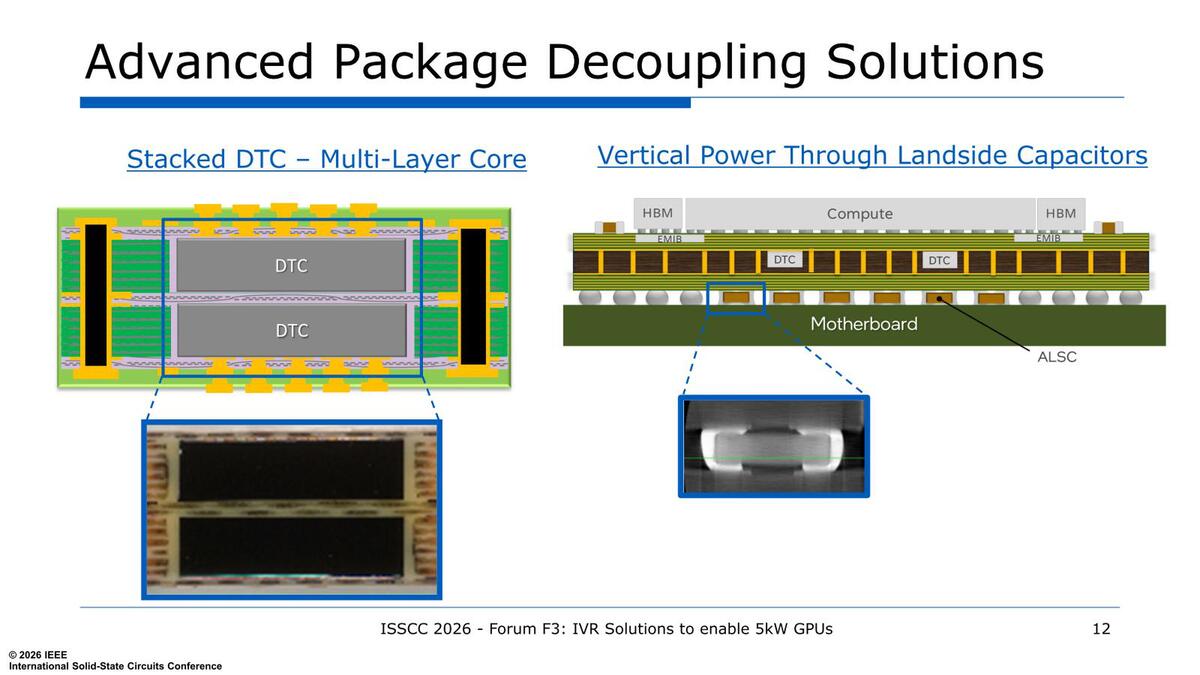

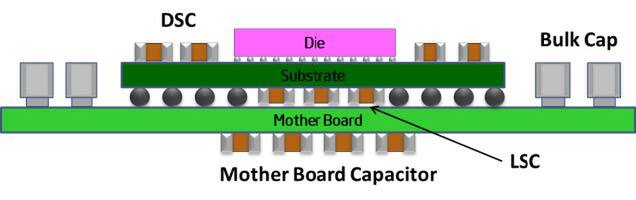

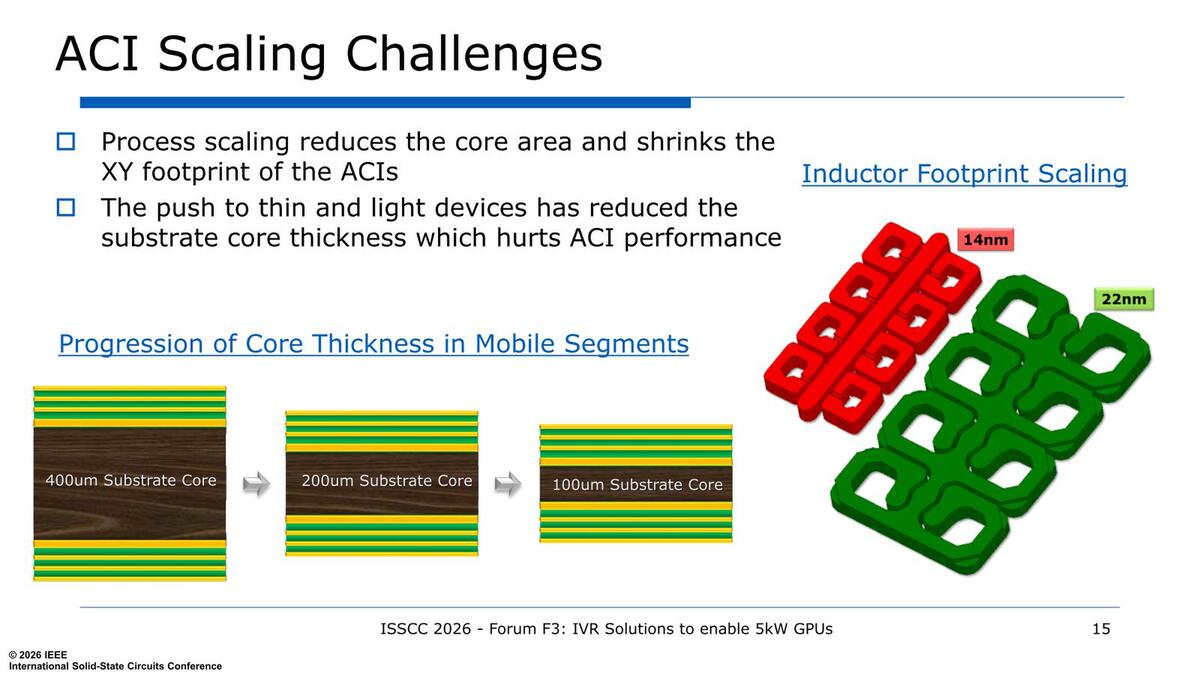

パッケージ内にコンデンサーを実装する取り組み。eMIMはembedded Metal Insulated Metal (Capacitor)、eDTCはembedded Deep Trench Capacitorの略だ

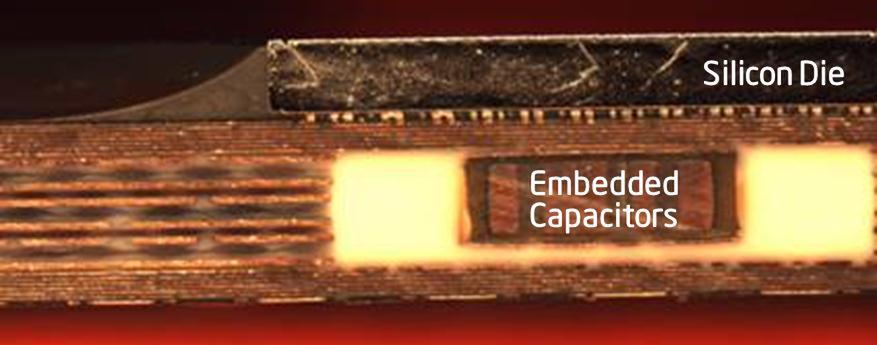

これは今に始まった話ではない。先に触れたようにEMIB-TにはMIMキャパシターが内蔵できるし、パッケージ基板にキャパシターを実装するのは例が違うが、Meteor Lake世代でベースタイルに3Dキャパシターを内蔵していた事例に通じるものがある。

もともとパッケージ基板の中にさまざまなパッシブ部品を入れる試みは昔からあり、この延長にあると考えればいいだろう。全体として、従来コンデンサーが実装されていた場所にVRが配されるので、その代替場所を基板内部に求めるのは理屈に適ったやり方だ。

それならパッケージ内部や基板内部にコンデンサーを埋め込めば足りるか? といえば全然足りない。そもそも1kW→5kWに供給電力が増えている時点で、それに応じて必要となるキャパシターの容量も増えるし、パッケージ/基板内部のキャパシターの容量は従来のパスコンよりも小さくなるため、絶対的に不足する(*1)。

(*1) 厳密に言うなら、従来のパスコンに比べるとよりチップに近いところにキャパシターが位置する関係で、容量は少なくても同様の働きをする(より早く電力供給ができるようになる)というメリットがあるが、いかんせん容量そのものは大きく減るので、いくら近いとはいえ同等になるとはいえない。

そこで容量を増やす方策はいろいろと考えられている。DTCに関してはインターポーザーをやや厚めにして複数個積層するとか、LCS(Land Side Capacitor)を使うなどだ。

実はDTCやLCSに関しては、2013年のECTC(Electronic Components and Technology Conference)という半導体パッケージの学会でインテルが"Embedded Capacitors in the Next Generation Processor"という論文を発表しており、(当時の)次世代XeonにDTCやLTSを利用することを明らかにしている。

要するにもうインテルとしてはこのあたりの対策はすでにある程度取っているのであって、来る5kW世代に向けても現在の延長では対応策としては足りない、という話である。

では根本的にどう解決するか? であるが、そもそもI2Rロス、つまりE=I2×Rで示される配線抵抗に起因するロスは、電流値の2乗で効いてくるのが問題である。例えば電圧1V、配線抵抗0.0001Ωとしよう。1000Wの場合には1000Aが流れるので、配線抵抗は10002×0.0001=100Wになる。ところが5000Wでは5000Aなので50002×0.0001=2500Wになる。

実際には配線抵抗のロス分はチップに行かないので、それも加味して1000Wなら1200W近く、5000Wなら9000W近く供給しないとそれぞれ1000W/5000Wがチップに行かないことになる。

電圧を12Vにするとどうなるか? というと、1000Wなら83.3A、5000Wでも416.7Aほどまで電流量が下がる。結果、配線抵抗のロスは1000Wの場合で0.7W、5000Wの場合でも17.4Wほどで収まることになる。

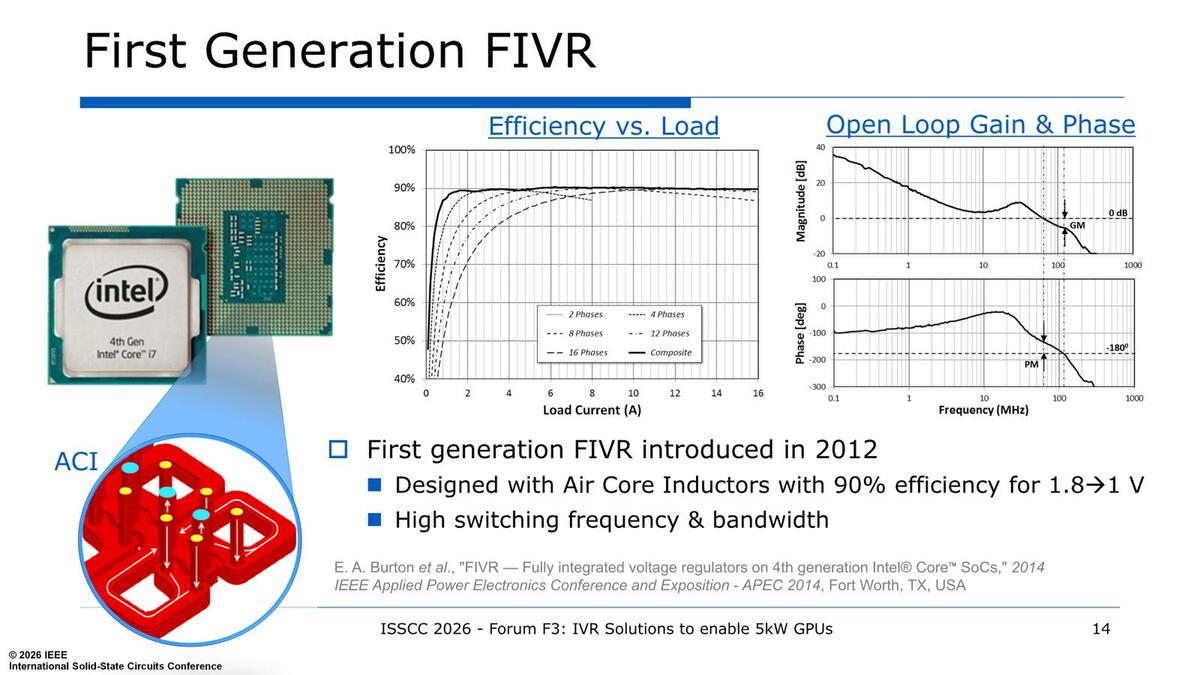

ただチップに直接12Vを供給したらトランジスタが間違いなく燃えるので1V未満(先端プロセスでは0.5Vあたり)まで落とさないといけない。この矛盾を解決する方法がIVR(Integrated Voltage Regulator)である。インテルはこれをFIVR(Fully IVR)と称しているが、要するにチップ外に部品を置かずに、完全にチップ内で動作するという意味である。

最初にこのFIVRを実装したのはHaswellこと第4世代Coreプロセッサーである。

しかしFIVRの実装は長続きせず、第6世代CoreプロセッサーであるSkylakeの世代では廃止されている。理由は簡単で、ハイエンドのデスクトップ向け(S SKU)には効果的なFIVRだが、モバイル向けの超低消費電力向け(U/Y SKU)にはFIVRでは非効率だったからだ。

結局、用途別にCPUパッケージの外にVRを置いた方がトータルで効率的と判断されたことで、一旦コンシューマー向けからは外されたFIVRだったが、サーバー向けにはその後も模索され続けた。ただ微細化にともない、コイルがどうしても薄型化・小型化の傾向にあり、インダクターの大きさも小さくなる欠点が顕著になってきた。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります