電力ロスを最小化!

チップの裏から給電するVPD(垂直給電)の仕組みと課題

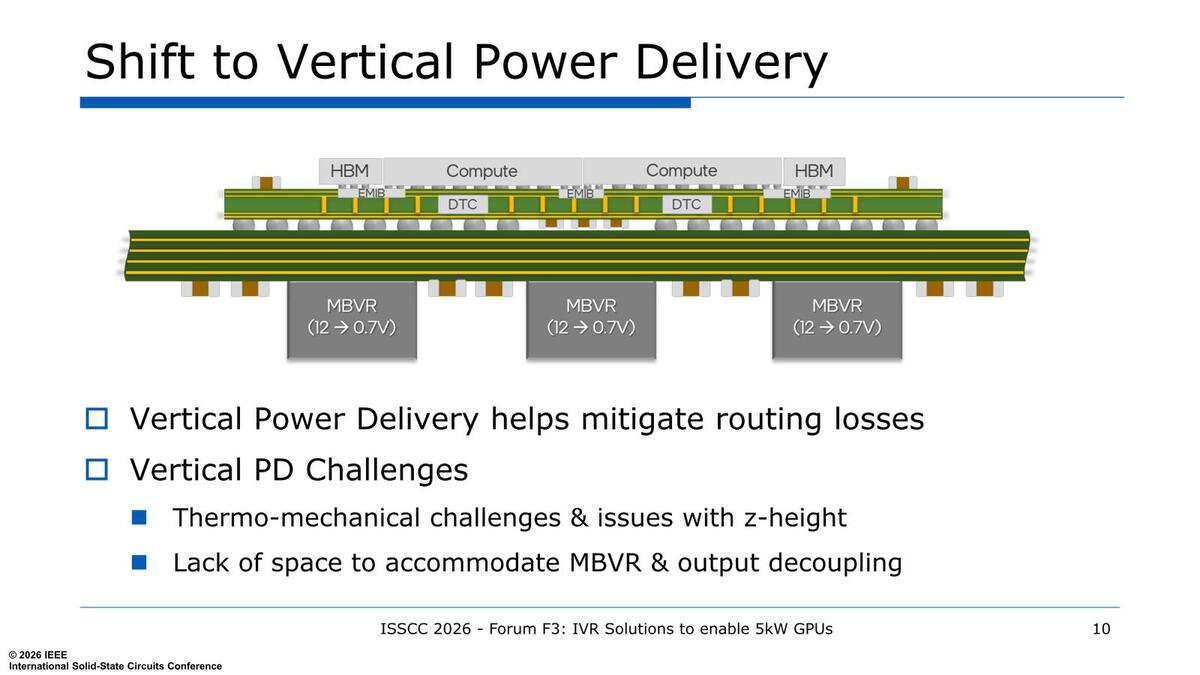

では電力配線はどうなっているか? が下の画像だ。これは従来型の、つまりチップの横にVR(Voltage Regulator)を配し、そこから基板内部の電源層経由でチップに供給を行う方式の模式図である。

MBVRはMother Board VRの略で、続くIVR(Integrated VR)との対比のためにこう書いたのだろうが、あまり一般的な略ではない。Discrete VRにすればよかったのでは……

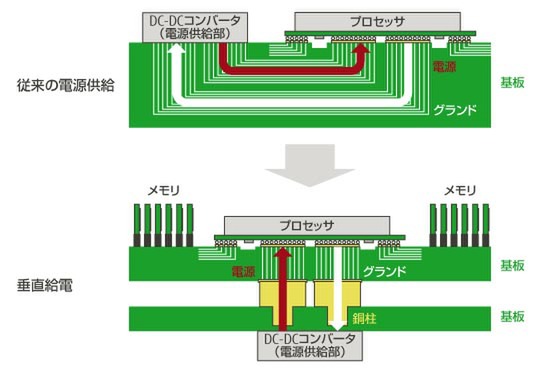

ここでGPUに1KWを供給するには1252Wの供給が必要であり、さらにGPU内部の電圧降下にともなうロスまで含めると、426Wが無駄になる。ところがこれが5KWになるとどうか? というとさらにひどく、MBVRのロスとI2Rロスで3301Wが無駄になり、内部で1528Wのロスが出る。トータルでは4829Wものロスで、入力された8301Wの半分以上が無駄に捨てられてしまう計算になる。

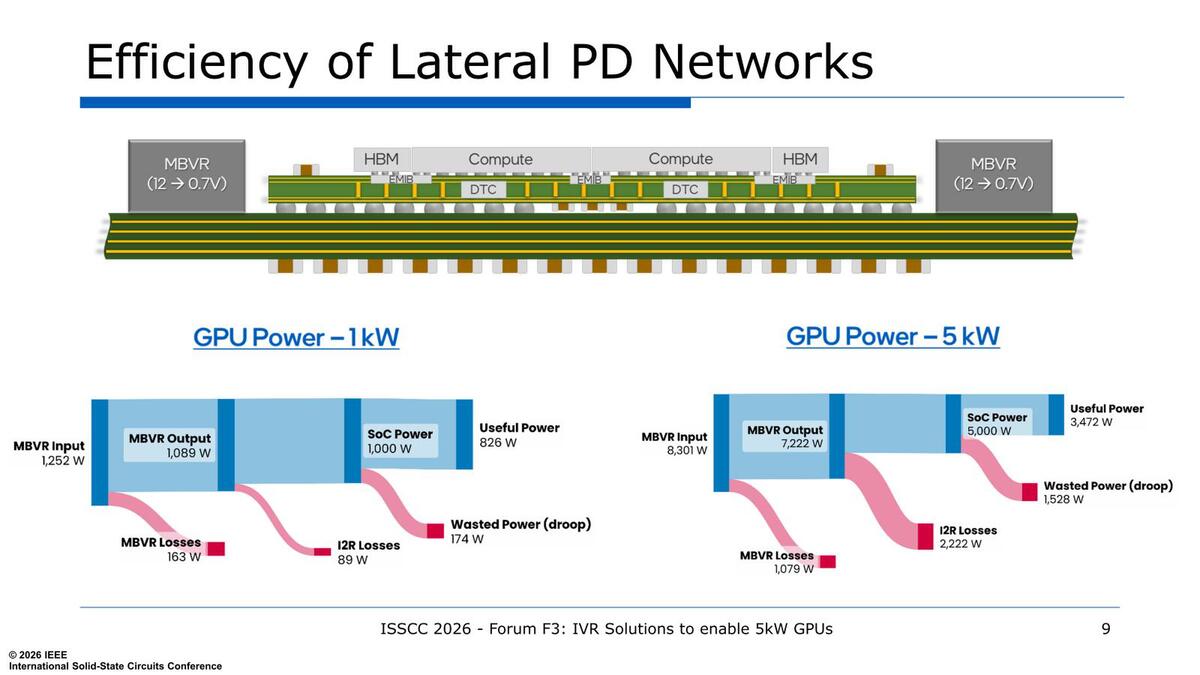

ちなみにI2Rロスというのは配線抵抗にともなう無駄な消費電力のことだ。1kWではそれほど大きくならないが、5kWではI2Rロスが一番大きい。MBVRのロスやチップ内部のロスはそれぞれ個別の対策が必要でパッケージ側ではなにもできないのだが、唯一I2Rロスを削減できる方法として今後導入されるのが確実視されているのがVPD(Vertical Power Delivery)である。

見ての通り、チップの真裏にVRを設置して、そこから基板を垂直に貫通する形で電力を供給することで、電力配線経路を最小限にしてロスを減らそう、という仕組みだ。

実はこの方式、すでに商用での実例がある。富士通が2017年に発表したSPARC M12がそれで、搭載されているプロセッサー(SPARC64 XII)の実装にあたって、VPD(Vertical Power Delivery)方式が採用されたことが富士通により明らかにされている。

もっともこの方式、現実で採用されている事例は非常に少ない。温度・機械的な要因(熱による歪みなど)と基板裏側にそれなりの高さの部品が配されること、それとパスコンを配する場所がなくなることが問題だ。ただ今後はこれらの問題よりも、電力配線を長くする弊害の方が影響が大きい。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります