1ヵ月ほど間が空いてしまったが、ISSCC 2026の解説に戻ろう。今回はForum 3("Powering the Future of AI, HPC, and Chiplet Architectures:From Dies to Package and Rack")の中でインテルが講演した"Integrated Voltage Regulator Solutions to enable 5 kW GPUs"(F3.1)の内容を紹介する。

AIチップのTDPは「4kW超え」の時代へ

電力供給の衝撃的現実

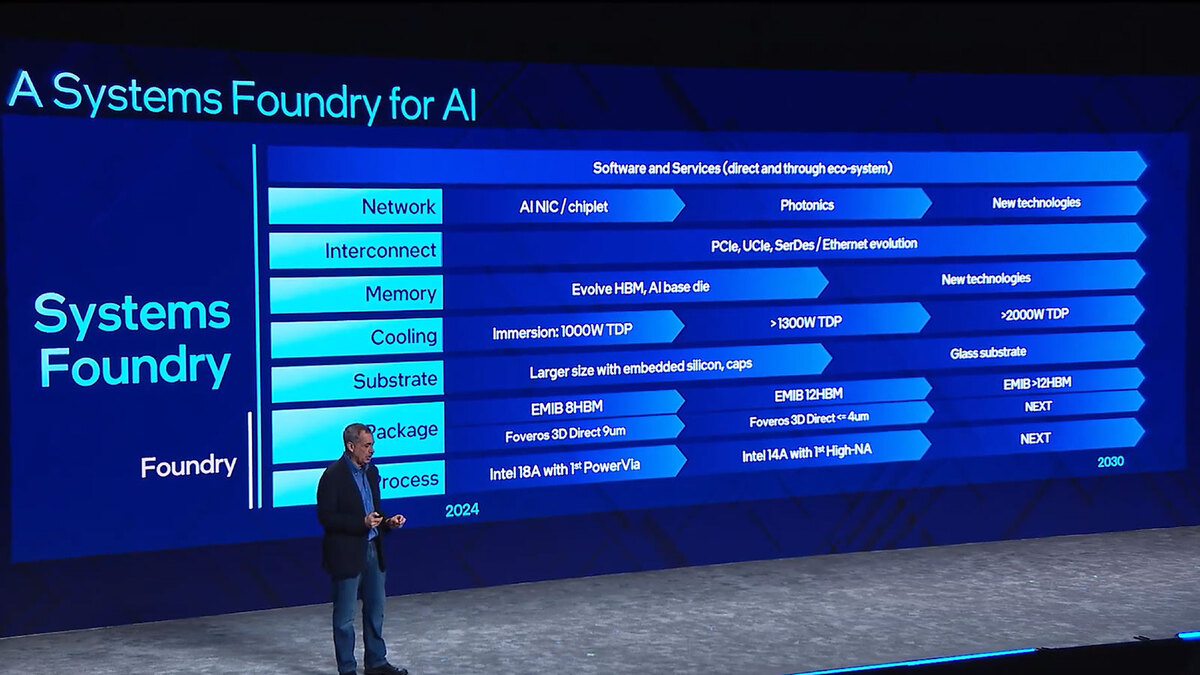

古い話だが、連載761回でIFS Direct Connectを取り上げた。記事の最後で「2030年代のAIチップのTDPが2000Wを超える」という予測があった。

実際にどうなったか? というのが下の画像で、2030年を待たずに2027年の段階で3700Wに達することが確定事項になっている。

ここには示されていないが、2027年に投入予定のInstinct MI500は4kW超えが確実だろう。要するに2024年のIFS Directの推定はまだ甘かったというおそろしい事実が明らかになった。それはそれとして、ではこのバカみたいに大きな電力をどうやって供給するのか、というのがこの講演の主眼である。

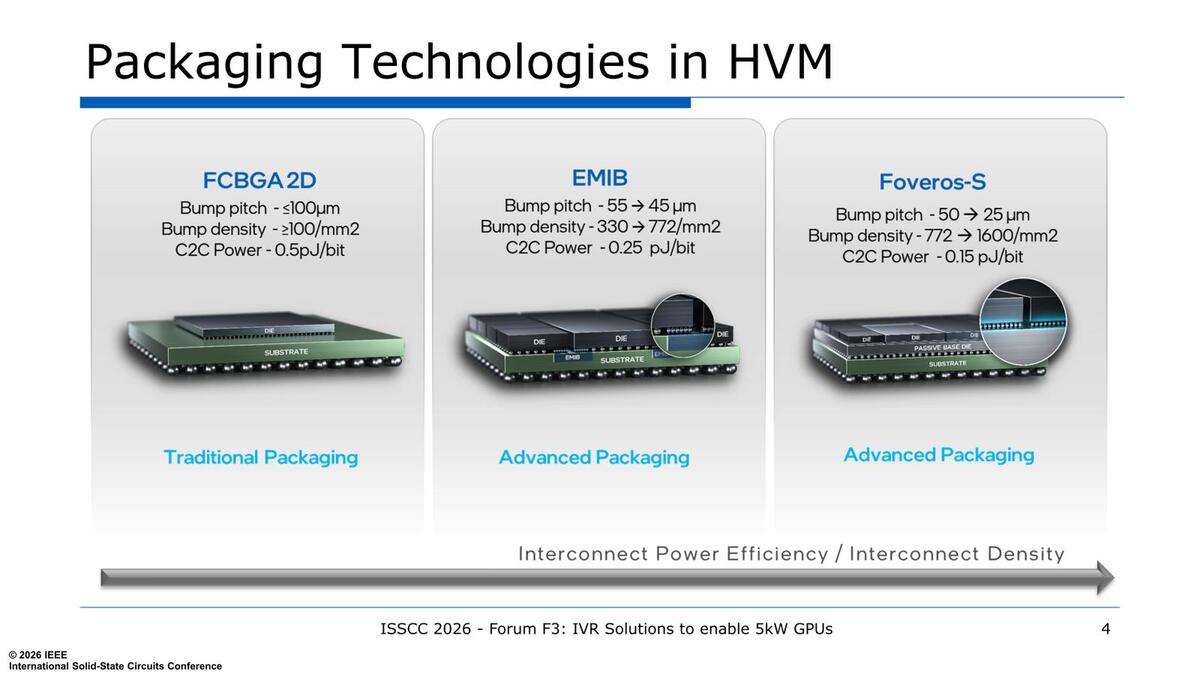

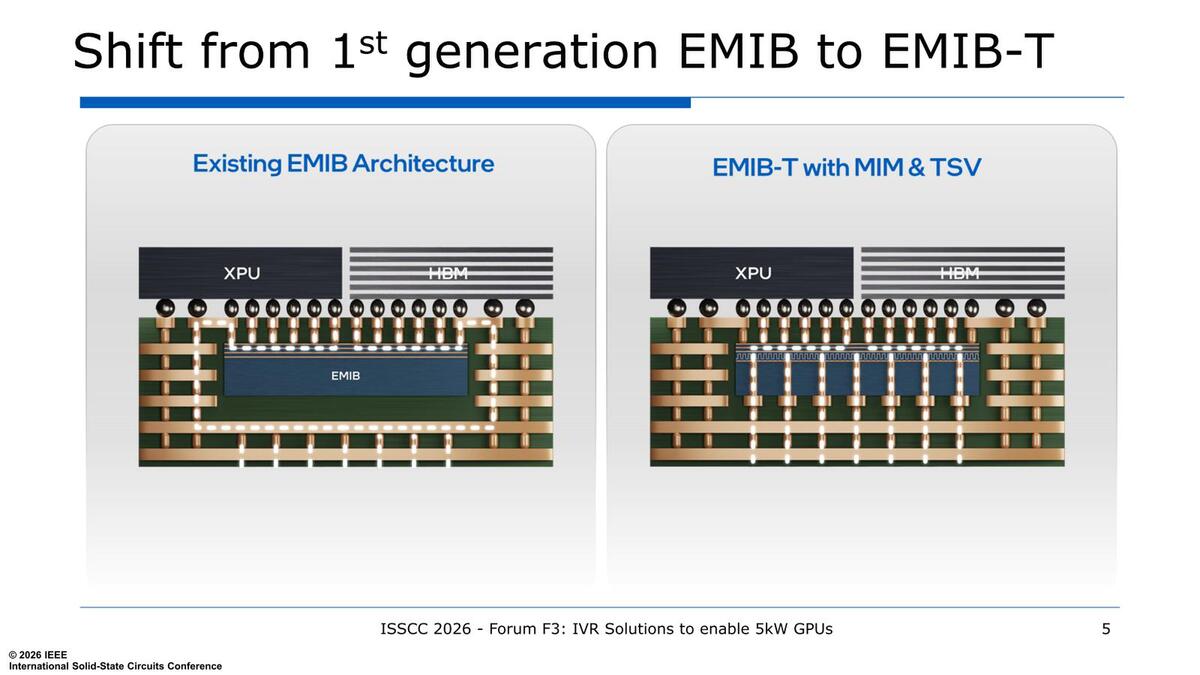

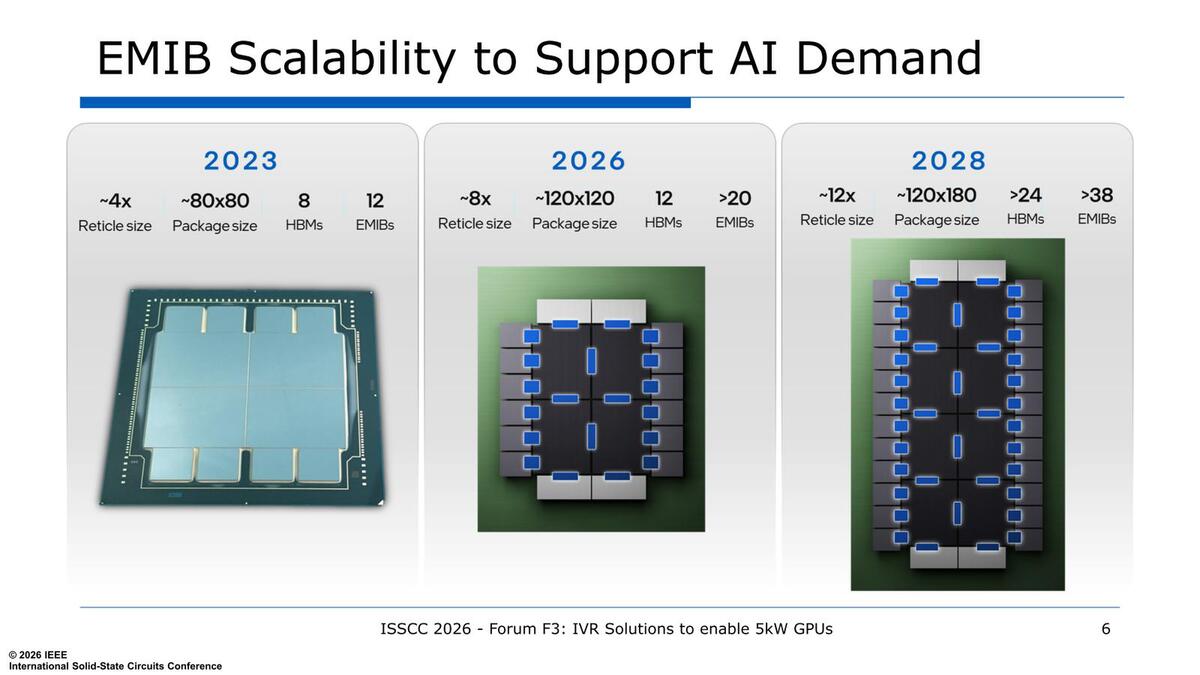

インテルはパッケージ技術としてEMIBおよびFoverosをすでに提供中であり、そのEMIBも、内部にMIM(Metal Insulator Metal)キャパシターやTSVを利用可能なEMIB-Tに進化しているのは連載823回でも説明してきた通り。

そしてこのEMIBを広範に適用することで、大規模なパッケージも構築できるとする。ただEMIBもFoverosも、信号の配線密度や速度の向上にターゲットを置いたものであり、電力供給を考慮したものではない。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります