微細化の壁を突破!

磁性体を利用した次世代インダクター「CoaxMIL」

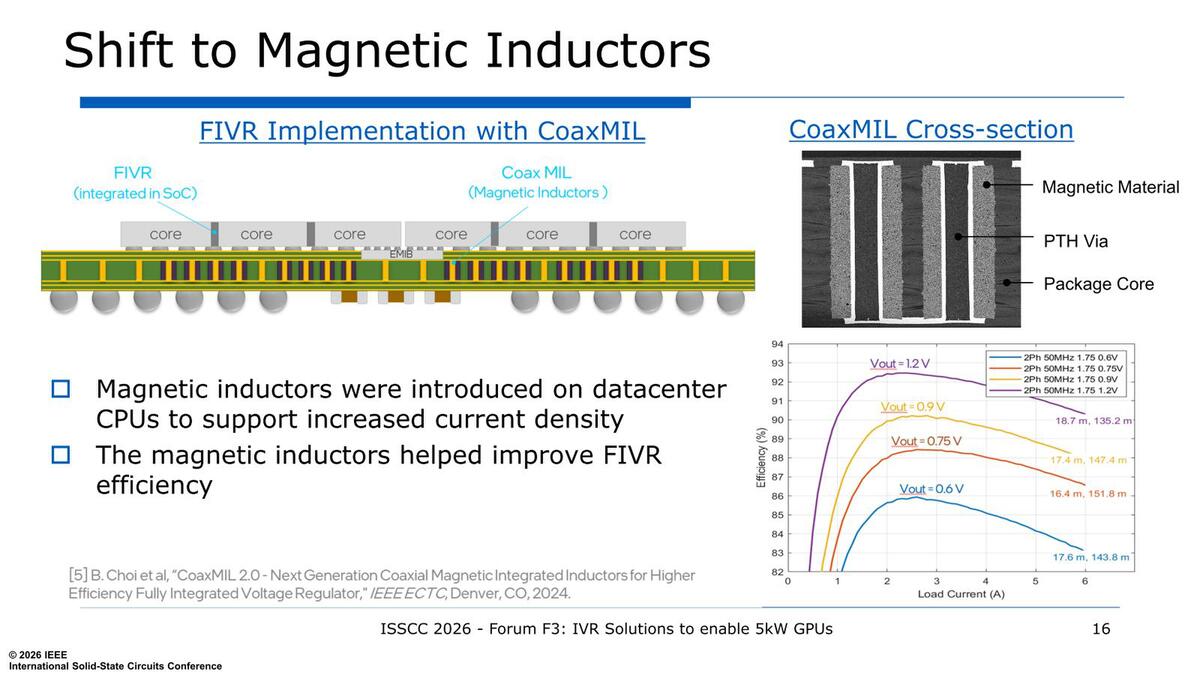

微細化対策としてインテルが導入したのは、コイルの中央に磁性体を埋める方式である。一般に電源周りを見ると、芯(フェライト)の周りに配線を巻いてコイルを形成している。これによりコイルの磁束を強化することでインダクタンスの値を大きくする、というものだ。

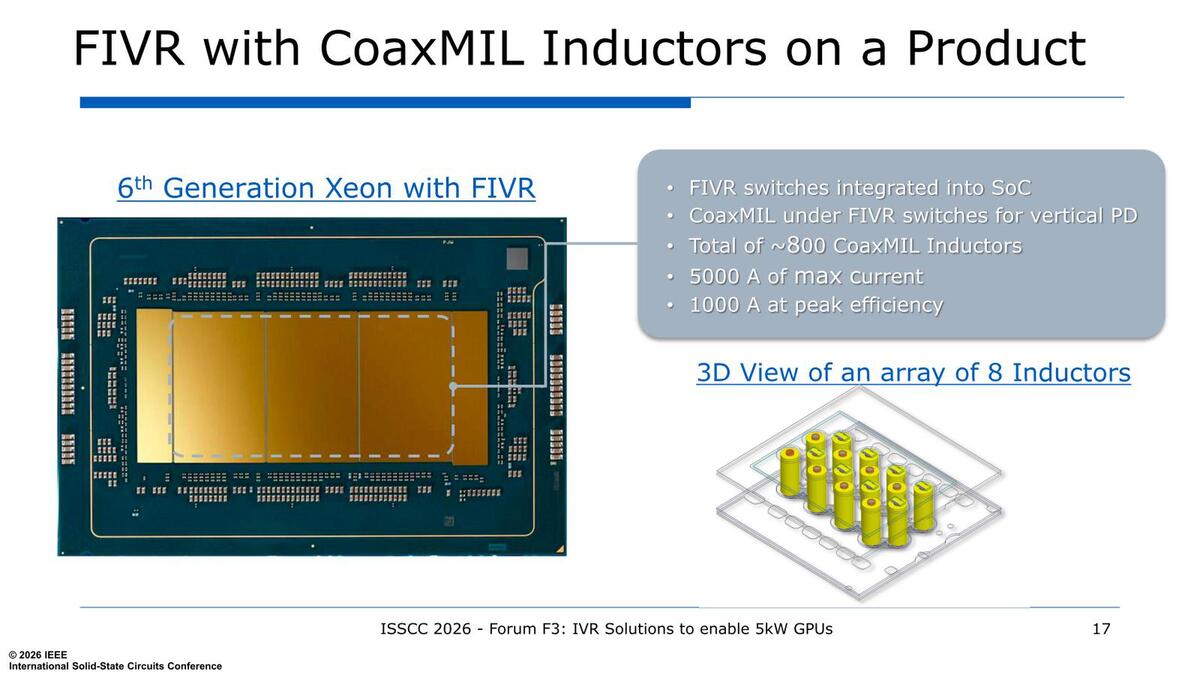

上の画像に出てきた論文"CoaxMIL 2.0 - Next Generation Coaxial Magnetic Integrated Inductors for Higher Efficiency Fully Integrated Voltage Regulator"によれば磁性体の種類そのものは明らかにされていないが、インダクタンス4.8nH、直流抵抗6mΩ、最大電流10A、面積0.5mm2といった数字が示されている。

大きさそのものはかなり小さいが、面積も非常に小さいため、これを複数個使うことで所定のインダクタンスを確保できるわけだ。そして最新のXeon 6のパッケージ基板には、このCoaxMILに基づくインダクタンスが800あまり配されており、最大5000Aの電流供給に耐えられるとしている。

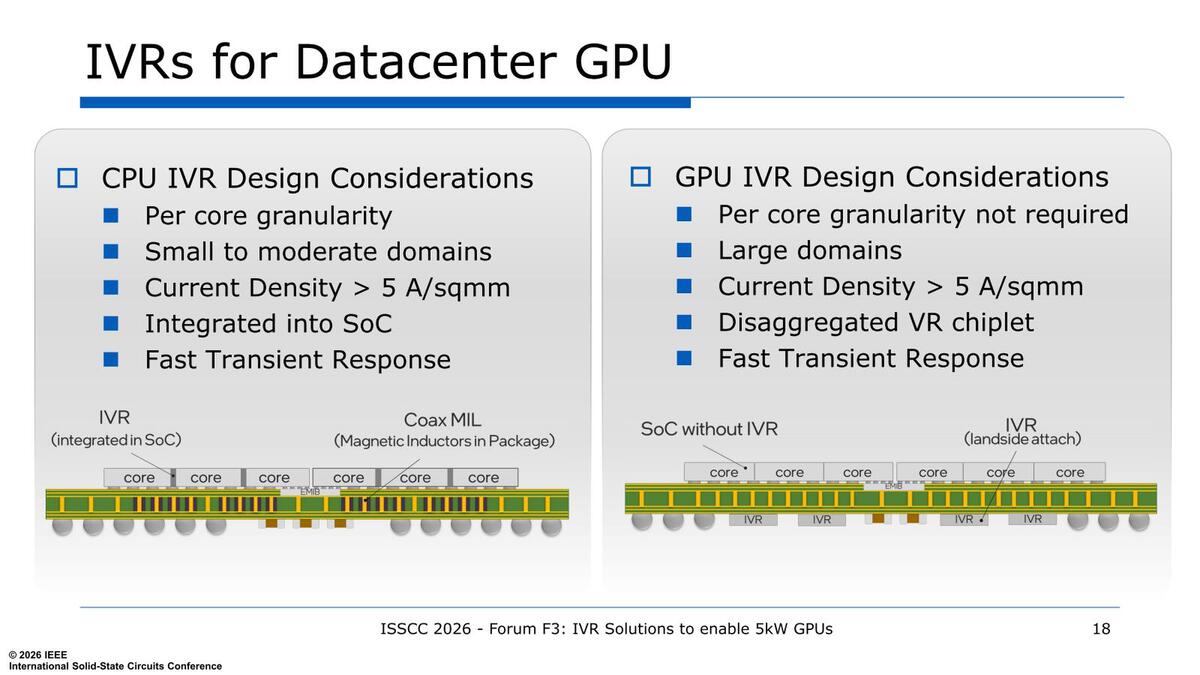

ではFIVRを使えば安心か? というと、GPUはともかくGPUに関しては必ずしもFIVRが最適とは考えていないようだ。

理屈から言えば、例えば100個のFIVRを並べて同時にGPUコアに供給するといった仕組みは取れるのだろうが、今度はそのFIVR同士が正確に連動しないといけないといった問題もあるし、そもそも1Aを供給するFIVRを100個並べるより、100Aを供給するFIVRを1個用意する方が効率はいい。

ただし、100Aを供給するFIVRを作るのが不可能である。そこでGPUではパッケージの裏側にIVRを置き、そこから裏面給電の形でGPUに提供するのが現実的としている。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります