「CU(Compute Unit)」から

「NCU(Next Compute Unit)」へ

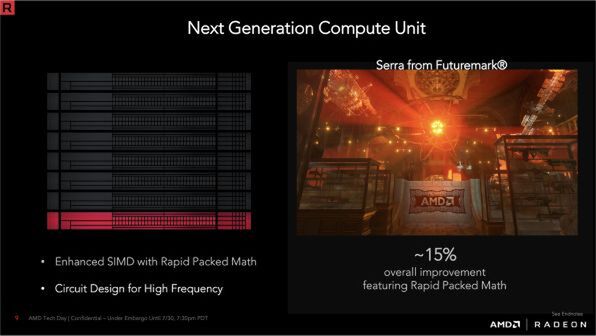

Vegaも系譜的にはGCN世代ではあるが、内部の設計や構造にかなり手が入っている。ストリーミングプロセッサー(SP)16基を4つ束ね、キャッシュなどの回路を付けた「Compute Unit」のスケールでどんな製品になるかが決まる。

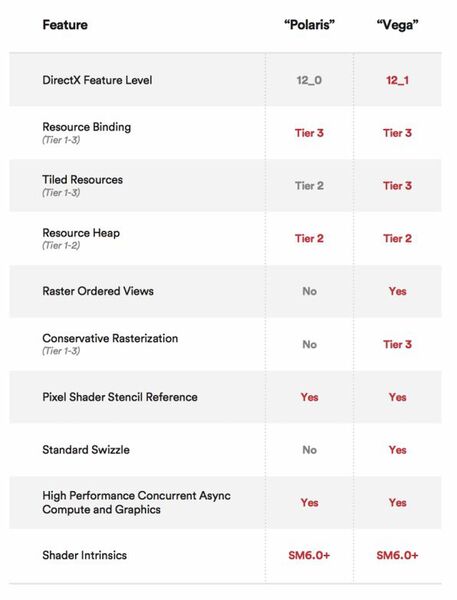

だがVegaは従来のCUを改善した「NCU」を採用することで、従来よりもDirectX12への対応度や16bitのデータの計算処理性能、さらにはパイプライン深度を抑制することで高クロック動作への適応度を高めている。GCNの正統進化系とは言うが、Vegaの進化は従来のGCNよりも皮のムケ方が激しい進化といえるだろう。

HBM2とメインメモリーが合体する

「HBCC(High Bandwidth Cache Controller)」

Vega 56/64はコンシューマー用GPUとしては始めてHBM2メモリーを採用しているが、このメモリーは(AMDによれば)VRAMではなく“広帯域キャッシュ(High Bandwidth Cache)となる。とはいえゲームなどの処理から見れば、VRAMと扱いは変わらないので実質的にVegaのVRAM搭載量は8GBである、といえる。

Fury X世代のHBM1と比べ、メモリーバス幅は半分になったものの、2チップで8GB(Fury Xは4チップで4GB)という大容量なものになっている。しかし、現在のGeForce系ハイエンドでは11GBや12GB搭載されている製品がある点からすると、Vegaの8GBというのはなんとも心細い気もする。

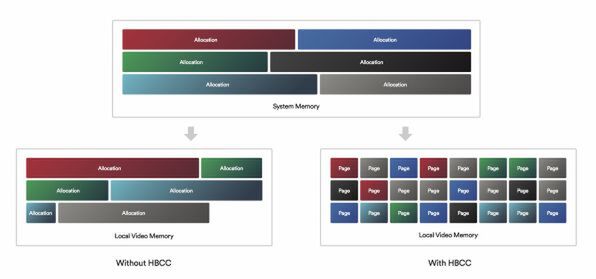

だがここで“広帯域キャッシュ”という言葉が活きてくる。Vegaではシステムのメインメモリーの一部領域をVRAMに組み込めるのだ。多用するデータのみHBM2側に置いておき、不要なデータはマザー側のメインメモリー側に置く。これならVRAM多量使用時に速度のペナルティーを受けにくくなる。

この“どの程度メインメモリーを割り当てるか”については「Radeon設定」内で指定できる。割り当て量を設定してもシステムから見える空きメモリーに変化がないことから、設定を有効にした瞬間メモリー領域が分断されるのではなく、広帯域キャッシュが溢れはじめた段階で確保される設計であると推測できる。

HBCCのメモリー空間は最大512TBまで確保できるので、VegaのVRAM搭載量は“実質無限”といったところだが、現実問題としてゲーミング用途ではよほど厳しい設定をしない限りは8GBを使い切るケースはレアだ。ゲーマーではなくGPUで汎用計算をさせたい人のための機能といってよい。

また、ハードウェア的にはHBM2を制御するコントローラー「HBCC」はZenアーキテクチャーで採用されたInfinity Fablicを用いてGPUコア部分と連結される点も設計的に注目すべき点だろう。HBCCやPCI Express、ディスプレー出力エンジンなどとGPUコアが結びついているが、これを拡張してCPUコアと連結すれば……Zen+Vegaな第8世代APU“Raven Ridge”のできあがりだ。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります