Granite Rapidsのダイサイズは

PHYまで含んでほぼ600平方mm

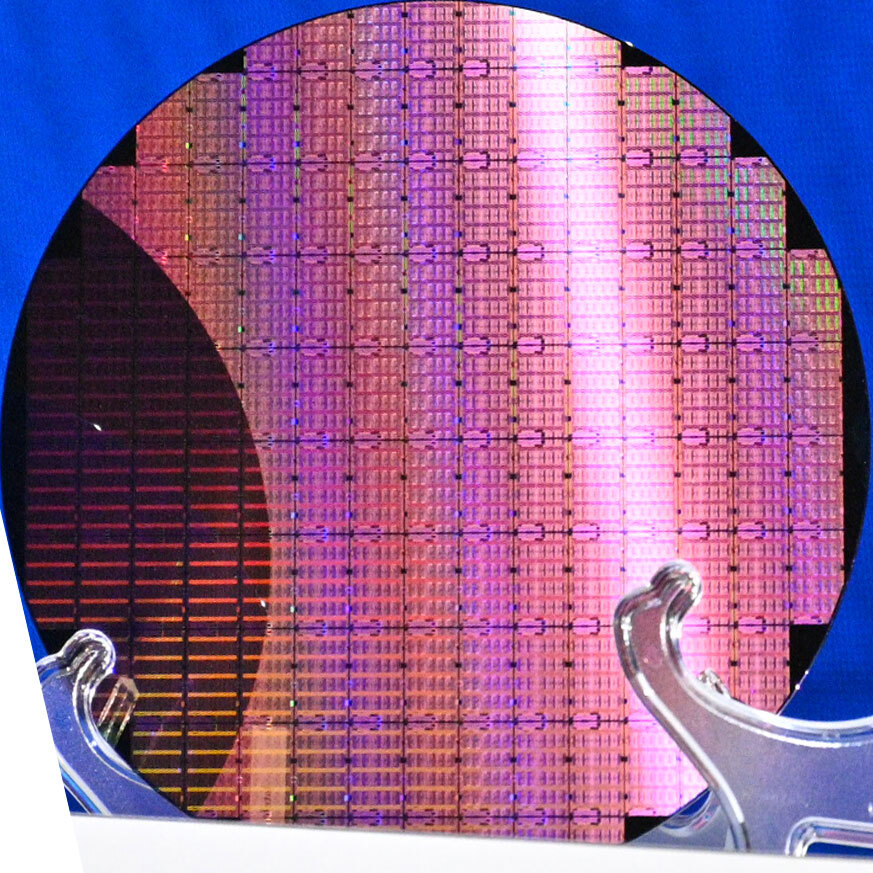

ところで今回の基調講演、壇上には展示されていながら説明されなかったのがGranite Rapidsのウェハーである。

これをむりやり歪み補正したのが下の画像だ。ダイサイズは32.18×18.65mmで599.98mm2なので、ほぼ600mm2となる。

連載736回ではコア部だけで600mm2程度、周辺のPHYも合わせると700mm2を切る程度と想定したが、実際にはPHYまで含んで600mm2以内に収まった格好だ。

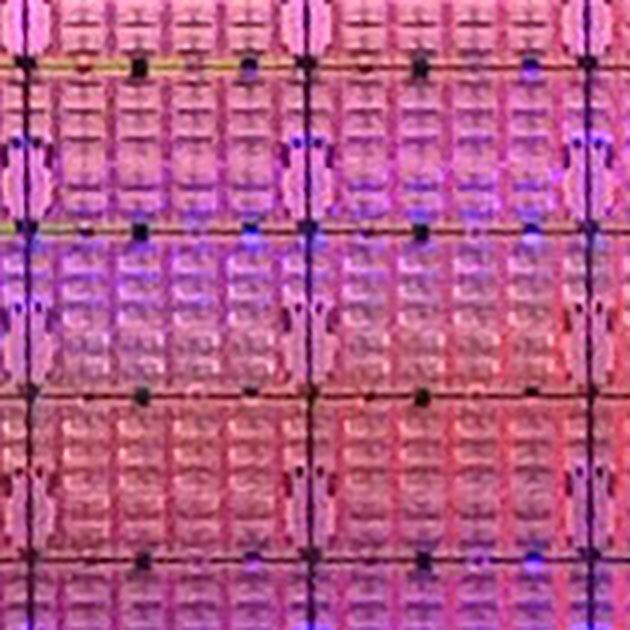

Granite Rapidsのウェハー中央部を切り抜いたのが下の画像で、縦方向に5本、横方向に6本のメッシュが通っているように見える。

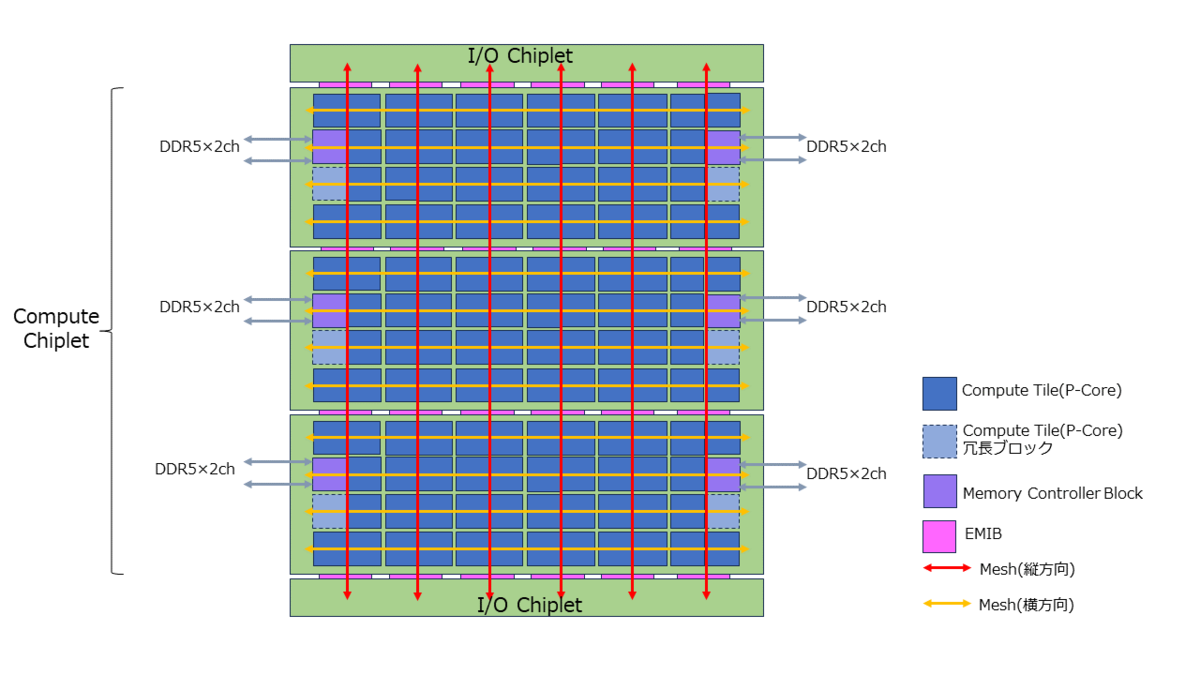

連載736回でGranite Rapidsの内部構造の想像図を掲載したが、その図は間違っていた。

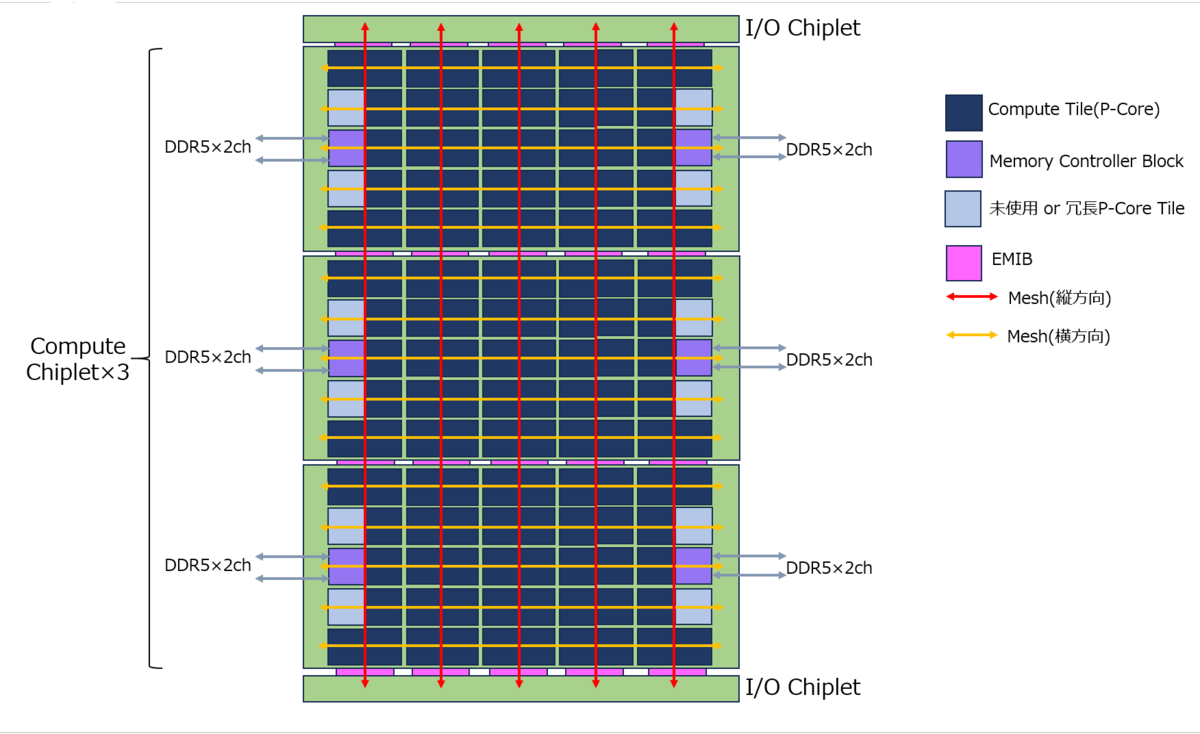

この図ではコンピュート・チップレットあたり縦方向6本、横方向5本のメッシュを想定していたが、実際の構成は下図になると想像する。

ちなみにこれは最大構成の3コンピュート・チップレットの場合で、この下に2コンピュート・チップレットで8ch DDR5の構成や、1コンピュート・チップレットで同じく8ch DDR5(これのみチップレット構成そのものが異なる)が用意されると思われる。

余談だが、そのGranite RapidsとSierra Forest、それとSierra Forestの後継となるClearwater Forestの3つの製品に関しては、正式に新しいBirch Stream Platformを使うことが明確にされた。

Sapphire Rapidsの提供が遅れたことで、Eagle Stream Platformは1年かそこらしか使われないのは少し可哀想である。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります