レイトレーシングにDLSS、RTコアやTensorコアの役割、自動OCテスト機能まで!

Turingコアの構造も謎の指標「RTX-OPS」の計算方法も明らかに!徐々に見えてきたGeForce RTX 20シリーズの全貌

2018年09月14日 22時00分更新

「リアルタイムレイトレーシング」というCG界の“聖杯”を手にすれば、今までの「ラスタライズ法」では困難だった表現も容易に実装できるという。この聖杯にいち早く手をかけたのは、新アーキテクチャー「Turing」をベースにした「GeForce RTX 20シリーズ」を生み出したNVIDIAだ。

8月にドイツはケルンで催されたスペシャルイベント「GeForce Gaming Celebration」にて初めてRTX 20シリーズがお披露目されたが、その直後にプレス関係者向けの説明会「Editor's Day」が設けられ、さらに深いレベルでの話を聞くことができた。

本日(9月14日)情報が解禁されたので、前回の記事「CG界の聖杯「リアルタイムレイトレーシング」に手をかけたGeForce RTX 20シリーズを理解する」【前編】【後編】お伝えできなかったことや後から判明したことを含め、RTX 20シリーズの技術的側面について深掘りしてみたい。

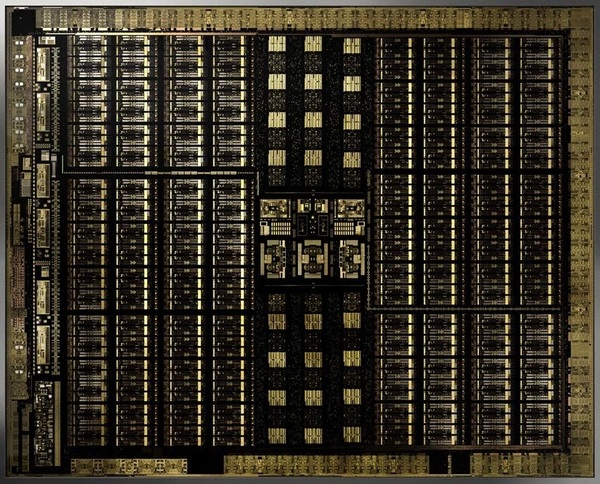

フルスケールな「TU102」コアの構成

まずはTuringコアの構造から眺めていこう。「GeForce RTX 2080 Ti」のコアは「TU102」、「GeForce RTX 2080」が「TU104」、そして「GeForce RTX 2070」は「TU106」と、それぞれ別の設計が用意されている。

Pascal世代であるGTX 1080と1070はどちらも同じGT104から生まれた製品であり、末尾「6」の製品はミドルレンジ向け(この場合はGTX 1060)であったことを考えると、今後GeForce RTX 2060が出るとすれば「TU107」になるのだろうか?

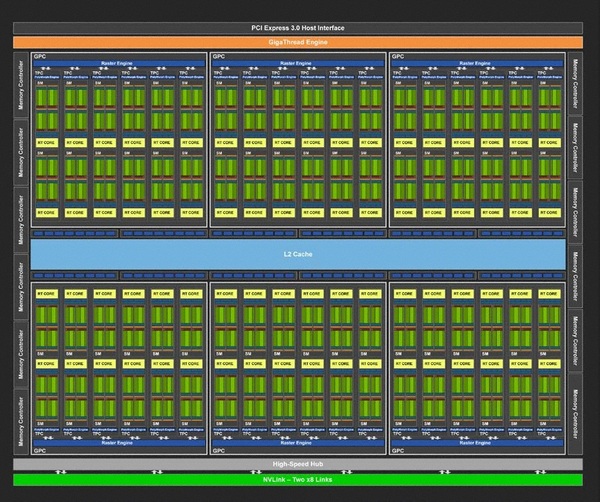

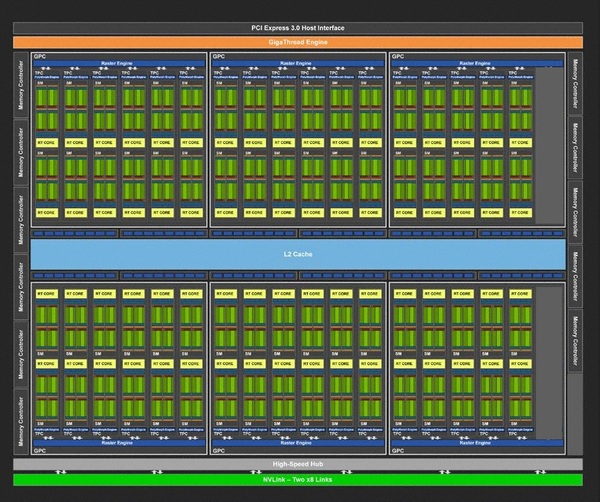

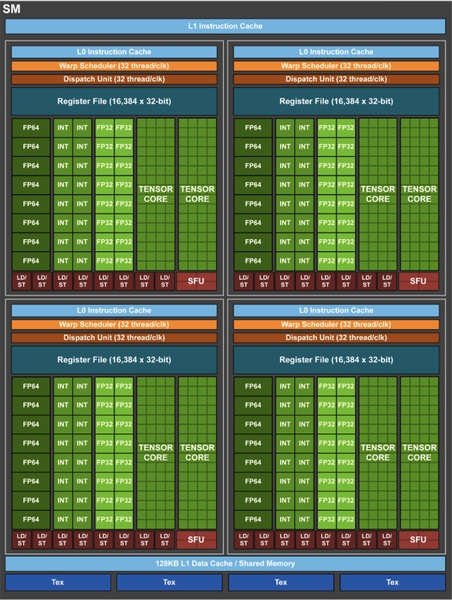

まずは“フルスケール”なTU102のダイアグラムをチェックしてみよう。まず、SM(Streaming Multiprocessor)あたりCUDAコアは64基、Tensorコアは8基、RTコアが1基ずつ配置される。CUDAコア数はPascal世代から半減したが、FP32とINT32用の演算機の2つで1カウントになっていること、Tensorコア8基の存在などから、Voltaの発展形であることが読み取れる。

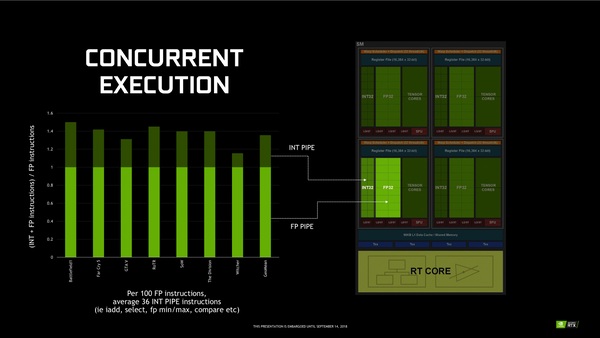

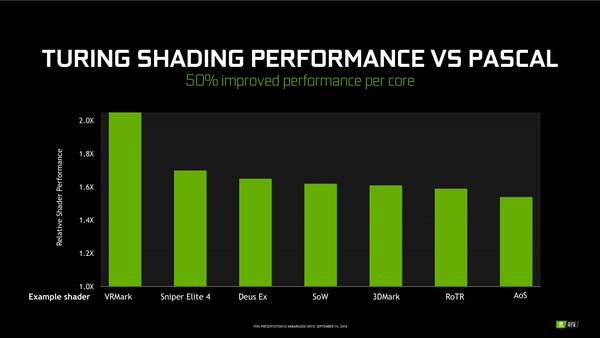

1番大きな改善はFP32とINT32の演算機を分割したことだ。ゲームのシェーダー処理においては、FP32とINT32の処理が混在している。Pascal世代までのアーキテクチャーでは、SM内でINT32の処理を実行している際、アイドル状態のCUDAコアがあってもFP32の処理をさせることはできなかった。

だが、Turing(とVolta)ではFP32とINT32のデータパスを分けることで、両者の処理を並列で捌けるようになる。ゲームによってINT32ラインの使われ方は異なるが、NVIDIAは10~50%のスループット向上を見込めるとしている。

ちなみにVoltaではFP64用のユニットがSMあたり32基搭載されていたが、TuringではSMあたり2基、演算性能にしてFP32の32分の1のスループットになっている。これについて、NVIDIAはFP64を減らしたことで「どんなプログラムでもFP64コードを正しく実行できるようになる」と説明している。

そして、Volta世代とTuring世代の最大の違いは、SM1基ごとにRTX 20シリーズの核心技術、RTコアが搭載されていることだ。このRTコアの役割については後ほど詳しく解説することにしよう。

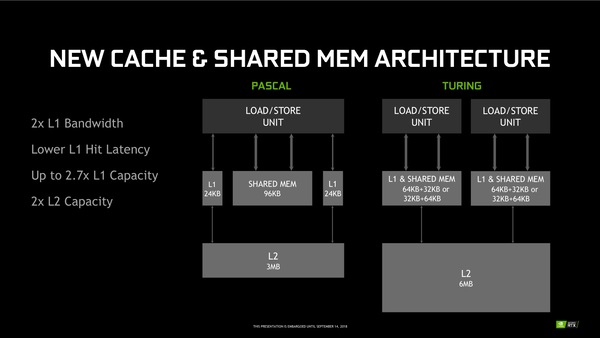

Turing世代ではキャッシュの階層にも大きな手が入った。PascalではSM内にL1キャッシュ48KB、それとは別に96KBの共有メモリー、そしてGPU全体で共有する3MBのL2キャッシュという構造を採用していた。これに対しTuringでは、SM内にL1キャッシュ兼共有メモリーが96KB、そしてGPU全体で共有する6MBのL2キャッシュという構成になった。

この新しい共有メモリーでは、L1キャッシュを最大64KBまで拡大できるので、L1キャッシュへのヒット率が高まる。また、L1キャッシュのレイテンシーを低減、さらにSM内のロード&ストアユニットへの帯域も従来より太くなっている。ゲームエンジンの設計にもよるが、このL1キャッシュの変更はパフォーマンスに大きく寄与する、とNVIDIAは謳っている。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります