第873回

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃

2026年04月27日 12時00分更新

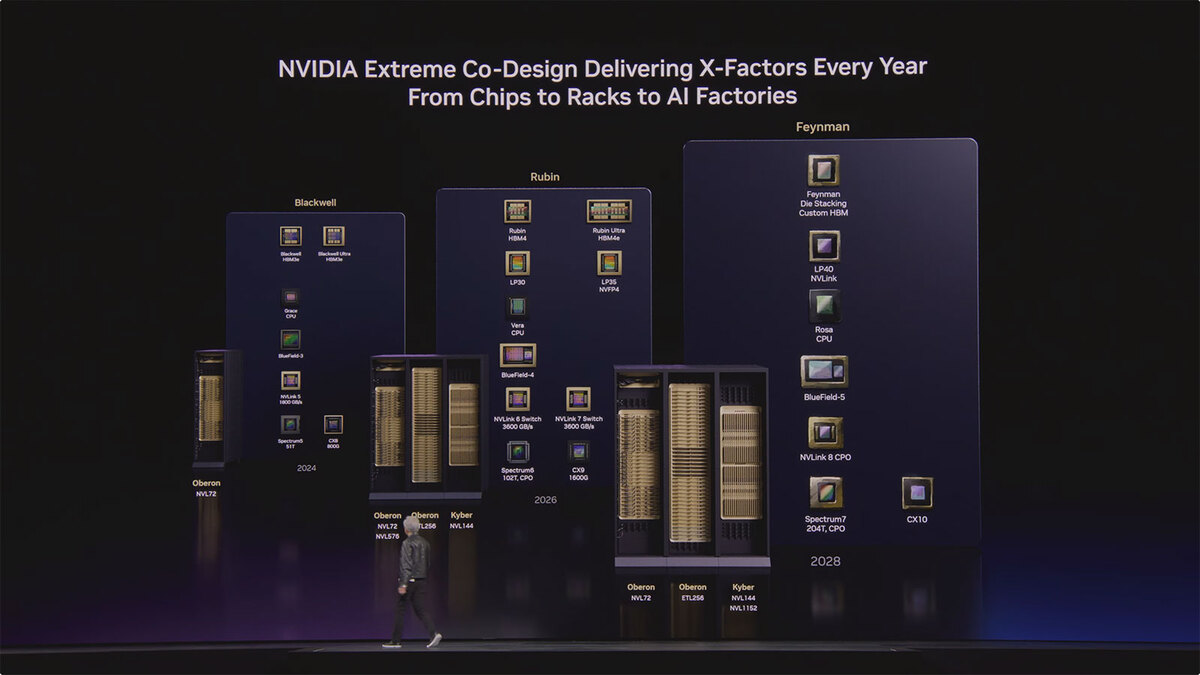

GTC 2026アップデートの3回目となる今回は、2028年のロードマップについて説明しよう。実は基調講演の中で2028年、つまりFeynman世代についてはあまり詳細な説明はなかった。ロードマップとして示されたのが下の画像だ。

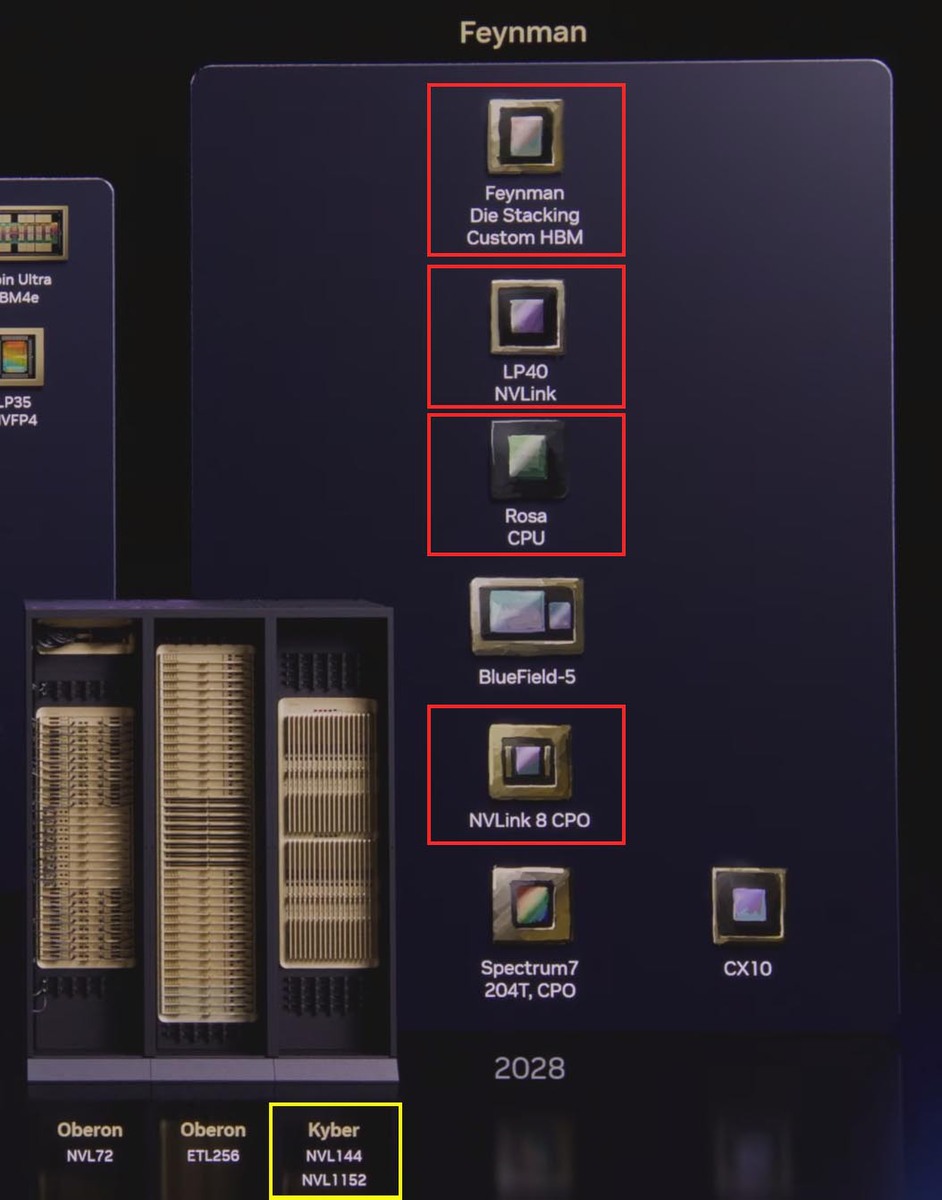

2028年の部分を拡大してみると、以下のことが明らかになった。

- FeynmanはDie StackingとCustom HBMを採用

- LP40がNVLinkを搭載

- CPUがVeraからRosaに更新

- NVLink 8にはCPOが用意される

それに加え、

- KyberベースでNVL1152が投入される

以下これを順に説明していく。

Feynmanの鍵を握る「Die Stacking」と「COPA」構想

まずFeynman。基調講演の中では名称が呼ばれただけで、基調講演の後のQ&Aでも特に言及がなされていない。したがってDie StackingとCustom HBMを使うこと「だけ」が公開情報になる。

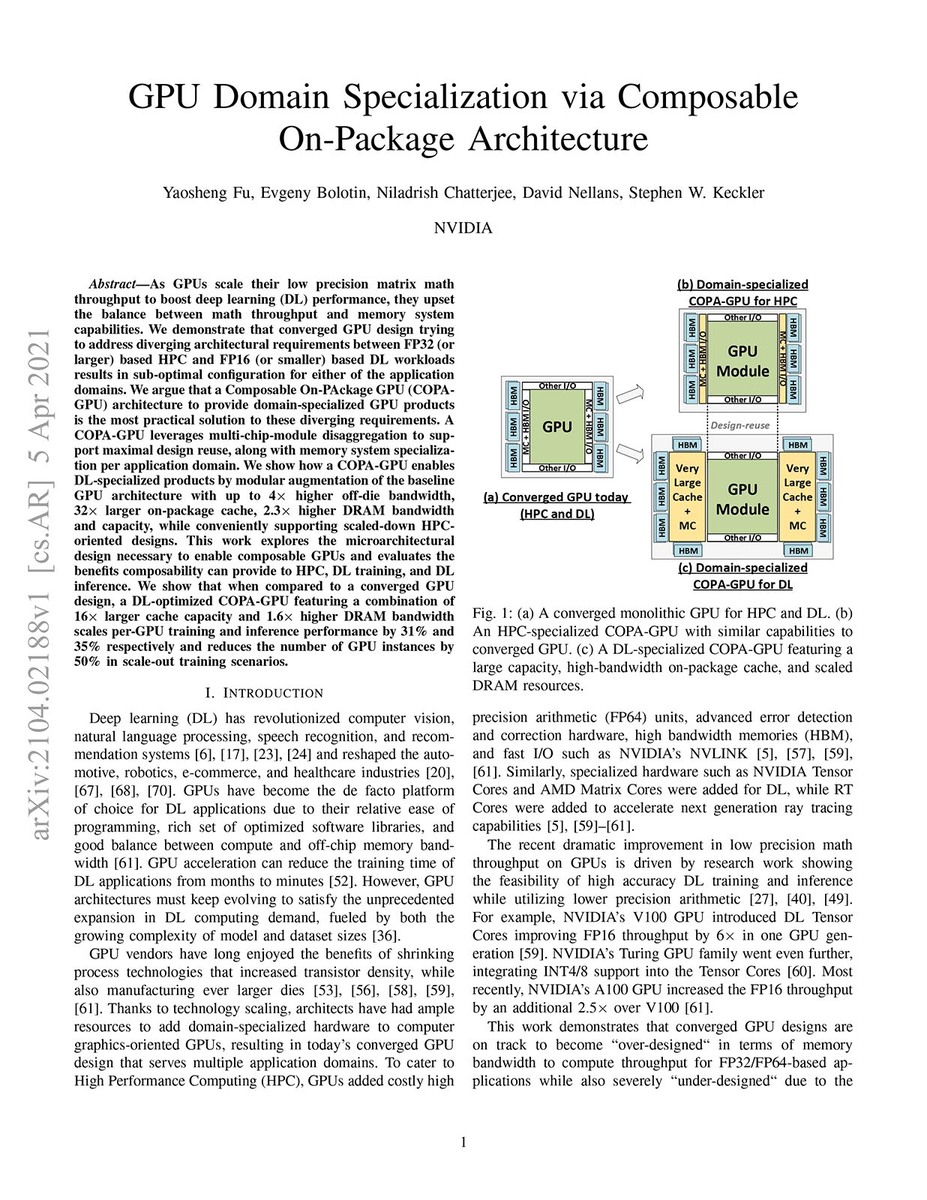

このDie Stackingであるが、これに関してNVIDIAが2021年に発表した"GPU Domain Specialization via Composable On-Package Architecture"という論文がある。

COPA(Composable On-Package Architecture)というのは、従来のGPUの構成をモジュールレベルで分解し、必要に応じて組み合わせを変えることで、用途別(Domain Specific)な製品を構築しよう、というものである。

動機は、HPC向けとAI向けではGPUに対する性能要求が異なるところからスタートする。プロセス微細化にともない演算器を大量に集積できるようになり、特にDeep Learning向けのスループットはどんどん向上している。一方でダイサイズはReticle Limitにより制限され、またメモリー搭載量やメモリー帯域はプロセス微細化の貢献が薄い。結果、今後は演算性能に対してメモリー帯域が決定的に不足するという予測になった。

悪いことに、このメモリー帯域の不足はアプリケーションによって影響が異なる。NVIDIAの分析によれば、Deep Learningの訓練/推論はDRAM帯域がボトルネックになっており、実行時間の28~30%がDRAM帯域の制限に由来すると予測される一方、HPCアプリケーションでは仮に帯域を無限にしても性能は5%ほどしか向上しないという結果が出たという。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります