第790回

AI推論用アクセラレーターを搭載するIBMのTelum II Hot Chips 2024で注目を浴びたオモシロCPU

2024年09月23日 12時00分更新

TelumはAI推論用のアクセラレーターを搭載

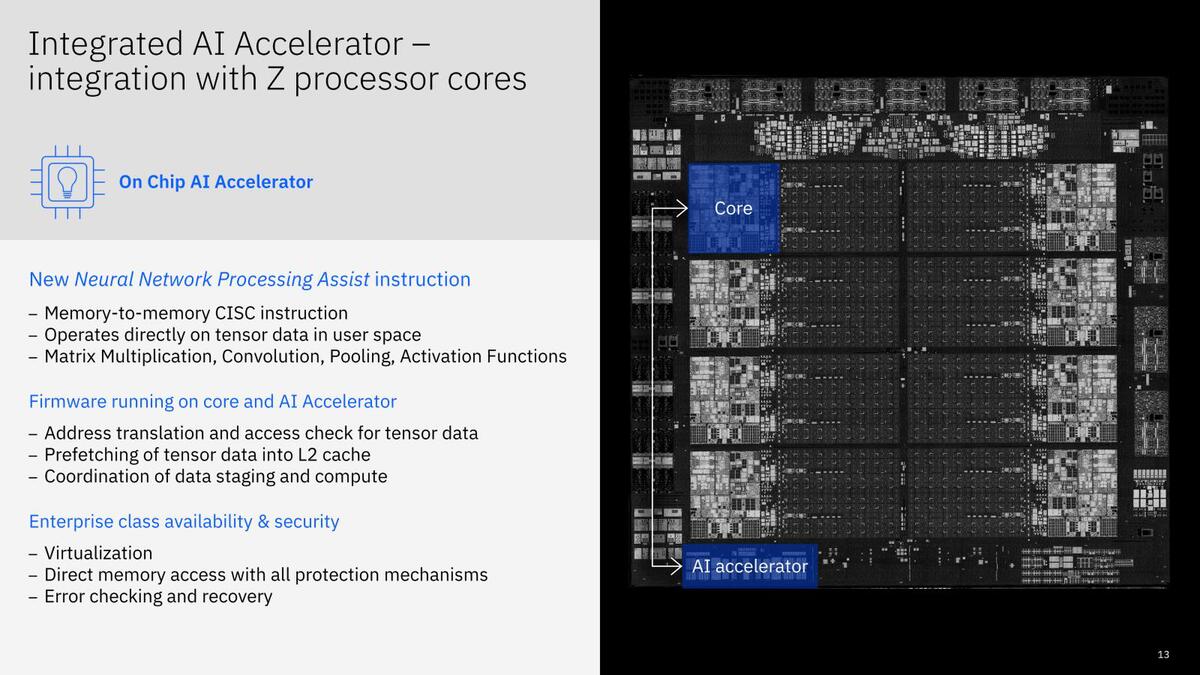

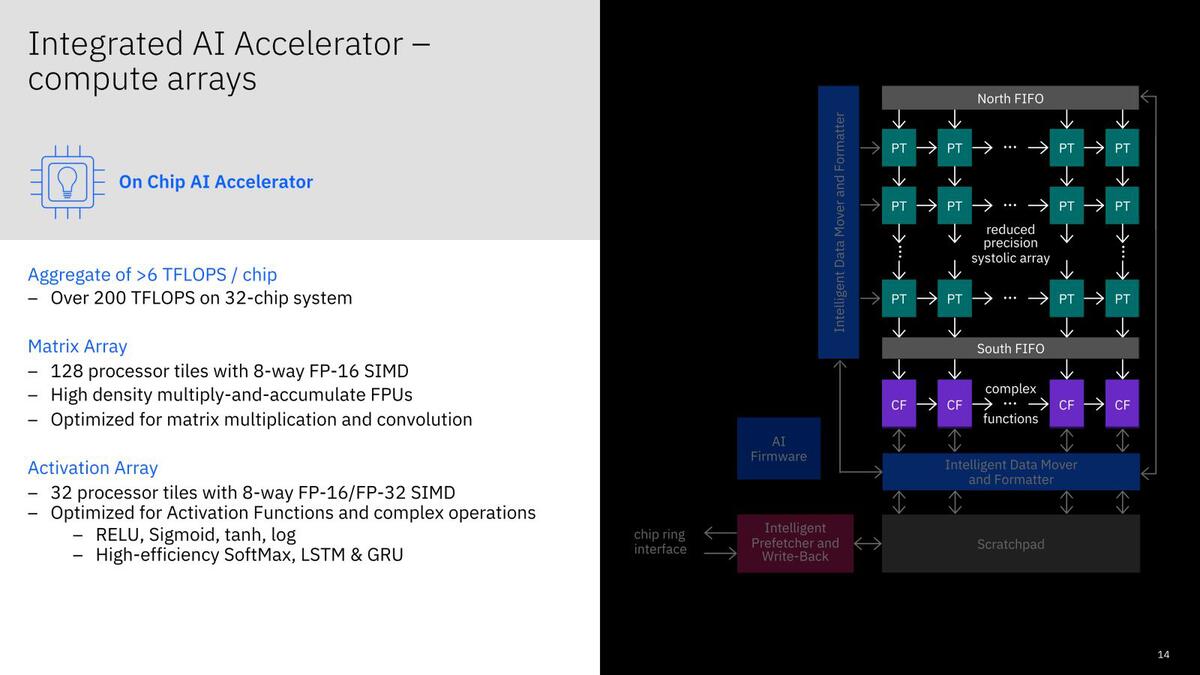

Telumでもう1つ大きな特徴は、AI推論用のアクセラレーターを搭載していることだ。このアクセラレーターはコアとは別の個所に配されており、マトリックス演算や畳み込みなどの演算を直接メモリーから読み込み、その結果もまたメモリーに書き戻す形で実施している。

この推論アクセラレーター、内部は8wayのFP16 SIMDエンジンを持つプロセッサー×128をマトリックス構成にしたものに、アクティベーション専用にFP16/FP32 8way SIMDを持ったプロセッサー×32を用意するという、なかなか強力な代物であり、チップ1個あたりで6TOPSの性能を持つとする。

下の方には推論アクセラレーター用のスクラッチパッドも見える。同時にいくつのネットワークを実行できるかは不明。6TOPSは、2021年当時はともかく現在としてはかなり見劣りする気も。ちなみに200TFlopsというのはドロワー4つでの合計性能である

他にもNXU(Nest Accelerator Unit)と呼ばれる、GZIPの圧縮/伸長用のアクセラレーターやMerge/Sort用のアクセラレーターなど、細かいアクセラレーターがいろいろ搭載されているのも特徴である。IBMの説明によれば、「ソケットあたりの性能を(z15世代比で)40%向上させた」としている。

CPUコアを減らしてDPUを配置したTelum II

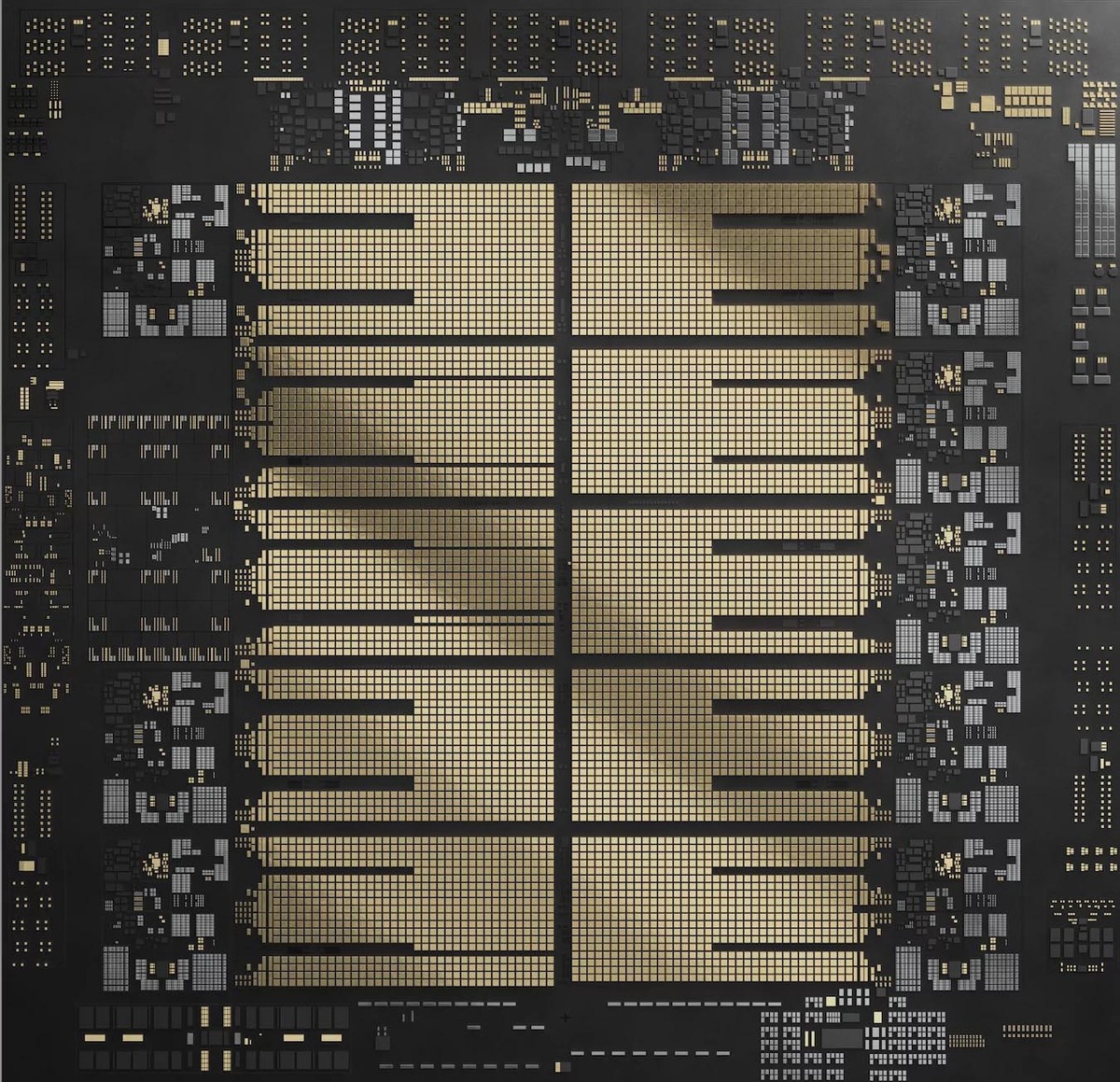

ということでやっとTelum IIである。Telum IIの写真として示されたのはこちらなのだが、これダイではなくパッケージ基板+αのようで、現時点でもダイの写真は示されていない。

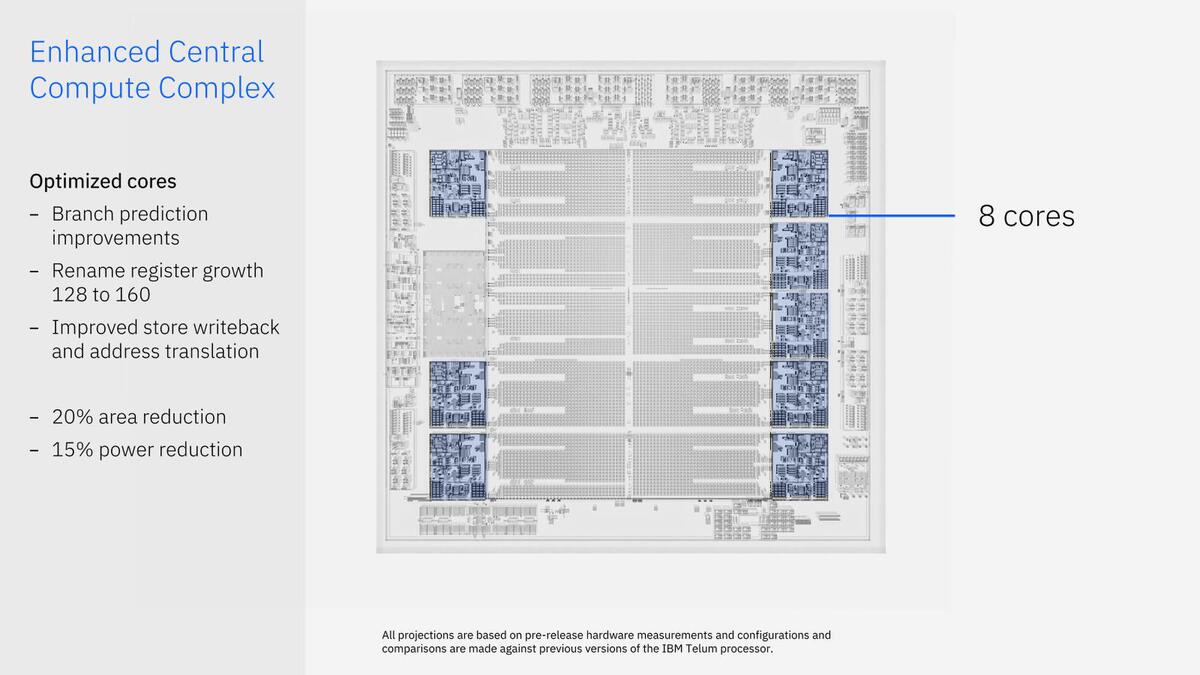

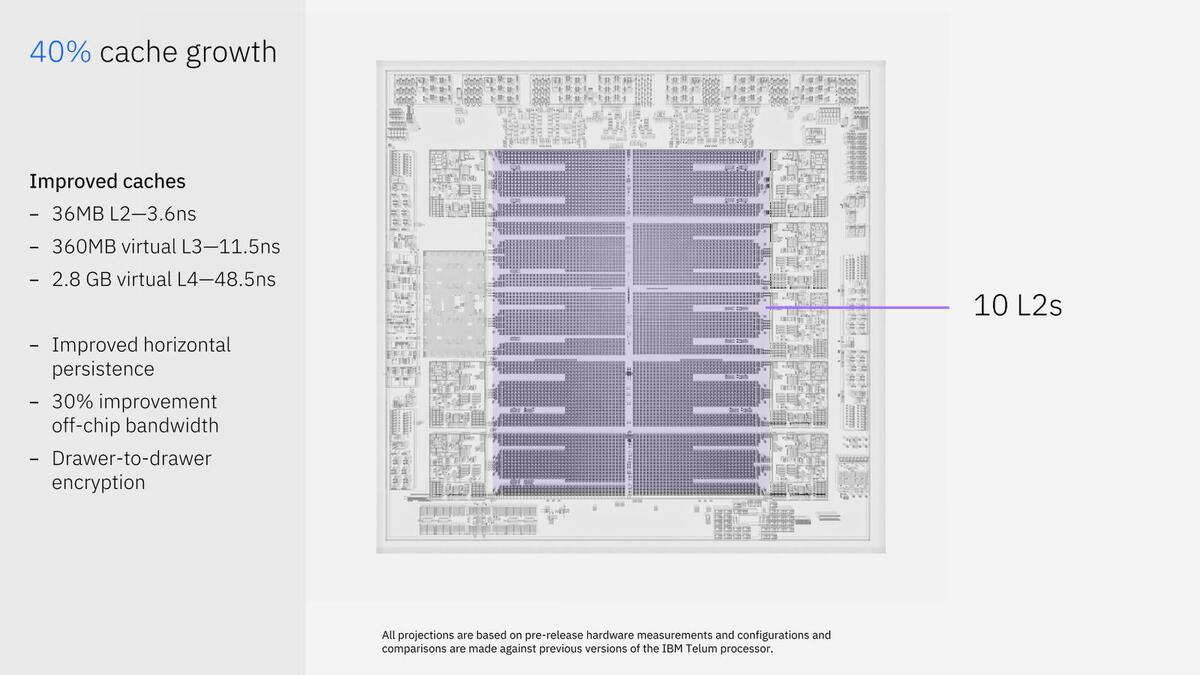

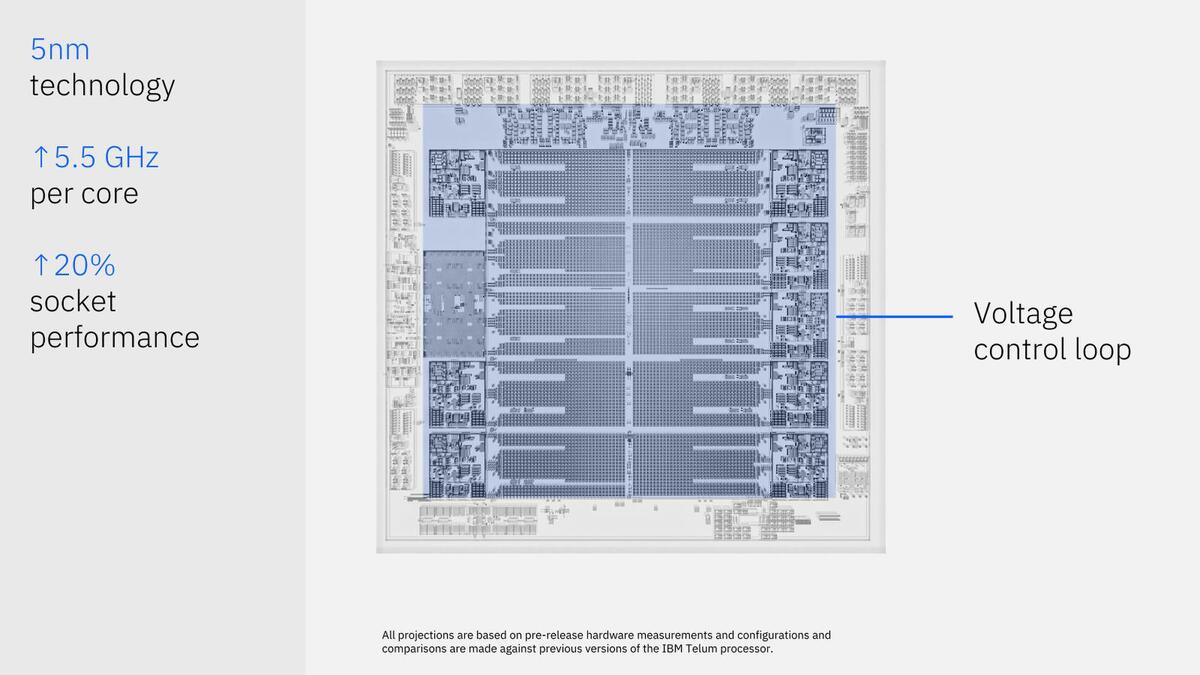

さて、Telum IIはSamsungの5nm(SF5:旧5LPPあたりと目される)を利用して製造されているが、CPUコアは8つに減ってしまった。

Area ReductionとPower Reductionはおそらく7nm→5nmにプロセスを微細化した効果だろう。ただしL2は36MBが10ブロック分が用意され、合計360MBとなっている。ややL2というサイズではなくなっている気がするが。

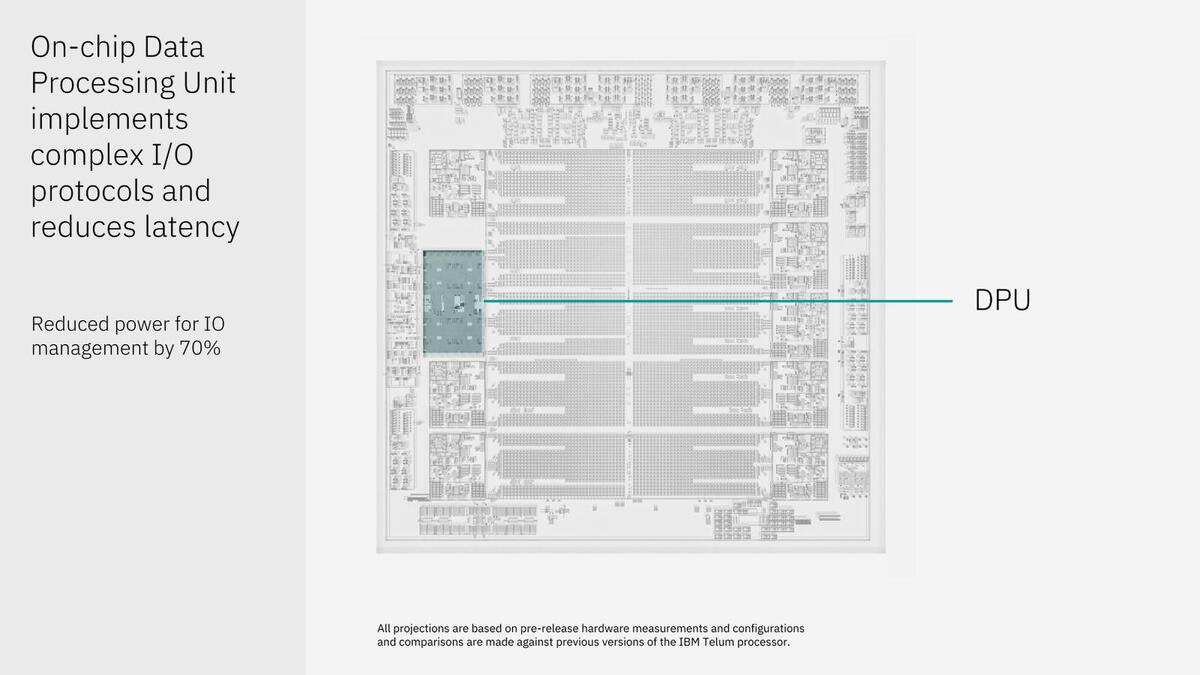

CPUコアを2つ減らしたところに収まるのがDPU(Data Processing Unit)である。これはインテルのMount Evansのように、I/Oの処理をオフロードするもので、これによりI/Oの制御に要する消費電力が70%削減できたとする。

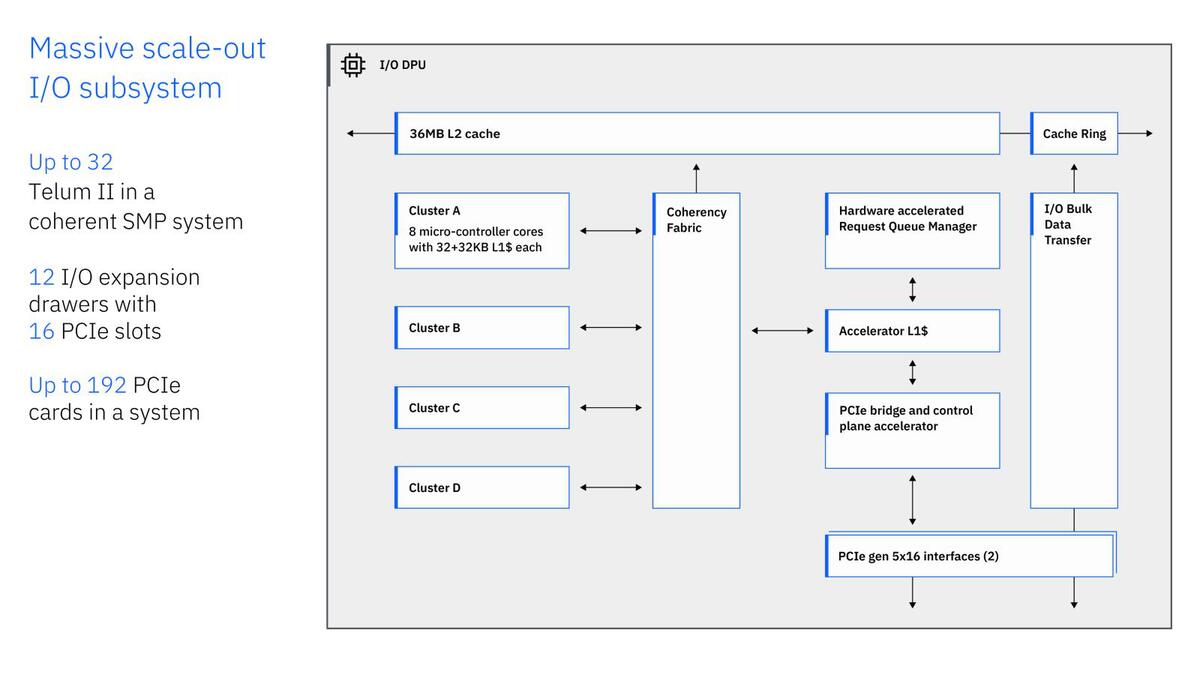

そのDPUの中身が下の画像だ。Cluster A~Dの4つのMCUコアクラスターがあり、おのおの8つのMCUが動作して、これがI/Oの処理を担っているようだ。ちなみにMCUとは言うが、中身は不明である。

さすがに今さらPowerPC 430などを使っているとは思えないので、Cortex-M7クラスのものだろうか? I/O周りの処理結果は、そのまま隣接するL2キャッシュに収められ、その内容はCPUコアからVirtual L3の先に格納されているものとして扱われる格好だろう。チップ1個あたり12個のPCIe Gen5 x16レーンが出るのも、このクラスのCPUとしてはかなりのものだ。

ちなみにCPUコアとL2、それとDPUに関しては、Voltage Control Loopの制御下に置かれており、このControl Loopの制御を有効にすることで最大18%の消費電力削減が実現したという。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります