第789回

切り捨てられた部門が再始動して作り上げたAmpereOne Hot Chips 2024で注目を浴びたオモシロCPU

2024年09月16日 12時00分更新

AMDのGenoaよりも性能消費電力比が30%以上高い

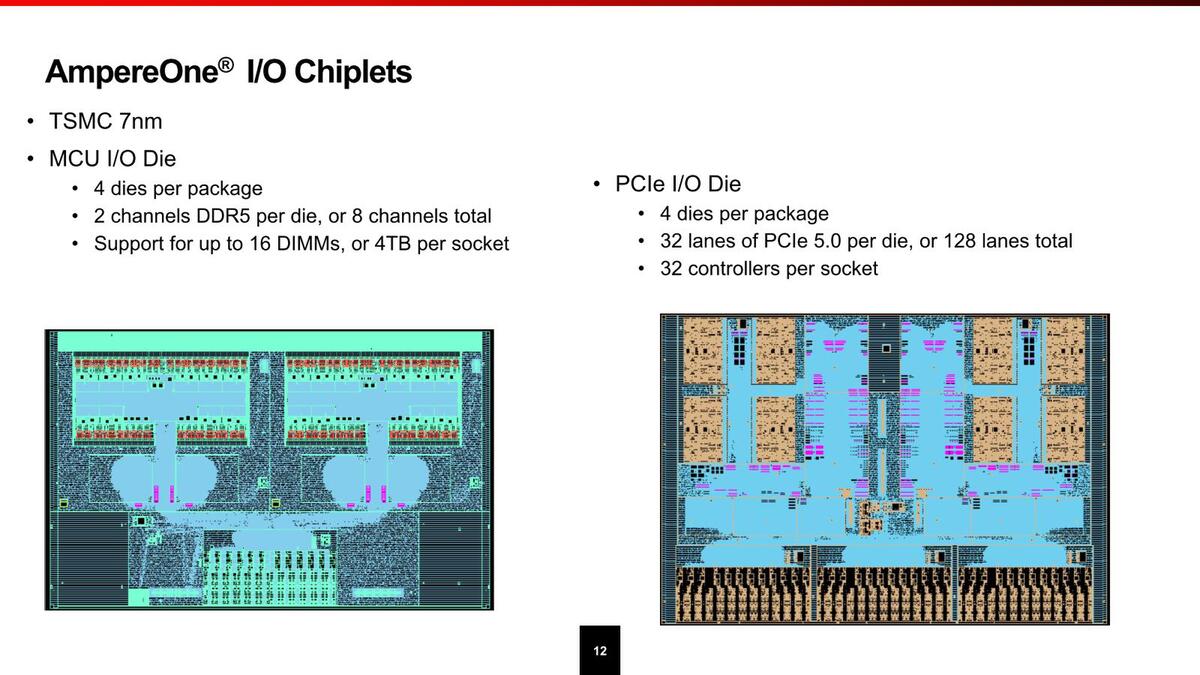

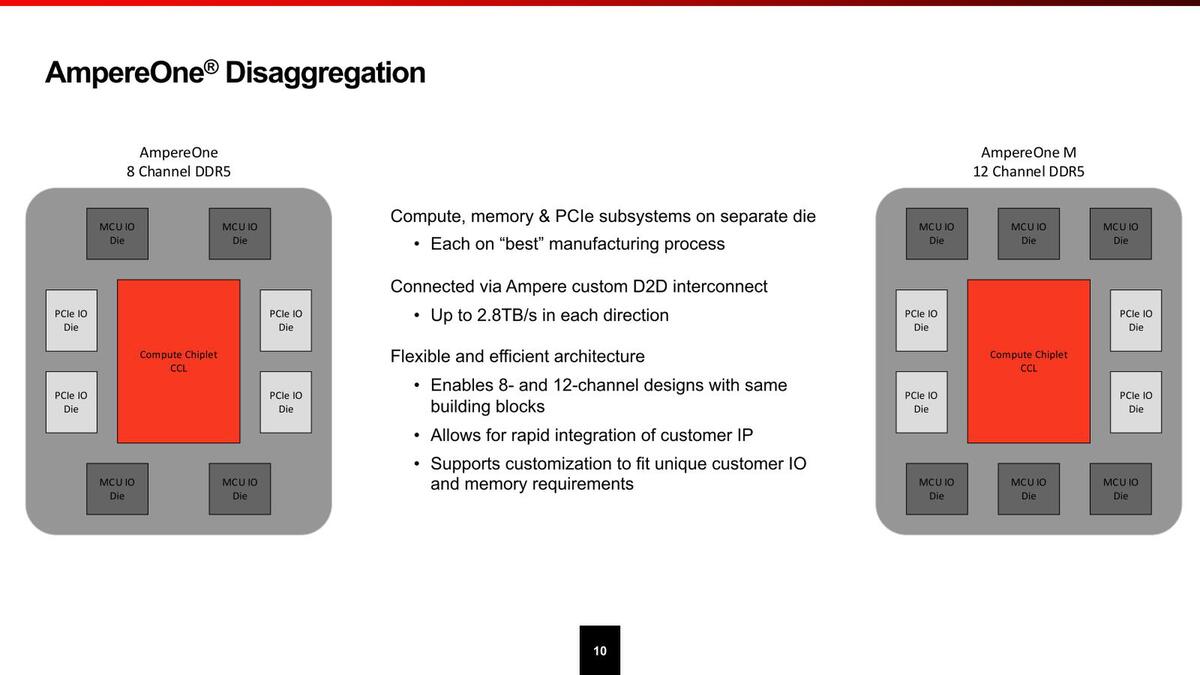

そんなAmpereOneであるが、同社初のチップレット構成である。メモリーコントローラーおよびPCIeは外付けのチップレットの構成となる。したがって、8ch DDR5のAmpereOneと12ch DDR5のAmpereOne Mは、同じダイであり単にメモリーコントローラーの搭載数が異なるという形になる。

8ch DDR5のAmpereOneと12ch DDR5のAmpereOne Mは、メモリーコントローラーの搭載数が異なる。"Same building block"とはあるが、パッケージが共通かどうかは不明。現実問題としては8ch版のAmpereOneと12chのAmpereOne Mではパッケージが異なるように思えるが、さてどうだろう?

このチップレット同士の接続は、同社独自のインターコネクトを使っているという説明である。最大2.8TB/秒とあるが、これは全チップレットを接続した場合の数字であり、おそらくチップレット1個当たりは180GB/秒程度。16bit幅とすれば信号速度は11.2GT/秒程度と考えられる。あるいは32bit幅で5.6GT/秒かもしれないが、それだと配線が大変そうだ。

AmpereOneのドキュメントを読んでもDDR5とだけしか書かれていないが、8chで16DIMMが最大構成ということから1chあたり2DIMMになるので、すると速度としてはDDR5-4400のRegistered DIMMと考えられる。ということは1chあたり35.2GB/秒、2chでも70GB/秒少々なので、180GB/秒の帯域があれば十分だろう。仮に1DIMM/チャンネルに制限してDDR5-6400を使ったとしてもチャンネルあたり51.2GB/秒、2chで102.4GB/秒に過ぎないからだ。

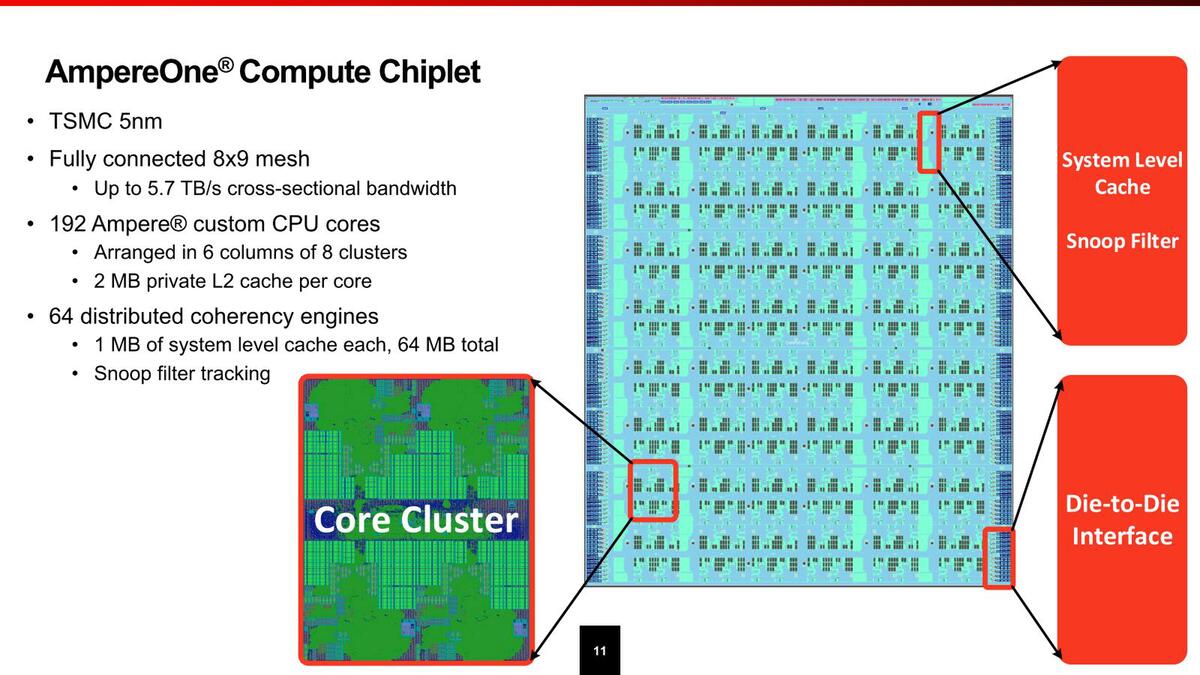

コンピュート・チップレットの構造が下の画像で、4つのCPUコアで1つのクラスターを構成し、このクラスターを6×8で48個搭載し、合計192コアという形だ。

チップレットへの接続用のPHYは16グループ用意されており、当初からAmpereOne Mの構成を想定に入れていることがわかる。このコンピュート・チップレットはTSMC N5だが、I/Oチップレットの方はTSMC N7であると発表されている。

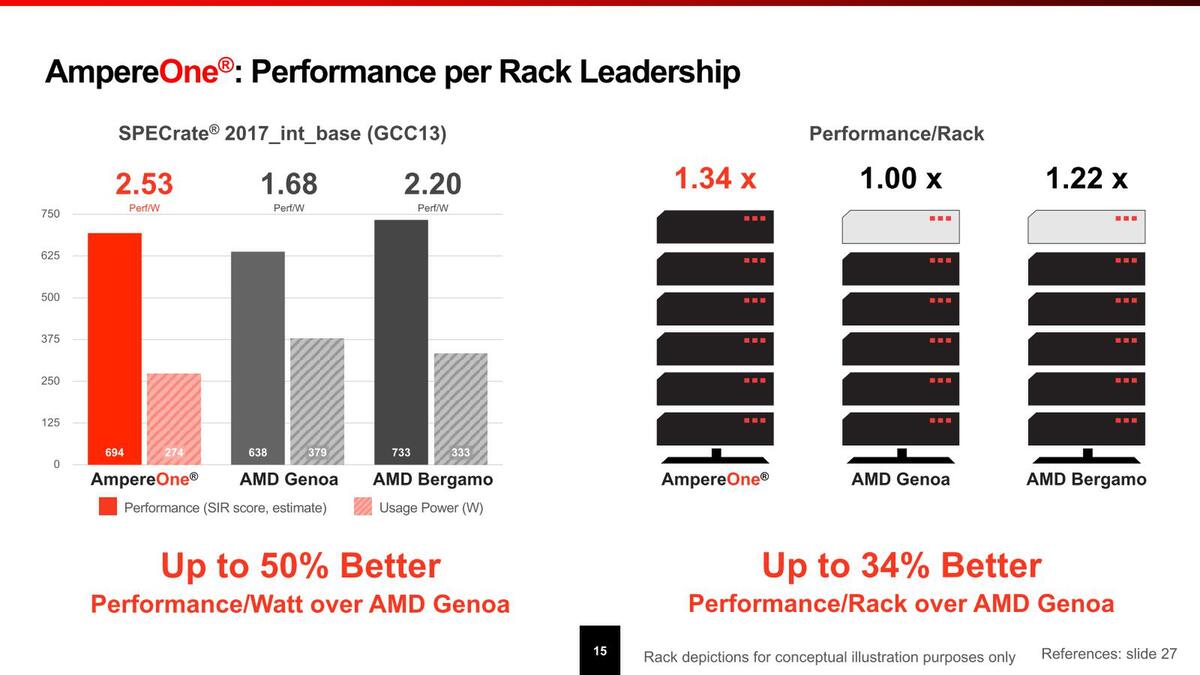

性能としては、SPEC CPUの結果はAMDのGenoa/Bergamoと比較して、Genoa比で最大50%、Bergamo比でも15%性能消費電力比が向上したとしており、ラック当たりの性能で言えば34%高いとしているが、性格からすればGenoaよりもBergamoとの比較が正しいと思われ、この場合は10%程度の向上に過ぎない。

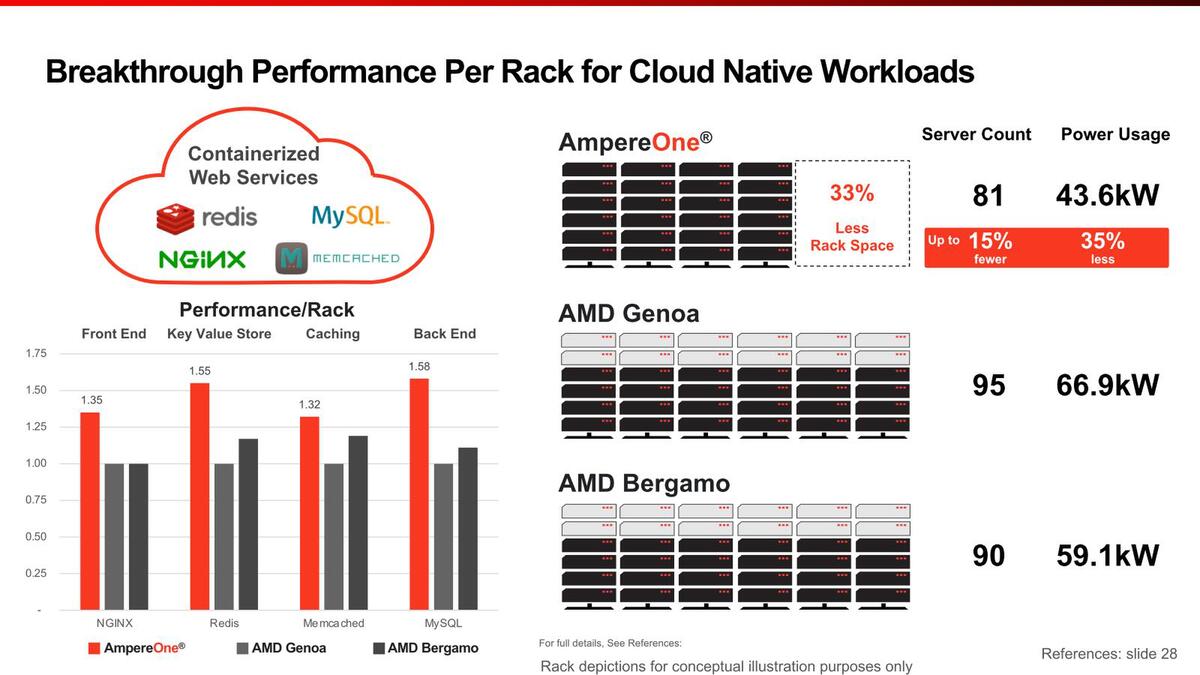

またクラウド・ワークロードに関してもGenoaと比較して性能消費電力比が32~58%向上、より少ないラック数/消費電力で同等の処理が可能としている。

先ほども書いたが、現状Armベースでユーザーが購入できるサーバー向けプロセッサーは意外と少なく、それもあってAmpere Alter/AlterMAXが多く利用されていたわけだが、こうした市場向けにより高い性能消費電力比のプロセッサーを導入するという同社の目論見に対応した最初の製品が無事出荷開始されているのはとりあえずは喜ばしい。

Genoa/Bergamoには勝ててもTurinにはどうか? Sierra Forestとはどうだろう? などいろいろ疑問はあるが、そのあたりのデータも今後出てくるかもしれない。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります