9月19日・20日にIntel Innovation 2023が開催され、初日の基調講演でPat Gelsinger CEOによりいろいろな情報が公開された。のっけから前回の情報の訂正からスタートしたい。

Sierra Forestはソケットあたり288コアだった

今年3月に開催されたDCAI Investor Webinarにおけるスライドでは、Sierra Forestは144コアという話であった。そしてHot Chipsにおける説明でも、1つのタイルに144コア(2ソケットで288コア)という説明がなされていた。

それもあって、前回の説明では、1つのコンピュート・チップレット+2つのI/O チップレットという構造が一番妥当に見える(そしてそのコンピュート・チップレットは8×5ブロックの可能性が高い)と説明をしたわけだが、いきなりこの前提がひっくり返された。

基調講演ではSierra Forestが2コンピュート・タイル構造で、しかもソケットあたり288コアであることが紹介された。つまりタイルあたり144コアなのは間違いないが、それが2タイルあるわけだ。

しかもSierra Forestは12chのDDR5を利用可能と説明された。つまりタイルあたり6chのDDR5のコントローラーを持つ計算になる。

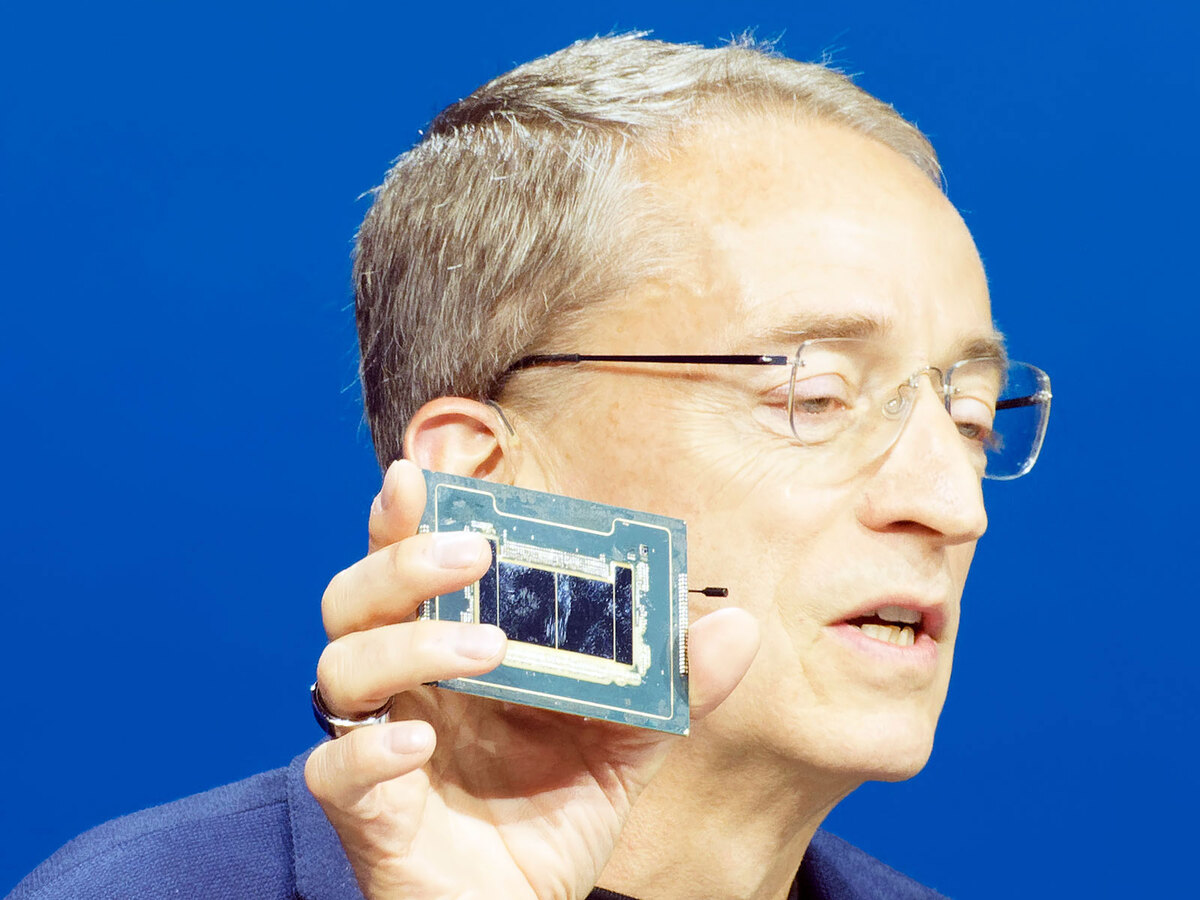

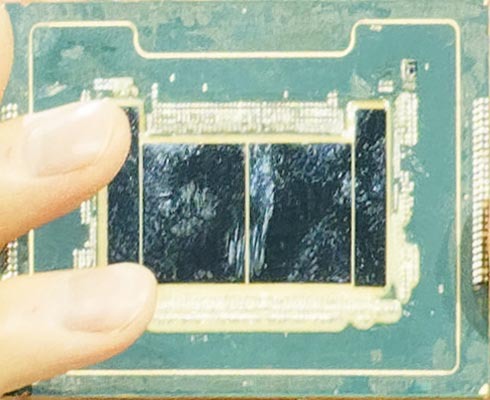

こうなると、144コアに関してはEコア×4のクラスターが36個、メモリーコントローラが3つという計算になる。また最初の画像を見ると、このスライドとは裏腹に、コンピュート・チップレットはパッケージの中央ではなく、偏りを持って配されていることがわかる。最初の画像のパッケージ部の歪みを補正したのが下の画像で、これを見るとCompute Tileの幅はI/O Tileの80%ほどである。つまり5:4の関係である。

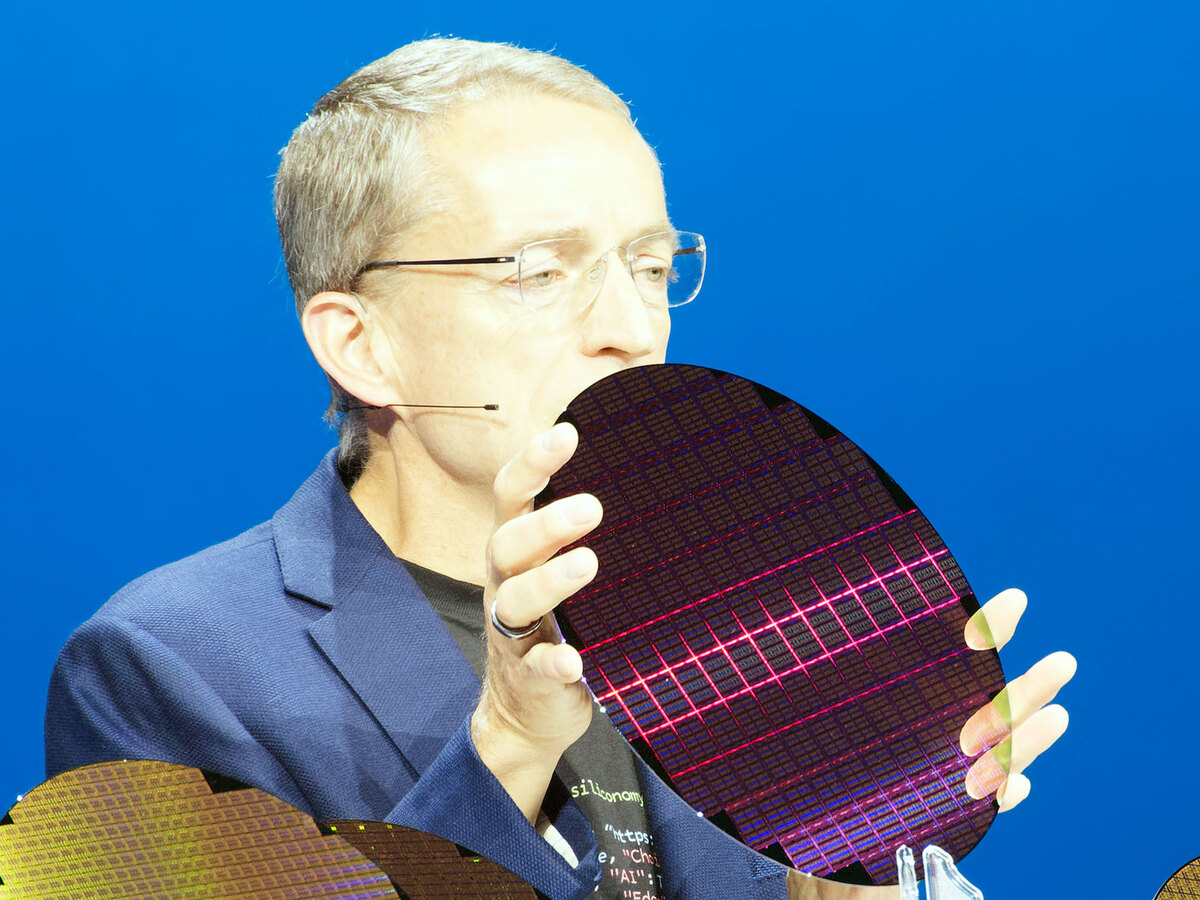

また今回Gelsinger CEOはSierra Forestのウェハーも公開した。ただこちらでは斜めからの撮影の関係で、ダイの構造がよくわからない。

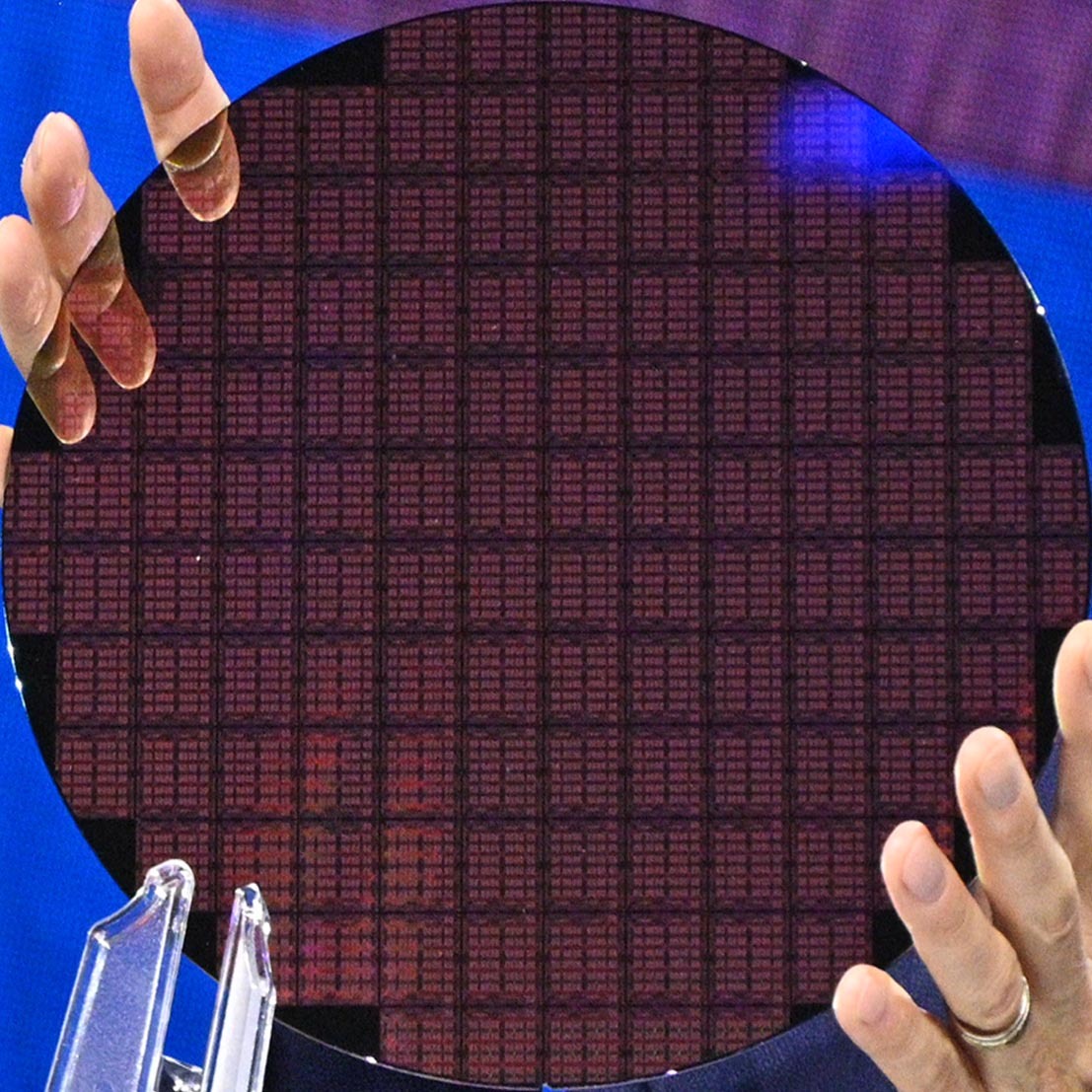

そこでインテル提供の正面からの写真をレタッチして縦横比を補正したのが下の画像である。

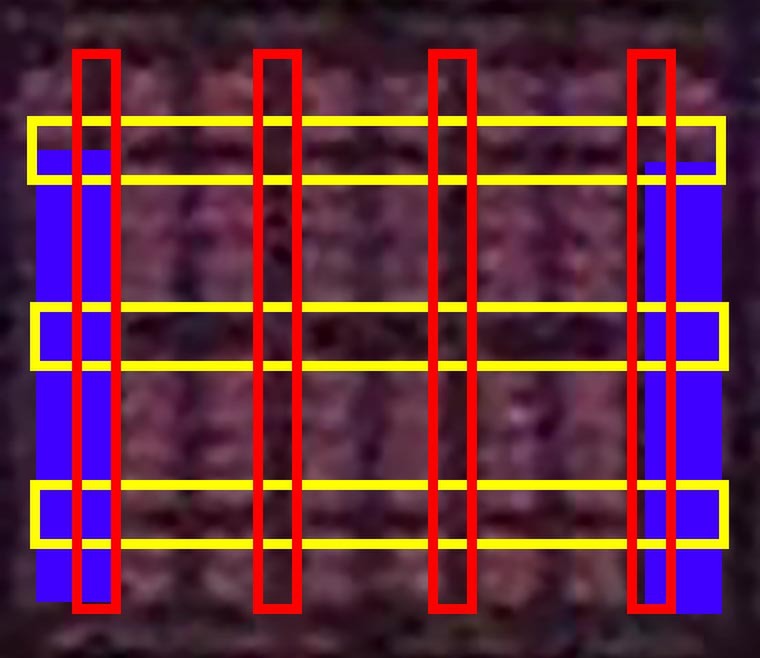

ここから4ダイ分を抜き出したのが下の画像だ。

- 一番上のみ横が8ブロック。その下は6ブロック。縦方向は6ブロック分。

- 上の画像では、縦方向に4本、横方向に3本のメッシュが通っているように見える。

- コンピュート・タイルは6×6のブロックに集中しており、その左右にはみ出している2ブロックの下にあるのはPHYに見える

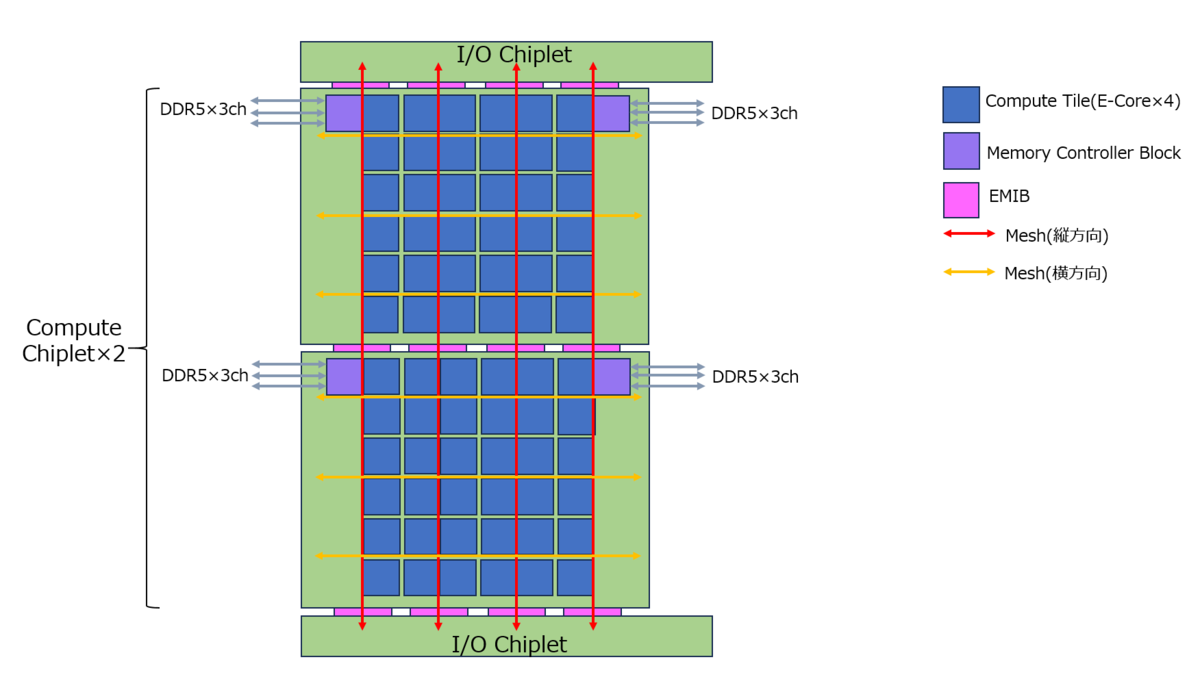

ここで、以下のことが想像できる。

- 赤:上下方向のメッシュ。これはEMIB経由でダイの外に接続される。

- 黄:左右方向のメッシュ。これはダイの中で完結する。

- 青:おそらくDDR5のPHY

ちなみにDDR5、従来のXeon Scalableでは1ブロックに2ch分のDDR5のI/Fが内蔵されているはずだが、このルールをそのまま適用するとDDR5用のコントローラーが3ブロック要る計算になる。

ただダイ写真を見る限り、全部で38ブロック分しかないあたりは、やはりSierra Forestでは1ブロックで3ch分のDDR5を制御できるようになっている、と考えるべきだろう。

結果として、正しい(?)Sierra Forestの構造図は下図になるだろう。

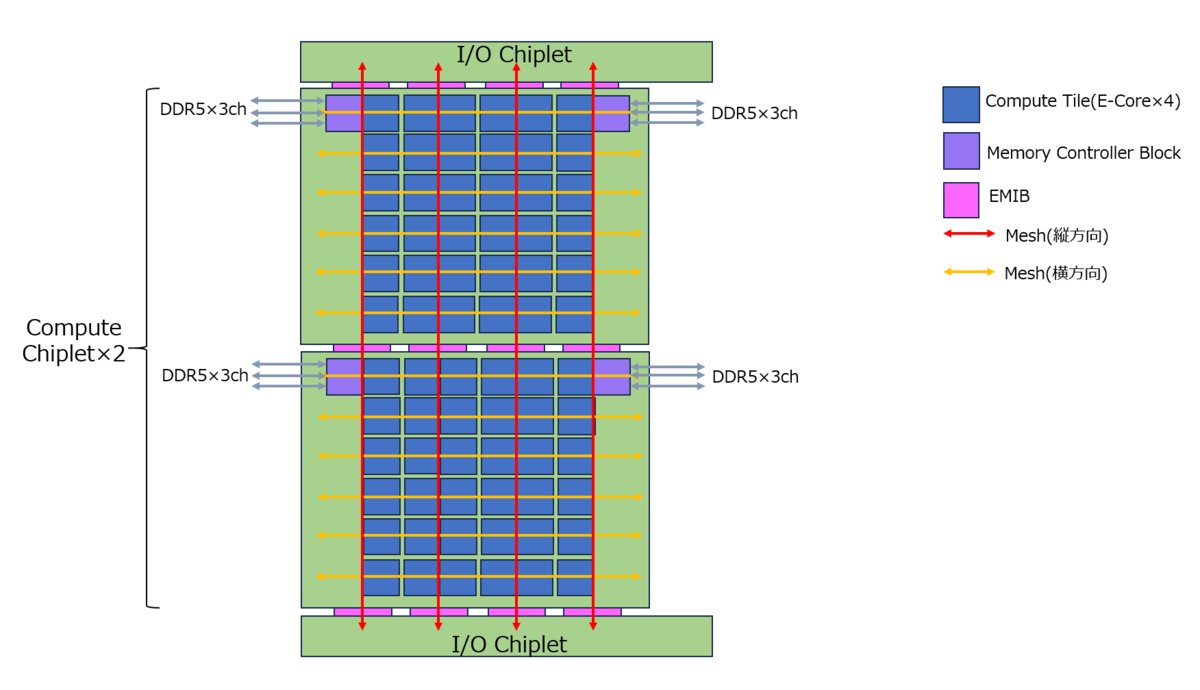

あるいは実際には横方向のメッシュは下図のようにチップレットあたり6本かもしれない。

一方縦方向は4本と思われる。これはGranite Rapidsの場合も縦方向は5本で、それがSierra Forestなどでは4本になると想定される。

そのSierra Forestのダイサイズはダイ写真を見る限り、22.34×26.53mm=592.68mm2ほどになる。ほぼ600mm2ということで、かなり大きいのは間違いない。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります