PコアとEコアが新命令セット「AVX10」でAVX512に対応

APXと同時に発表されたのがAVX10である。インテルのウェブサイトからテクニカルペーパーとホワイトペーパーを入手できるが、簡単に言えばAVX命令に拡張性を追加しようというものだ。

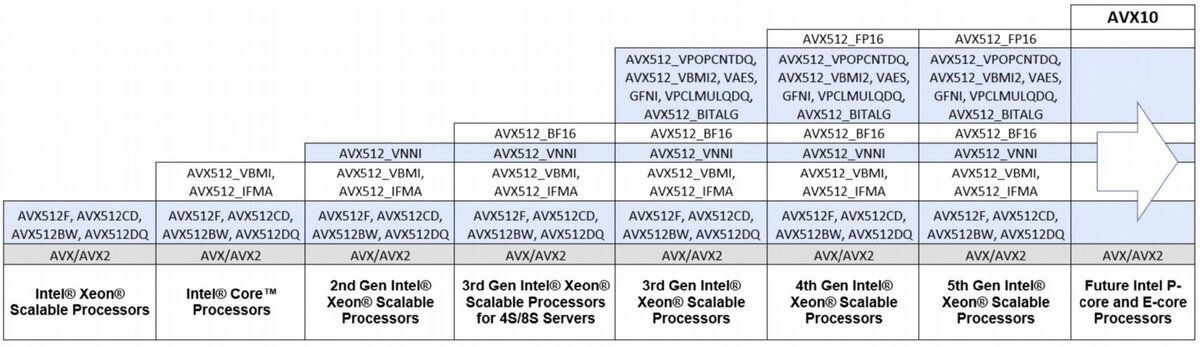

もともとAVX命令は、特にAVX512が無駄にバージョンが多すぎて、追加が止まらなくなっておりかなり混乱を招く状況だった。その一方で、例えばVNNI(Vector Neural Network instructions)は当初AVX512でのサポートだけだったはずなのに、後から256bit幅のAVX2 VNNIが追加されたりして、わかり難いことおびただしい。

そこでインテルとしては以下のことを明らかにした。

- AVX512の拡張はこれ以上行わない

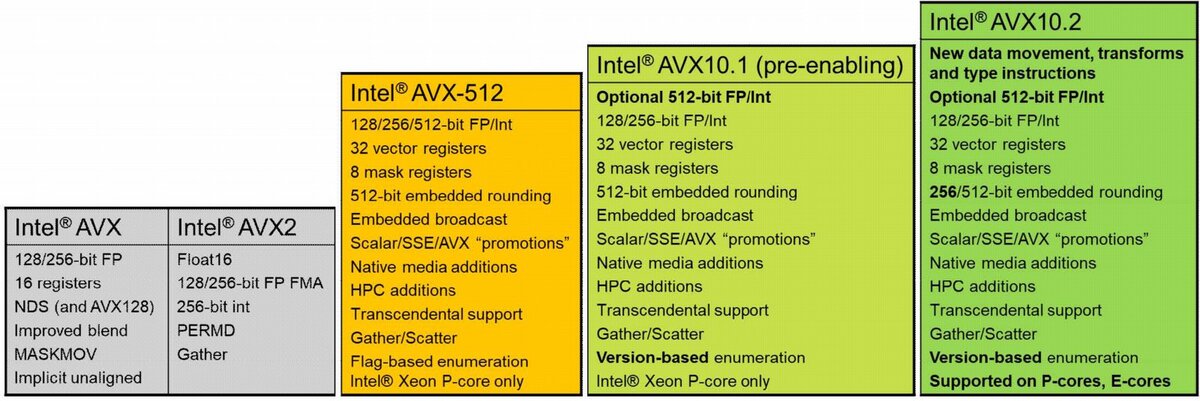

- AVX512の機能はそのまま継承するが、必ずしも512bitの実装を必要としない

- 128/256bit幅もサポート

- 今後はVersion-baseでの機能追加を行なう。つまりつまりAVX512-xxxxのような形での実装ではなく、AVX10.1/10.2/10.3/...とバージョンがあがるのに対応して機能が追加される。

ここで2つ目のポイントであるが、これは要するにArmのSVEやRISC-VのVEEと同じように、Vector(というよりSIMD)の幅を可変長にできるというものだ。

これと3番目のポイントが連動するわけだが、AVX10では、例えば128bit幅のSIMDを4回、あるいは256bit幅のSIMDを2回回すことで、512bit幅(や、多分こういう書き方をするからには将来的には1024bit幅などさらに大きな幅)の演算が可能になるものと思われる。

実はZen 4のAVX512サポートがまさにこれである。Zen 4は256bit幅のFPUを2つ同時に動かすことでAVX512をサポートする格好だ。

実のところ、現在のインテルのEコアはAVX512のサポートがない。AVX512のサポートを追加すると、猛烈に回路規模が大きくなってしまうからというのがおそらくの理由であるが、この結果として現状XeonではPコアのみの構成しか提供されていない。

Eコアのみで実装されるSierra Forestは2024年投入予定だが、このSierra ForestでAVX512をサポートしない、というのはさすがに問題がある。そこで、性能が低くなっても良いから小規模な回路増加でAVX512をサポートする、という方策に転換したものと思われる。

またVNNIのようにAVX512からAVX2に命令を逆移植というパターンが増えてたので、このあたりで命令とデータ幅を分離して整理する方向に舵を切った、というあたりだろうか。

こう考えてみると、X86-S/APX/AVX10のいずれも、最初に実装されるのはサーバー向けのXeon Scalable向けだろう。サーバー用のOSはもう16/32bitは一切不要だし、古い16/32bitサーバーを使っているという話も聞かない。

APXに対応したアプリケーションは従来のx64プロセッサーでは動かなくなるが、サーバー向けの最新版のアプリケーションは最新のプロセッサーに向けたものが少なくない。つまり過去のハードウェアとの互換性をあまり考える必要がない。

そしてAVX10、まずはSierra Forestへの対応が最初に行なわれることになると思われる。このあたりがコンシューマー向けのCoreプロセッサーに波及してくるのは、Xeon Scalableの後になるのではないだろうか? もっとも冒頭でも書いたように、X86-Sはまだ提案の段階である。実際にはXeon Scalableのみの対応、という可能性もありそうだ。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります