GAAを利用するための3つの困難とその解決策

今回の講演の中では、GAAの製造の難しさについても説明があった。

まずはトランジスタの製造後に配線層を積層するわけだが、その配線層の積層プロセスの工程が最上位のNano Sheetにダメージを与えるというもの、2つ目がSheet間のメタルゲートの削除が面倒なこと、最後がNano Sheetの幅が広くなると、両端と中央で特性が変わってきてしまうことの3つが言及された。

その問題に対する回答は、当然ながら詳細はまさにGAAを利用するためのノウハウになるので開示はされていないのだが、まず1つ目の問題は“Soft Metal Gate Removal”を利用することで、ゲートからのリーク電流をSF4と比べた場合PMOSは1.58倍だったものを0.28倍に、NMOSでは1.06倍だったものを0.43倍にできたとする。

要するに従来だと最上位のNano SheetがMetal Gate Removableで傷んでしまい、そこからのリークがけっこう多く発生したのが、これでだいぶ緩和された。またMetal Gateの製法にも改良を加えたことで、Nano Sheetの幅に起因する電圧の差も大幅に削減できたとしている。

なにをどうソフトにするのかは当然秘密であるが、普通ではCMP(Chemical Mechanical Polish:研磨剤を使って削り取る方式)なので、これを行なう際の圧力を減らしたり研磨剤の特性を変えて削り方を緩やかにしたりするなど、だろうか?

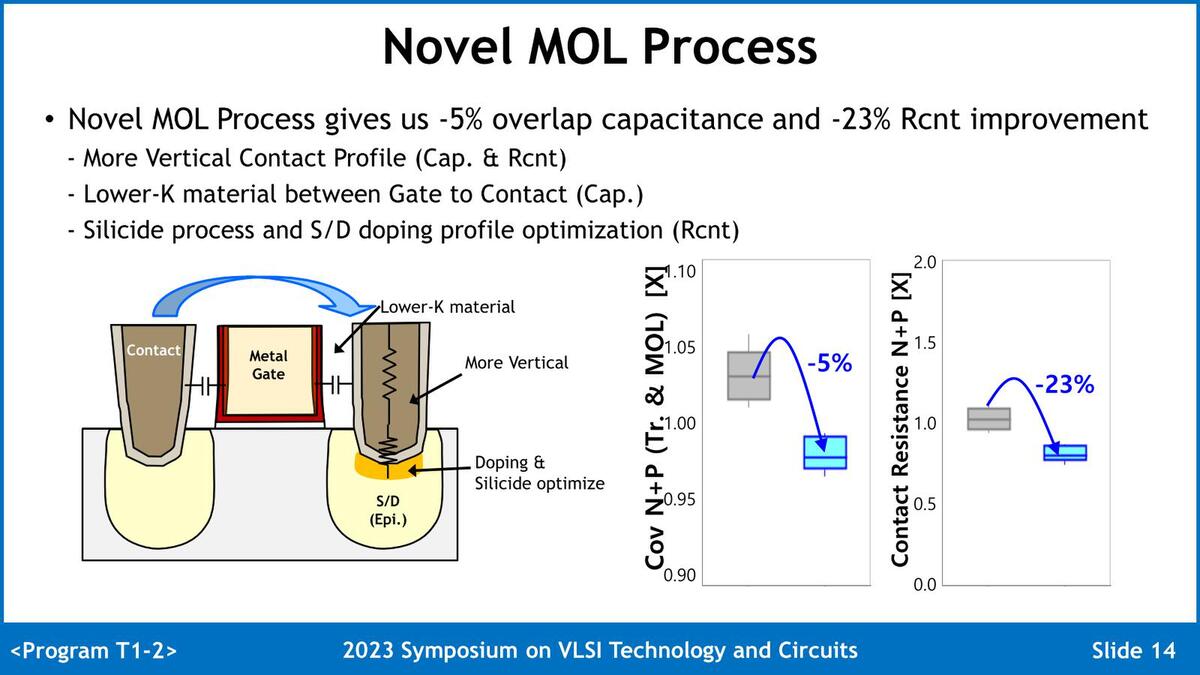

2つ目の問題については、直接的な回答ではないのだが示されたのはMOL(Middle Of Line:中間層)の製造プロセスの改良である。Metal Gateと接続するコンタクト部を、より細長い形状にするとともに、ソース/ドレインの接続部分の組成の最適化をすることで、寄生容量を5%、抵抗を23%削減したとする。

3つ目の問題はDTCO(Design Technology Co-Optimization)の採用で解決した、という。Nano Sheetの構造だけで問題を解決するのではなく、回路側の最適化と組み合わせることで対応したという話で、同じ駆動電流の場合NANDゲートで2.5%、NORゲートで4.5%の高速動作が可能になったとされる。

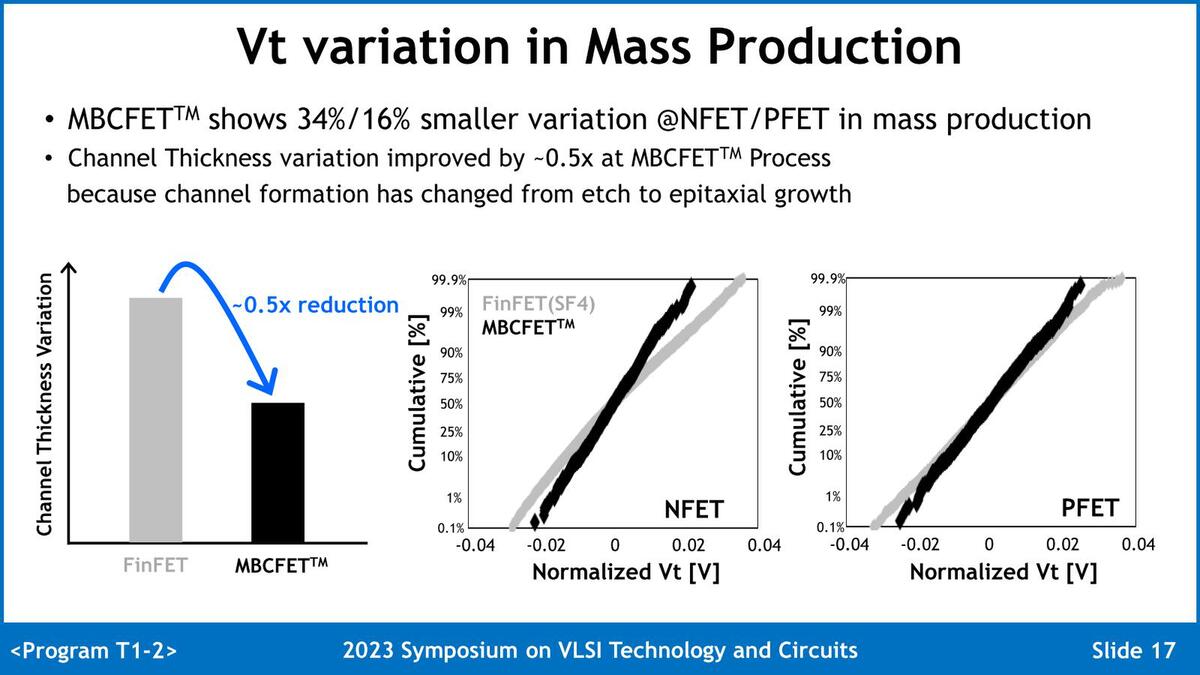

ちなみにこうした工夫の結果として、SF4と比較した場合、SF3では特性のバラつきが大きく減ったとされる。これを実現できた理由の1つはチャネルをCMPではなくエピタキシャル成長に切り替えたことがある。ただ確かに特性はそろいそうだが、CMPに比べると時間が掛かりそうな気がするのだが、そのあたりについては言及がなかった。

今回はこのSF3の歩留まりについては説明がなかったし、SF3Eの当初の歩留まりを考えれば、立ち上がりはやや鈍い(プロセス立ち上げ時の歩留まりが低いのは、すでにSamsungの御家芸になっている気もしなくはない)とは思うが、それでも技術的な完成度にはそれなりの自信を感じさせる。

ちなみに今回説明はしないが、T4-1の結論は、BS-PDNを使うことで動作周波数を3.6%向上させ、一方でブロックレベルでのエリアサイズを14.8%削減できるとしている。

動作周波数が上がるのは電流供給能力が改善したことに起因する話で、エリアサイズ削減は電源層を裏面に追いやれることで配線層にゆとりが生まれたためだろう。

インテルはこのBS-PDNをIntel 20AプロセスでGAAと一緒に導入する予定だが、Samsungはより確実性を狙ってかSF3にはBS-PDNは導入しないようだ。ただSF3Pなどは、ひょっとするとSF3+BS-PDNかもしれない。あとは顧客が付くかどうかがSamsungにとって最大の問題かもしれない。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります