ソニーは2月7日、業界初のDRAMを積層した3層構造積層型CMOSイメージセンサーを開発したと発表した。

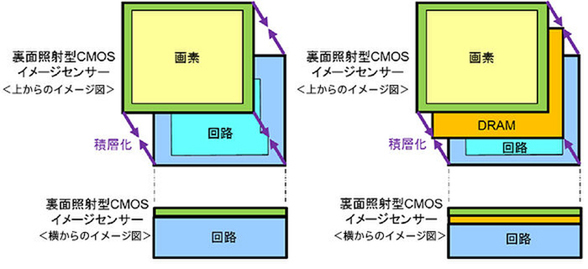

従来の裏面照射型CMOSセンサー(画素部と信号処理部の2層)に加え、DRAMを積層したもので、従来のCMOSセンサーで生じていた動きの速い被写体での歪みをなくすことができる。

従来のCMOSでは、画素に蓄積された電荷の読み出し速度の問題から、高速で動く被写体が歪んでしまったり速いパン・チルトで映像が波打つという問題があった。読み出し信号回路を二重化するなどの工夫がされていたが、信号速度の制約から一定以上の読み出し速度の実現は難しかった。

ソニーの新CMOSでは、読み出した画素をいったんDRAMに保存してから読み出すため、1920×1080ドットの画像でも毎秒最大1000フレームという従来の8倍の速度で撮影できるという。撮像素子は有効2120万画素(5520×3840ドット)、4K映像を60fpsで撮影可能。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります