第867回

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする

2026年03月16日 12時00分更新

2.2GHz動作で300TOPS超へ?

演算器構成から逆算するSpyreの動作クロック

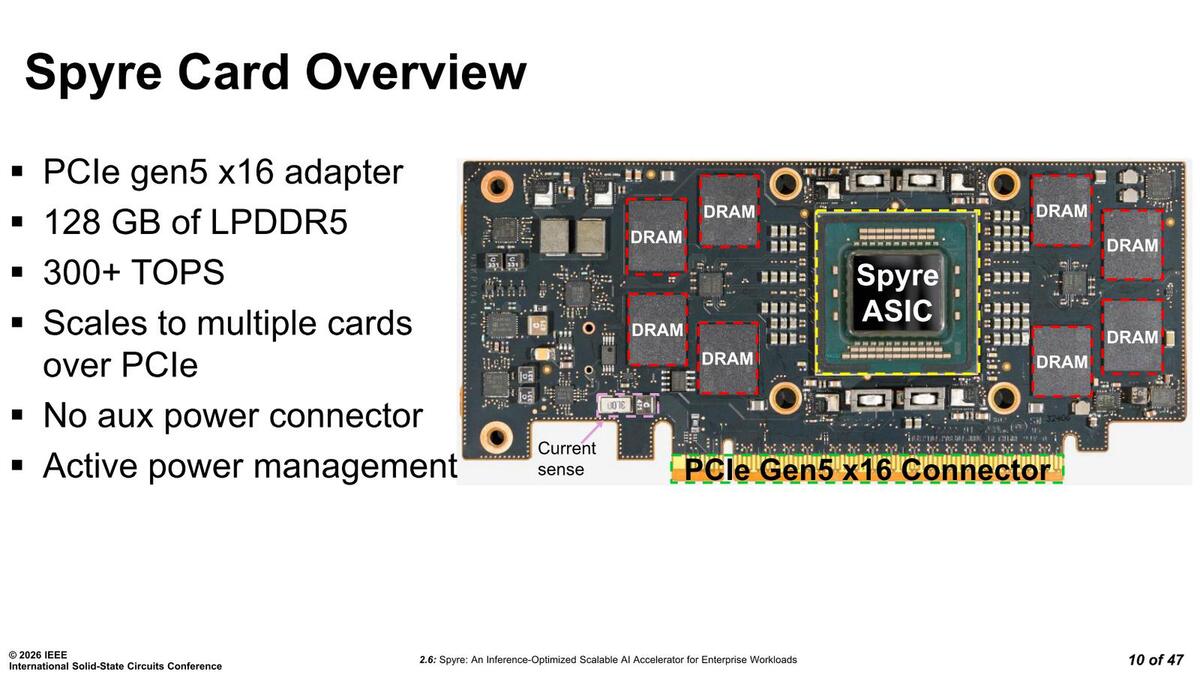

Spyreを搭載したカードの構造が下の画像だ。前掲のカード画像と見比べるとかなり似ているのがわかる。ただ、若干部品配置が異なるものもあるので、厳密に一緒というわけではない。

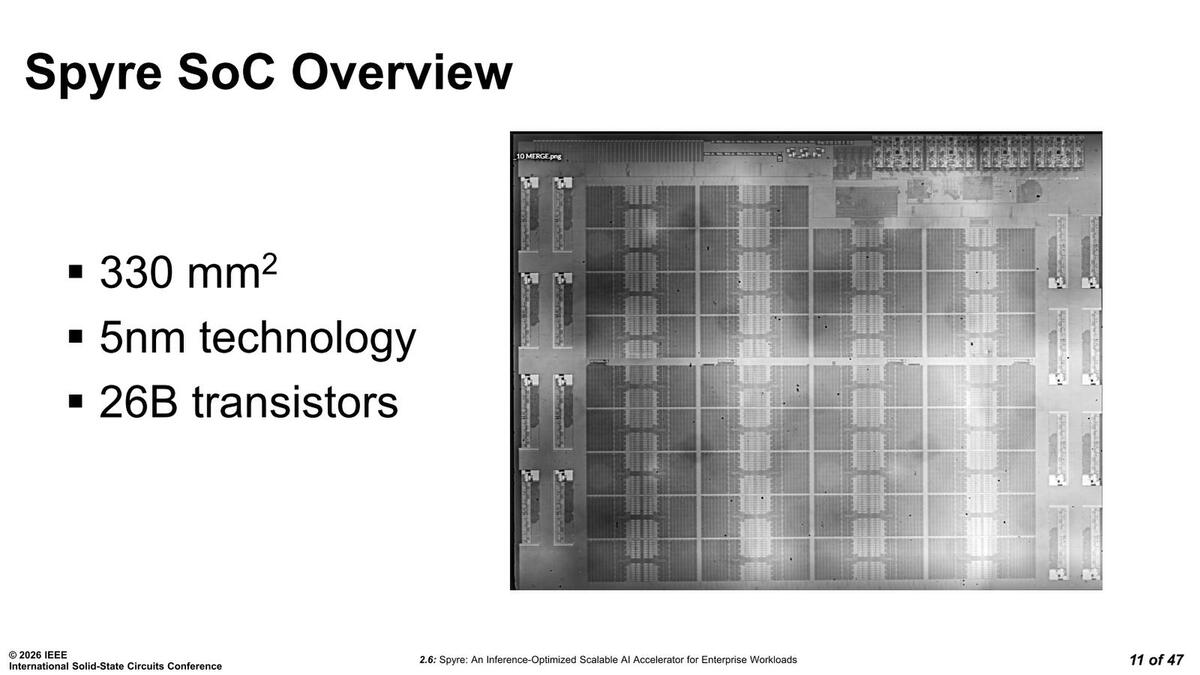

このカード1枚で300TOPS以上の性能であり、先に書いたように消費電力は75W以下である。スペック的にはQualcommのCloud AI 100カードに近い。ダイサイズはSamsungの5nmプロセスを利用してダイサイズは330mm2、260億トランジスタとされる。

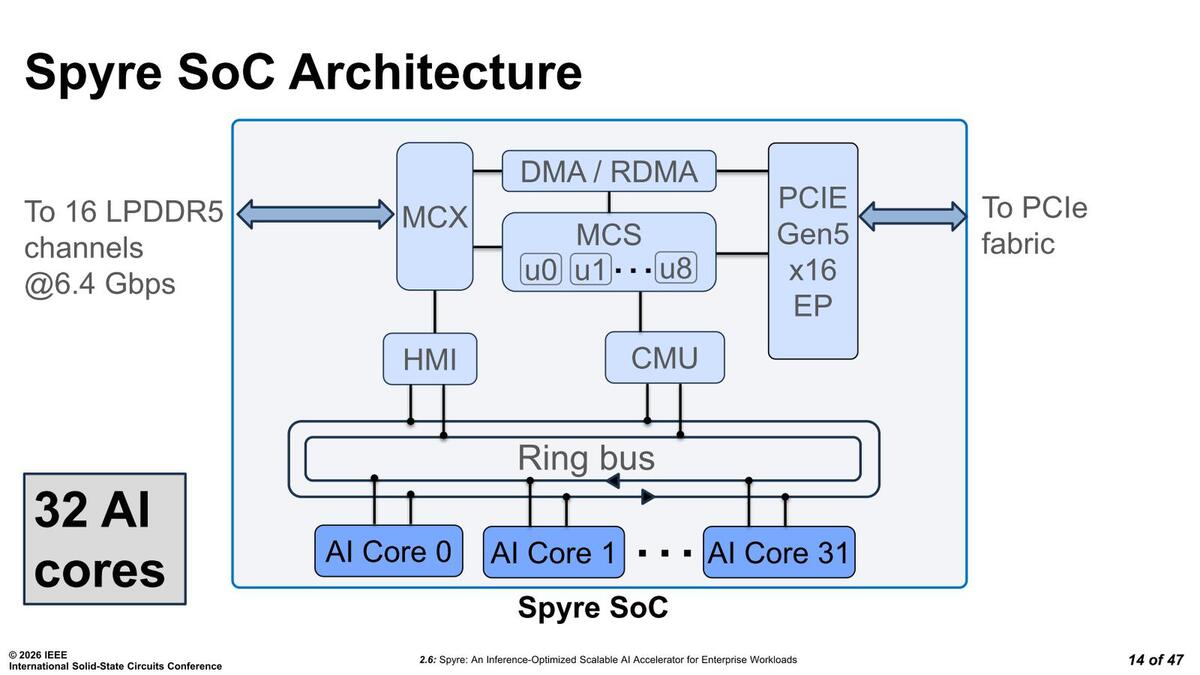

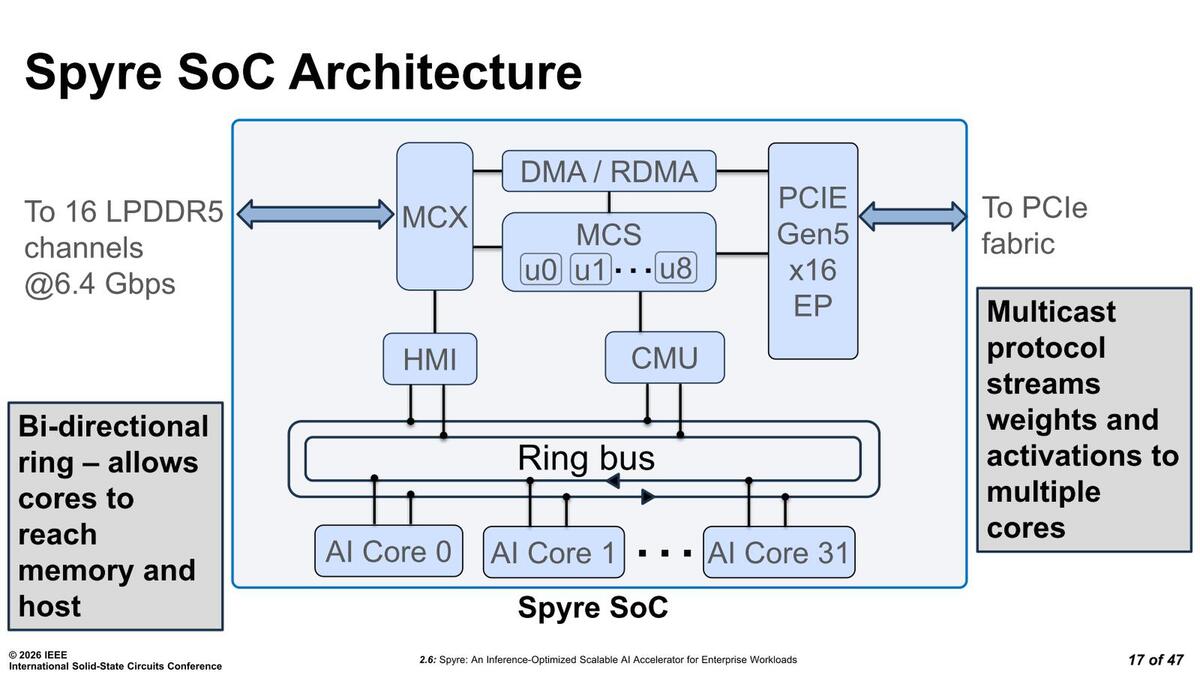

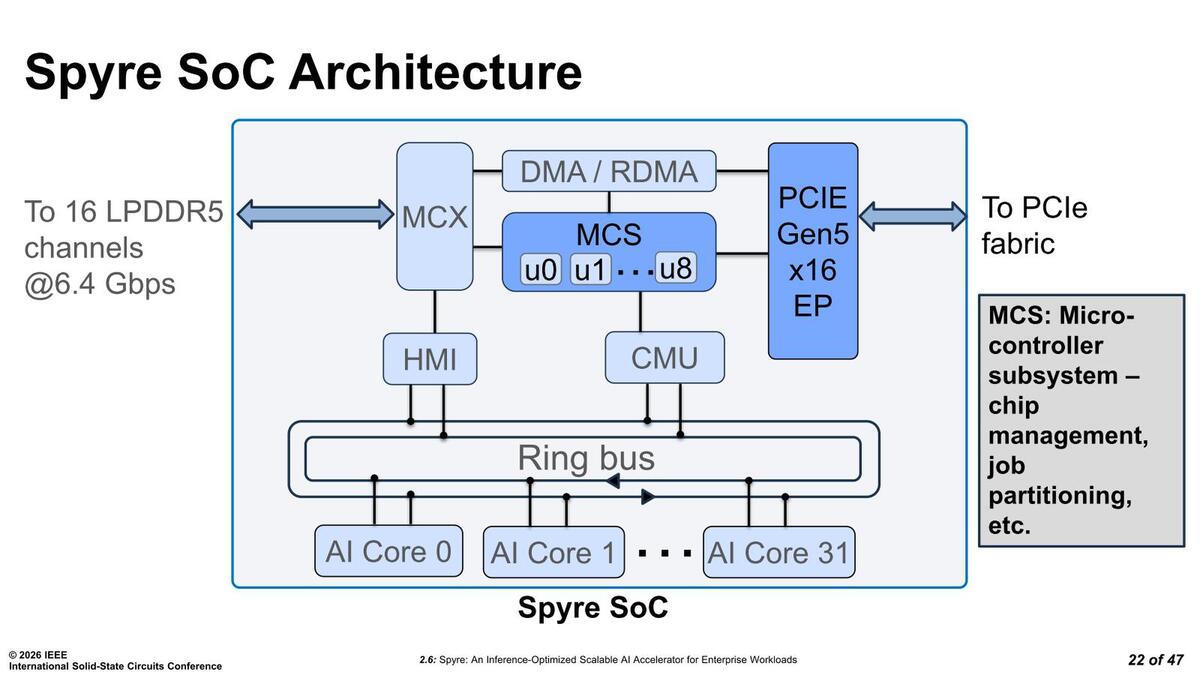

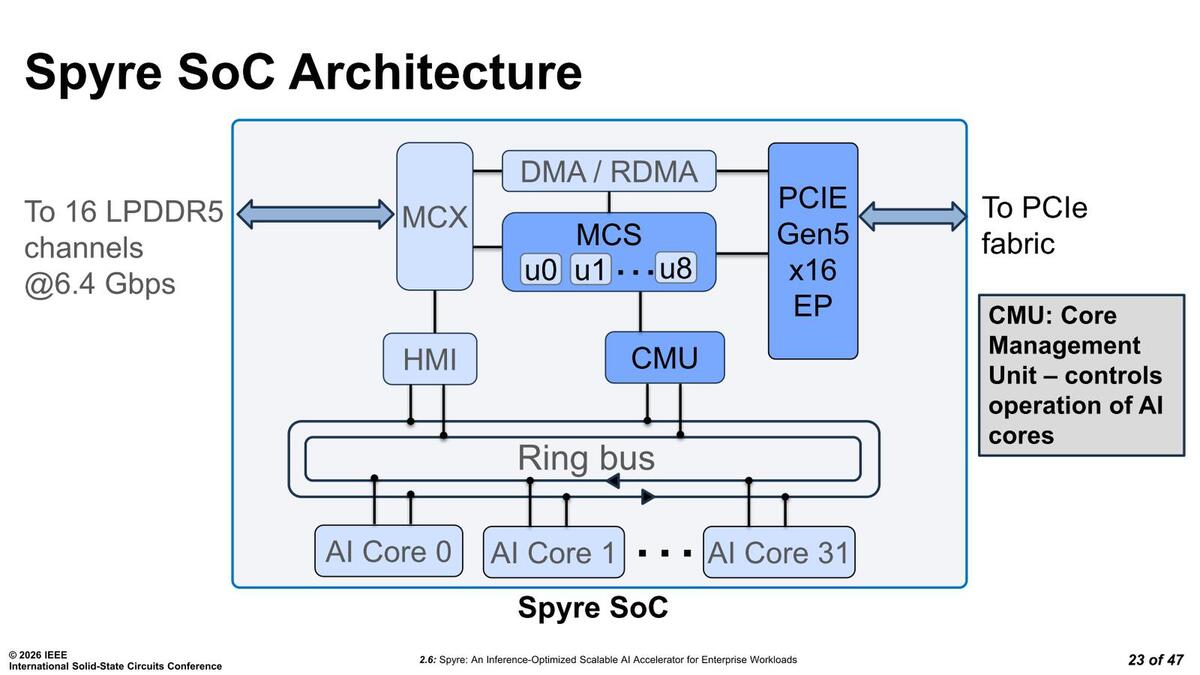

内部構造の概略図が下の画像だ。記事冒頭の画像にもあるように32コアの構成だが、これが双方向リングバスにぶら下がり、同じリングバスにメモリーコントローラーとシステムマネジメント系もつながるという、ある意味わかりやすい構図である。

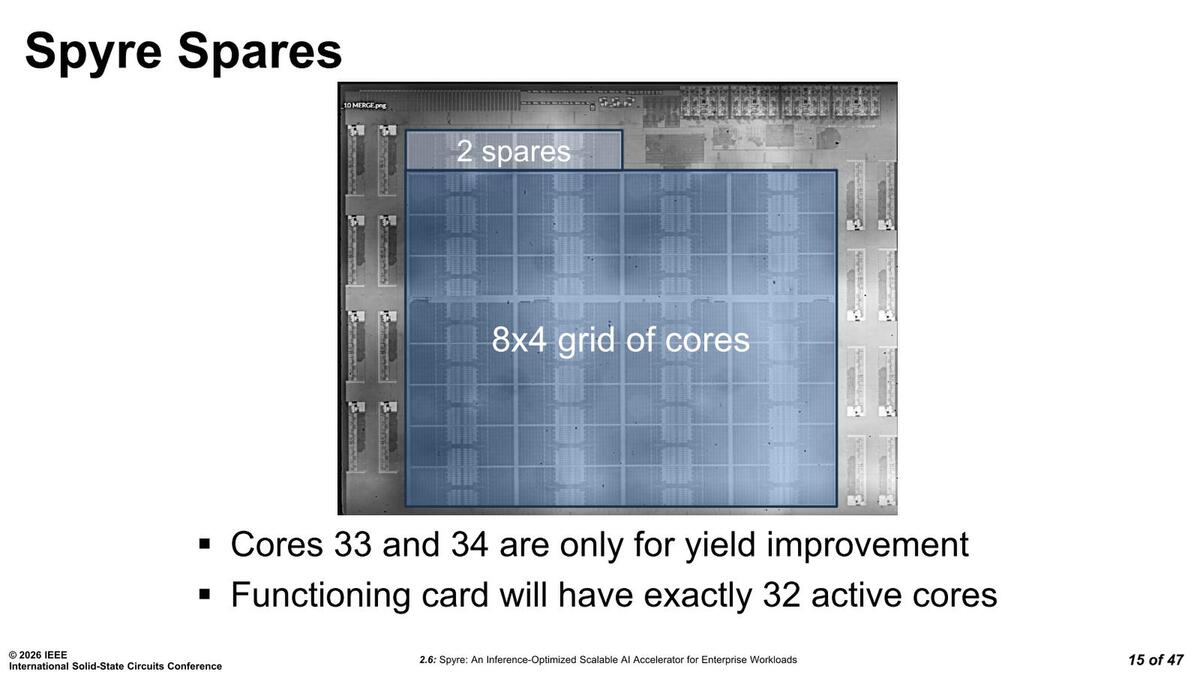

コアは32なのだが、物理的には34コア構成である。これは冗長コアが2つあるからという話だった。

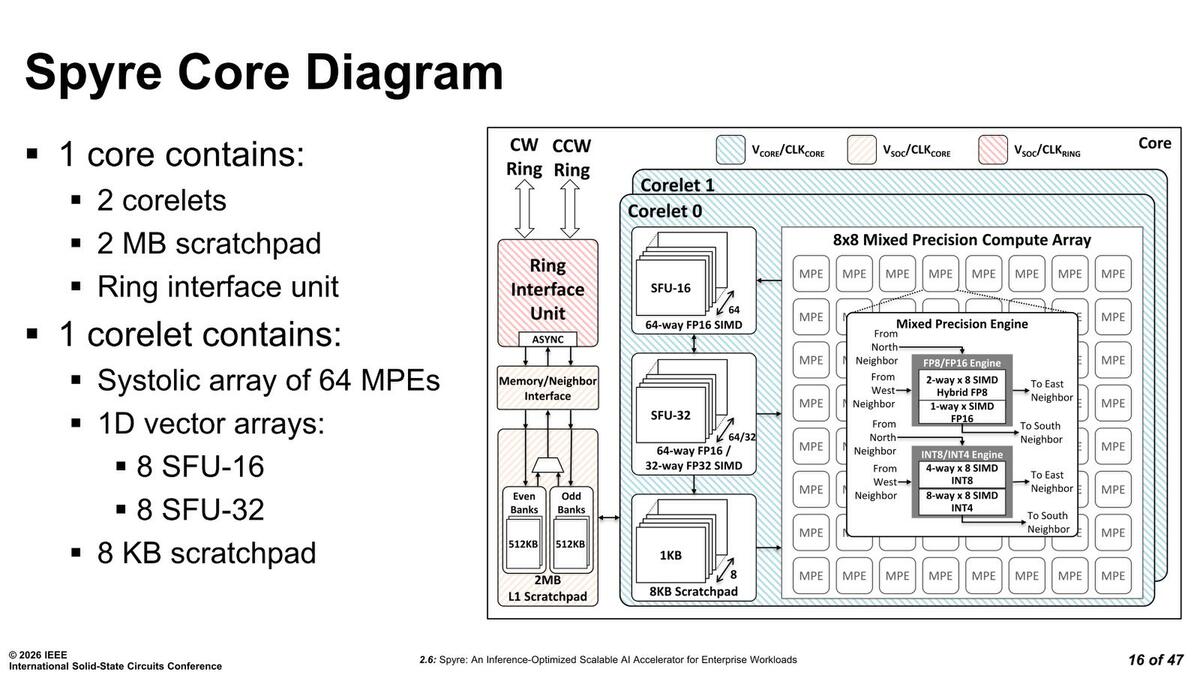

その個々のコアの中身が下の画像だ。8×8の64個のMPEが中核であり、それに8組のFP16/FP32用のSFU(Special Function Unit)と8KBのスクラッチパッドで1つのコレットを構成。このコレットが2つと2MBのL1スクラッチパッド、リングI/Fで1つのコアを構成する形だ。

FP8はe4m3とe5m2の両方のフォーマットに対応している。仮にINT4で計算すると1つのMPEで64 OPS/サイクル。1つのコレットにMPEが64個なので合計4K OPS/サイクル。このコレット×2で1コアだから8K OPS/サイクル。Spyreはこれが32個なので128K OPS/サイクルでの処理できる。

これが仮に1GHzで動作すればピーク性能は128 TOPS/サイクルという計算になる。このページの最初の画像にある300+ TOPSを実現するには動作周波数が2.2GHz以上あればいい計算だ。Samsungの5nmプロセス(SF5)ならこれは容易だろう。

コア同士は双方向のリングバスで接続される形になっている。このリングバスにMCX経由でLPDDR5、それとPCIe Gen5のI/Fが接続されている。

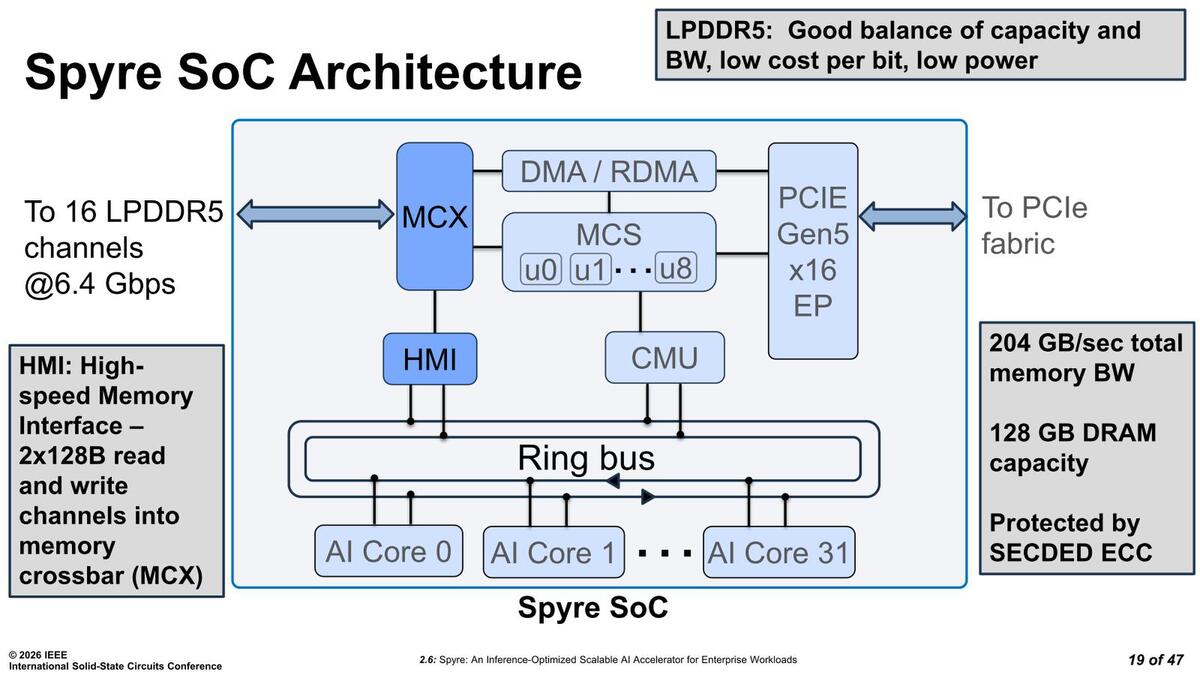

論文によれば16ch LPDDR5@6.4Gbpsで208GB/秒とのことなので、バス幅は256bitという計算になる。4つ上の画像にある、左右に配されるPHYはいずれもLPDDR5 16chのものというわけだ。基板上にLPDDR5チップは8つしかないが、Samsungはすでに16GB(128Gbit)のLPDDR5を出荷しており、これが8つで容量128GBとなるので辻褄は合う。

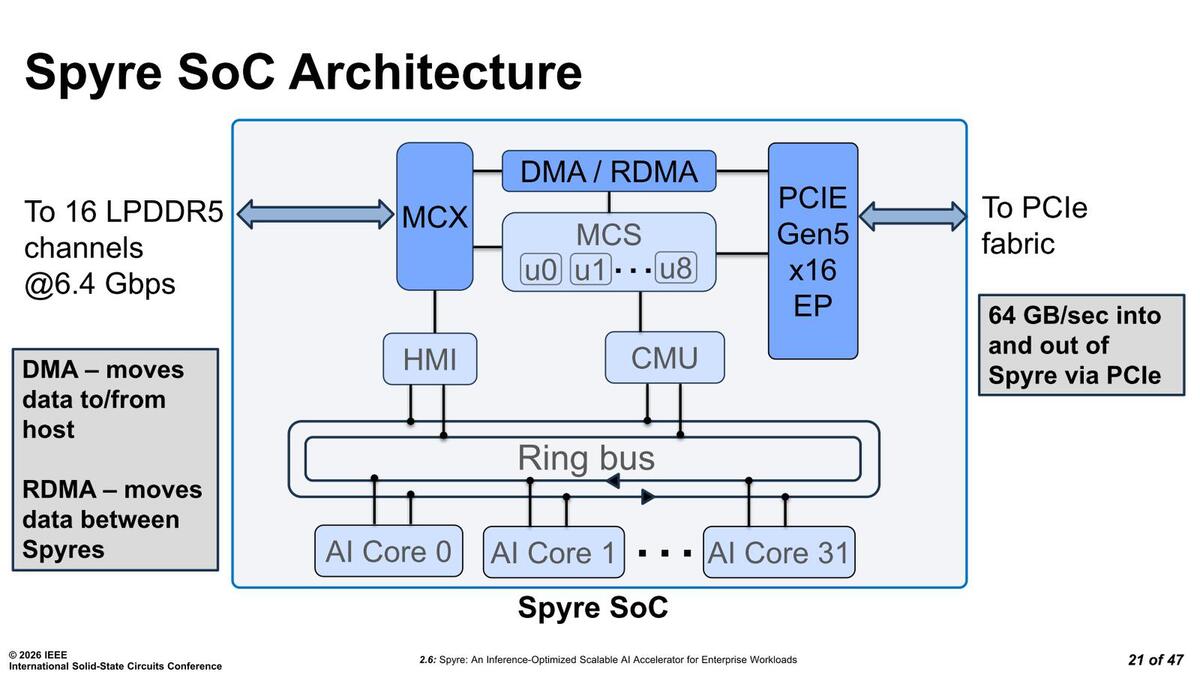

おもしろいのはMCXとPCIe Gen5 I/Fの間にRDMAが実装されていることだ。RDMAとはRemote DMAの略で元はインフィニバンド、現在はイーサネットなどで多用されているが、Spyreの場合はPCI Expressが対象である。つまり2枚のSpyreカードの間でメモリーの内容を自動で転送するためにRDMAコントローラーが搭載されている格好だ。

こうした制御を行なうために通常ではアプリケーションプロセッサーがいくつか搭載されそうなものだが、SpyreではMCUが8つ実装されたMCSが搭載されているそうだ。

絶対的な処理性能ではアプリケーションプロセッサーの方が高速だが、何かイベントが発生してから処理に移るまでの時間という意味ではMCUの方がずっと短くなるので、制御用に使われることそのものは不思議ではない。ただこのMCSはMCXやPCIe、DMA/RDMAの制御などに向けたものであり、コアそのもの制御はCMU(Core Management Unit)と呼ばれる独自ユニットが担っている。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります