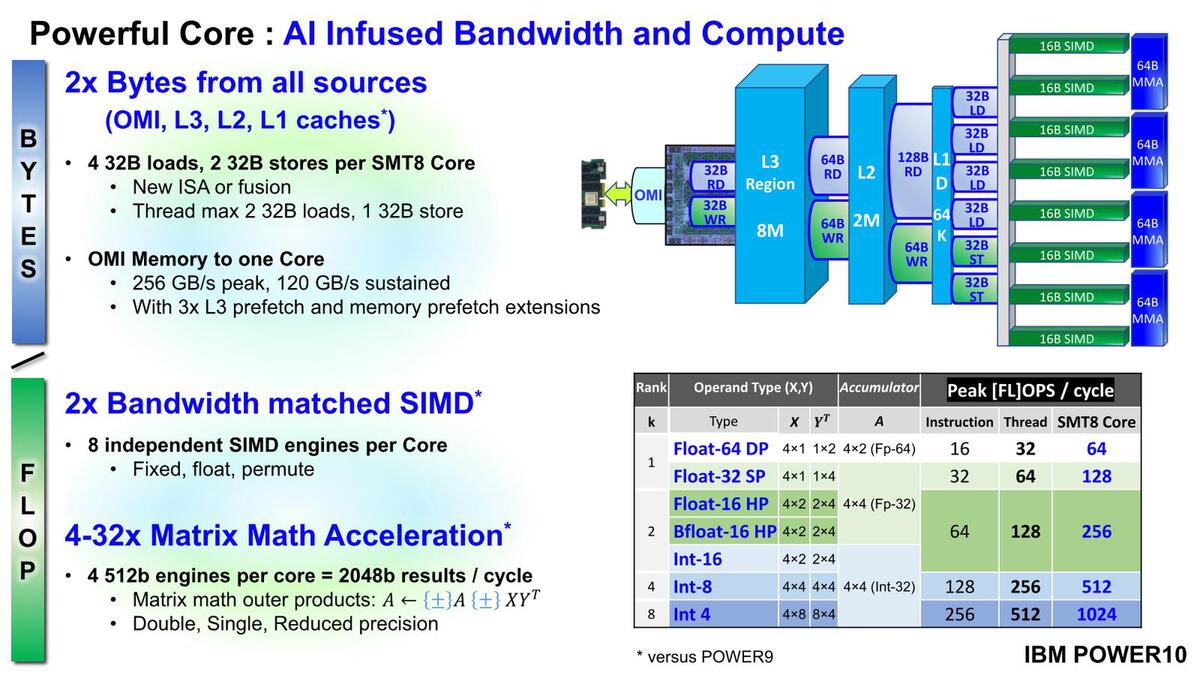

コアの数だけMMAが搭載されるためAI処理が高速になった

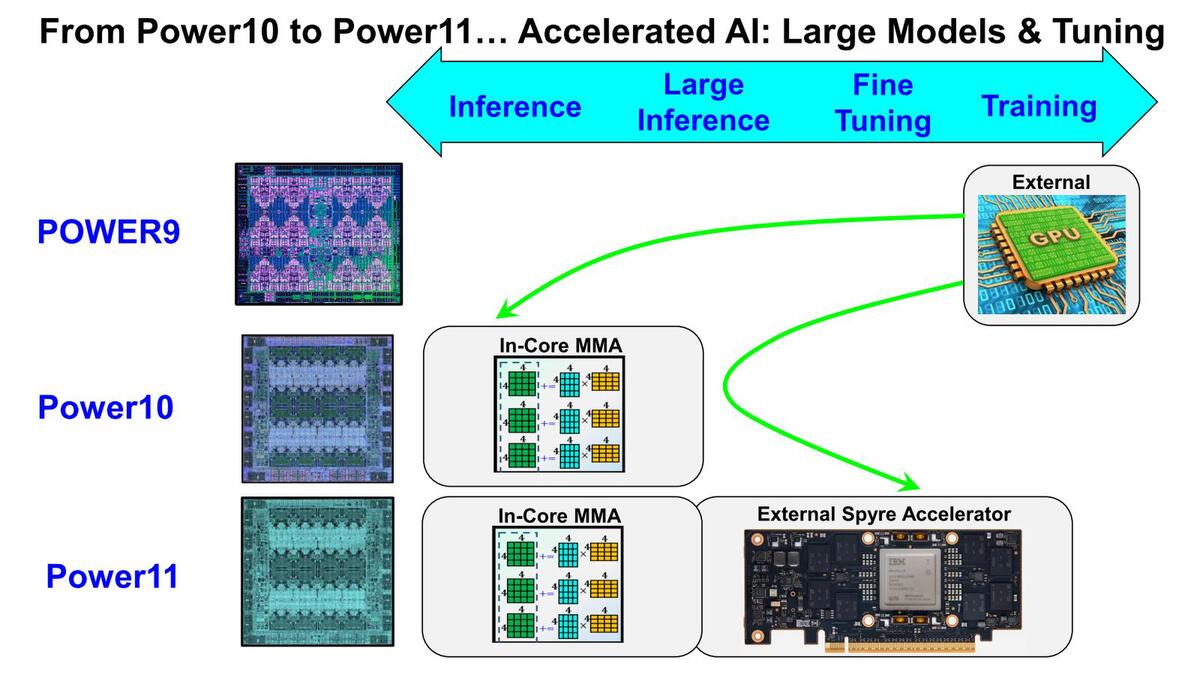

AI性能に関しての改良がIn-Core MMA(Matrix Math Accelerator)とSpyre(スパイア)アクセラレーターの接続である。Spyreアクセラレーターに関しては連載790回でも説明したが、もともとはTelum IIとあわせて発表されたPCIeカード型のAI推論用アクセラレーターである。

Telum IIと同時に発表されたからといってz専用ではなくPower11でも利用できるという話として、MMAの方はPOWER10時代に実装されたものである。

例えばMMAの性能が今回POWER10世代から倍増したわけではないようで、単にコア数がSKUによっては増えたことと、動作周波数が上がったこと、それとメモリー容量/帯域が増えたことで、従来よりAI処理が高速になったというだけのようだ

構造としてはインテルのAMXやArmのSME2と同じく、行列演算を一気に行なえるようにしたものであるが、AMXはアクセラレーターの形でソケットに1つだけ搭載されるし、SME2はコアクラスターあたり1つ(次世代は2つになるらしい)だけの搭載なのに対し、MMAはこれがコアの数だけ搭載されるわけで、下手な専用アクセラレーターよりも高速に処理できるかもしれない。

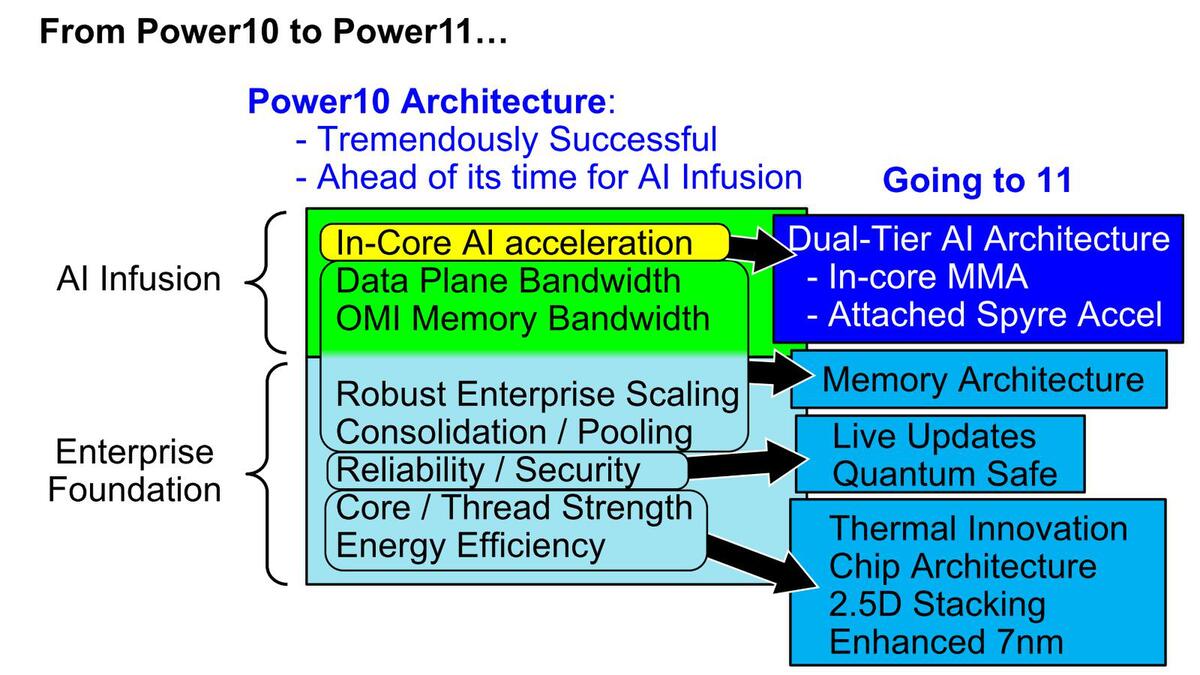

ここまででわかるように、POWER10からPower11への変更はあまり多くない。製造プロセスがあまり変わらないあたりが、マイナーアップデートの域を出ないことが示唆されている。メモリー周りの大幅強化で実効性能そのものは明確に上がっているかもしれないが、やや行き詰まり感がある。

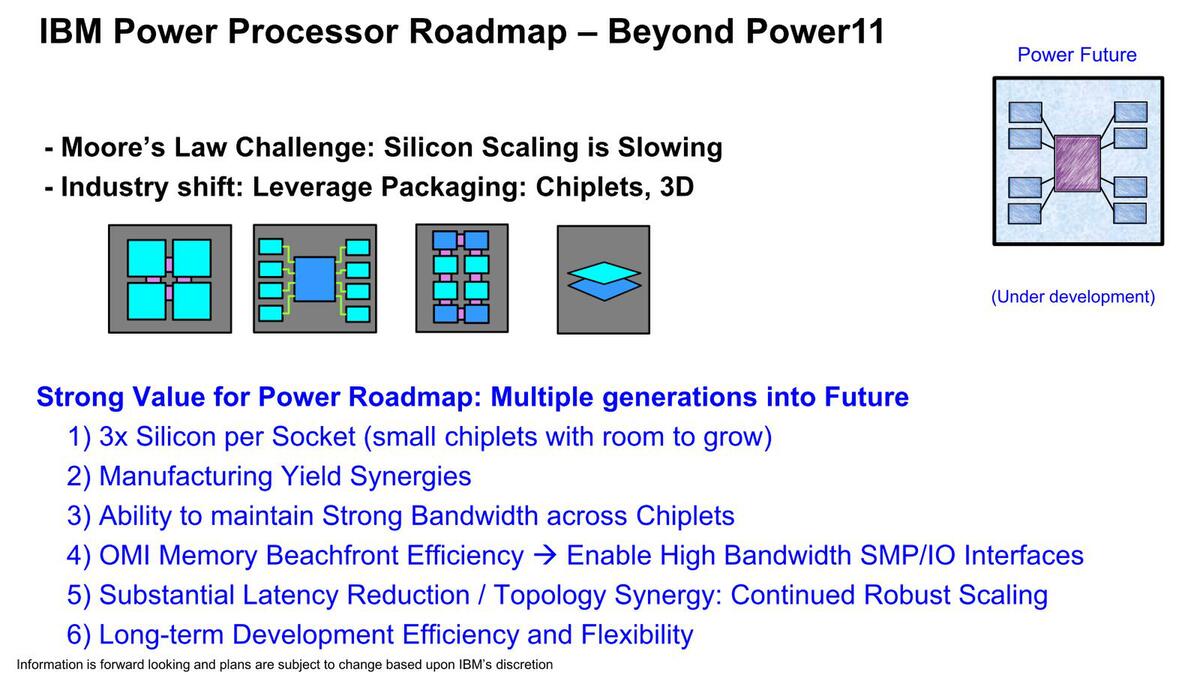

そうしたことを踏まえてか、将来計画ではチップレット化による、より大量のシリコンの実装や歩留まりの向上、OMIの効率化などが示されている。

もっともzシリーズに比べると更新頻度がゆっくりなPowerシリーズなだけに、次の製品が出てくるのは2028年か2029年になるかもしれない。その頃だと製造プロセスは2nmを切ってるというあたりか? そろそろPowerとzの製品ライン統合があっても不思議ではない状況だが、本当にPower Futureは出てくるのだろうか?

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります