コスト面での課題は残るが

次世代のインターコネクトとして有望なHybrid Bonding

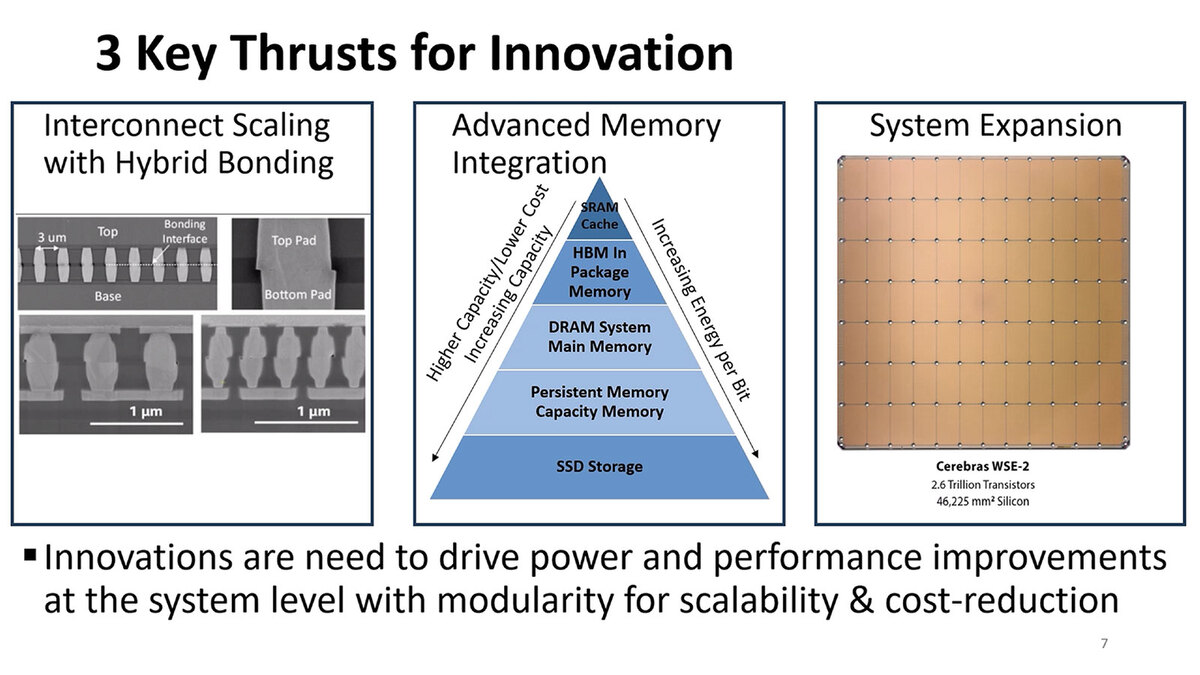

こうした問題を3つに集約して、それぞれ論じるとする。まずインターコネクトの話。ここで論じているのはHybrid Bondingである。

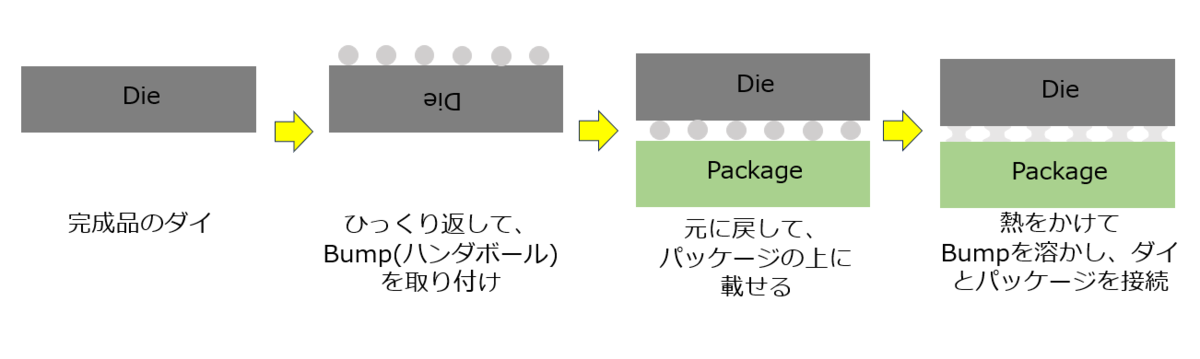

一般論であるが、ダイを基板の接続、あるいはダイ同士の接続は基本Bumpと呼ばれるハンダのボールを利用してきた。下図はこのBumpを利用する場合の基本的な接続手順である。長らく利用されてきた実績ある方法である。

最近は、特にシリコン・インターポーザーを利用する場合などには、ハンダボールの直径を非常に小さくしたMicroBumpと呼ばれるものも利用されているが、それでも以下の問題がある。

- Bumpを使う限り、温度(と圧力)を掛けた時にハンダが広がる関係で、Pitch(Bumpの間隔)を10μm未満にするのが極めて難しい。

- Bumpは基本ハンダ(さすがに最近は鉛は使われず、スズと銅、銀の合金などが利用されることが多いが、これも用途に応じてさまざまなものがある)で構成されるが、確実な接続が優先されることもあって、電気抵抗などが多い。

- Bumpを経由する場合は、基本チップの外に信号を出すという扱いになるので、PHYというほど大げさではないにしても出力用の回路(Fan Out)が必要になり、これが通信に利用する消費電力の増加につながる(あと非常にごくわずかではあるが、レイテンシー増加につながる)。

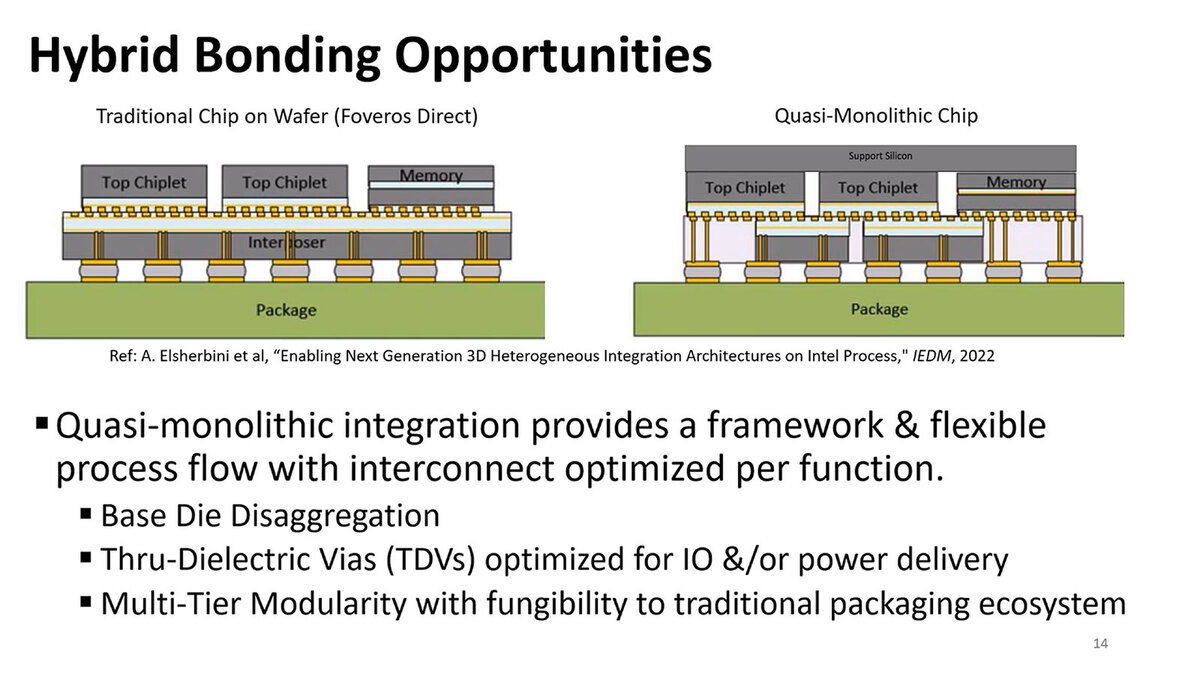

これを解決するのがHybrid Bondingと呼ばれる技法で、要するにBumpを介さずに直接2つのダイ(あるいはダイとパッケージ)を接続する方法である。もっとも現状ダイとパッケージの接続はまだ難しく、ダイとダイの3次元積層に限られている。TSMCのSoIC、あるいはインテルのFoveros DirectがこのHybrid Bondingに該当する。メリットはBumpの逆で、以下のように高速化や省電力化には欠かせない特徴を兼ね備えている。

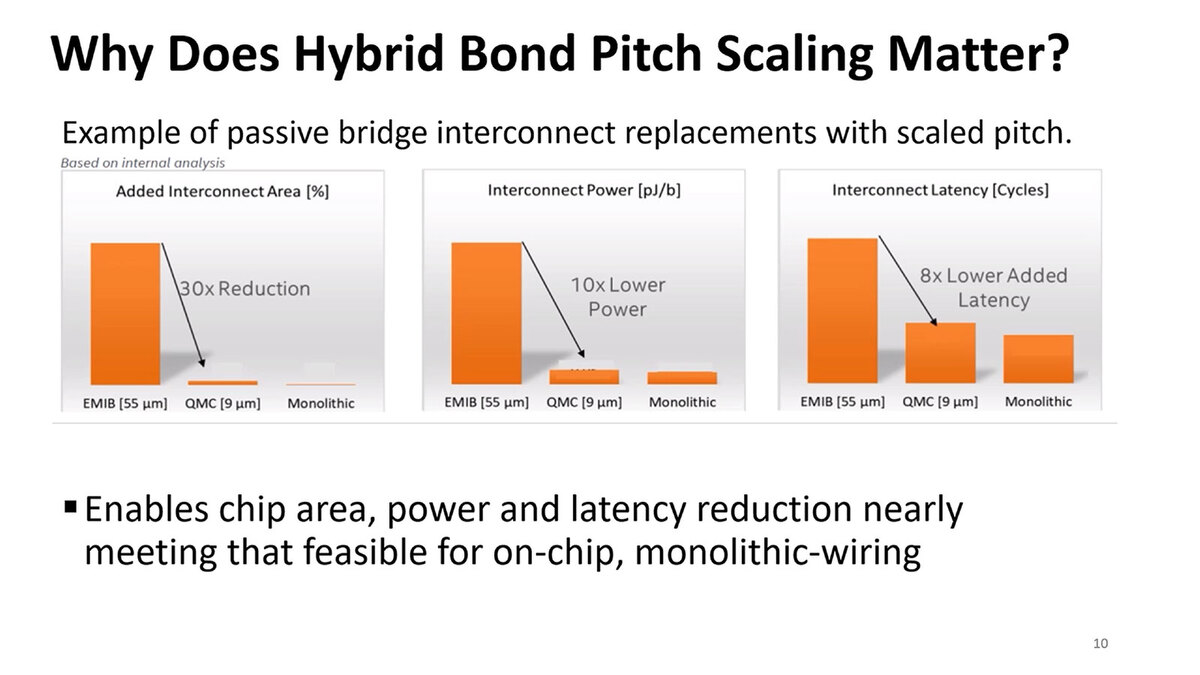

- 接合時にBumpが広がらないので、ピッチを10μm未満にすることも十分可能。

- 基本は銅と銅が直接触れ合う形になり、余分な抵抗が減る。これにより消費電力と、寄生容量に起因するレイテンシーを最小限に抑えられる。

- 基本はFan Outは不要(実際には若干保護回路が入る)

実際このHybrid Bondingを利用した場合、まず接続に必要となる面積は30分の1、接続に要する消費電力は10分の1であり、レイテンシーは8分の1になるというのがここでの説明である。ほとんどモノリシック(つまりマルチダイ構成を使わない1ダイ構成)と変わらない特性を維持できるとする。

QMCはQuasi-Monolithic Chip、つまり疑似的に1チップ(というか1ダイ)構成を取っているの意味。Ryzenに3D V-Cacheを実装したものは、実際にはCCD+3D V-Cacheで2ダイなのだが、見かけ上1ダイとして扱えるのがその代表例だ

では欠点は? というと、まずはコストである。TSMCのSoICや、これを利用したAMDの3D V-Cacheが好例だが、Hybrid Bondingはファンデルワールス力を利用する。分子間力を利用しての接続だが、このためには接続面が非常に平滑でないといけない。

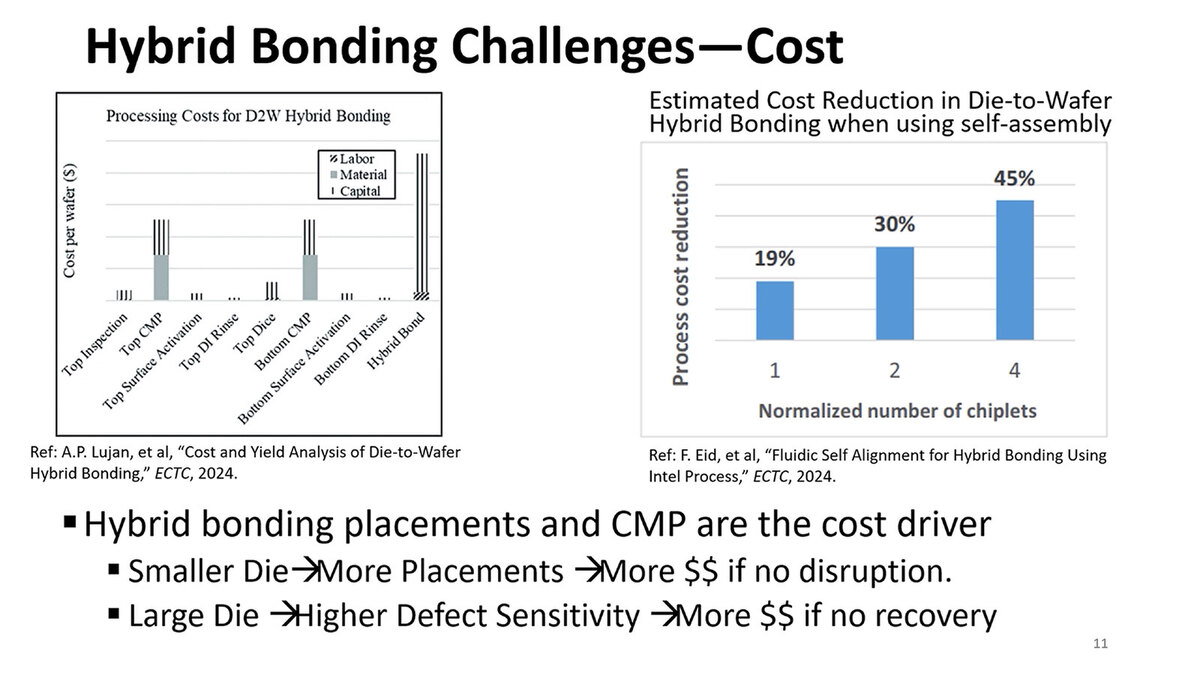

したがって接続面をCMP(Chemical/Mechanical Polishing:研磨剤などを使ってキレイに磨く処理)やRinse(CMPの後で、表面を整える処理)などが必要となる。また、2つのダイの接続面が正しい位置関係にないと、うまく信号が伝わらないことになる。このための位置合わせの精度は1μm未満でないといけないわけで、これに猛烈な手間(とコスト)が掛かる。

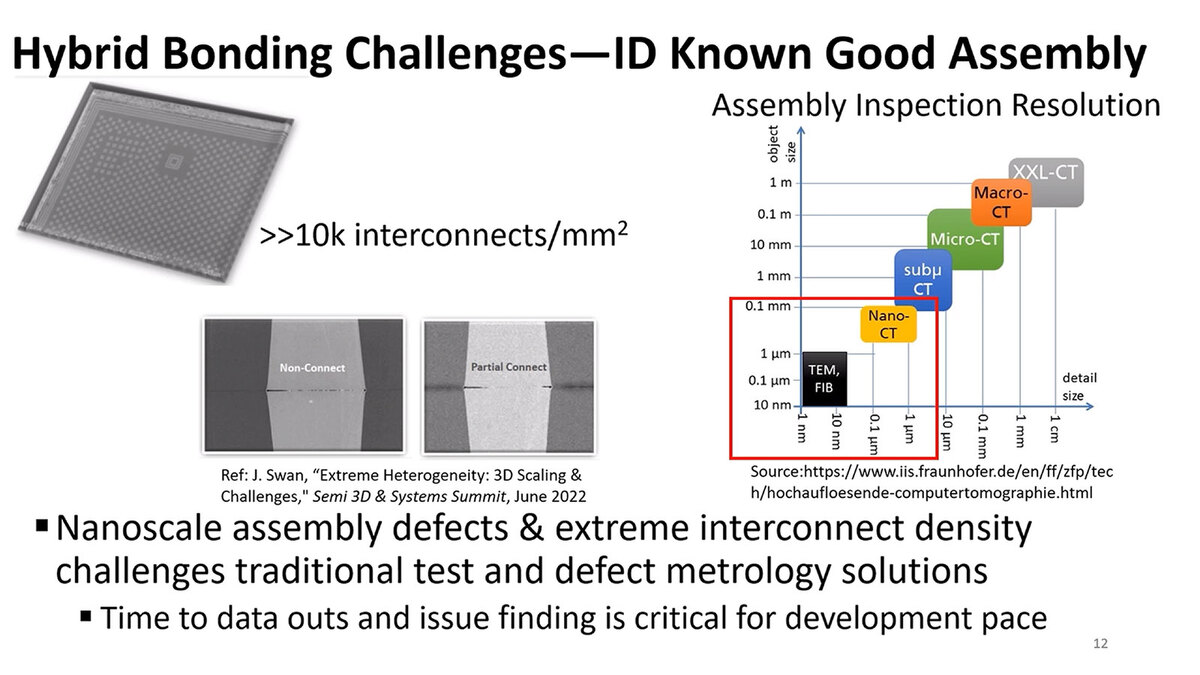

加えて言うと、検査もまた大変である。Bumpの場合は10μm程度だから、X線CTスキャナーで検査することで、正しくBumpの接続ができているか確認できるのだが、Hybrid BondingはギリギリNano-CT(1μm未満の解像度を持つX線CTスキャナー)が必要であり、その下はTEM(透過型電子顕微鏡)などの領域になってしまう。

チップレットの数が増えるとコストが大幅に上昇する。コストを低減するための提案の論文をIEDM 2024でインテルが発表している

左の写真のように、「接続できているようでつながってない」とか「中央はつながっているけど両端がつながってない(これは少しの衝撃や歪みなどで剥がれる可能性がある)」などをチェックしようとすると、猛烈な手間が掛かる。

FIBはFocused Ion Beam:収束イオンビームの略である。そもそもTEMは対象を薄くスライスし(この時にFIBを使って対象を切り出す)、それに対して内部構造を見るという破壊検査であり、故障した製品の分析には使えるが、対象を破壊するため製造の後の検査には使えない

このようにいろいろと課題はあるものの、Hybrid Bondingは現時点では次世代のダイ間接続のインターコネクトとして非常に有望であるとし、複数チップを積層するようなケースで利用できるというのが1つ目のまとめである。

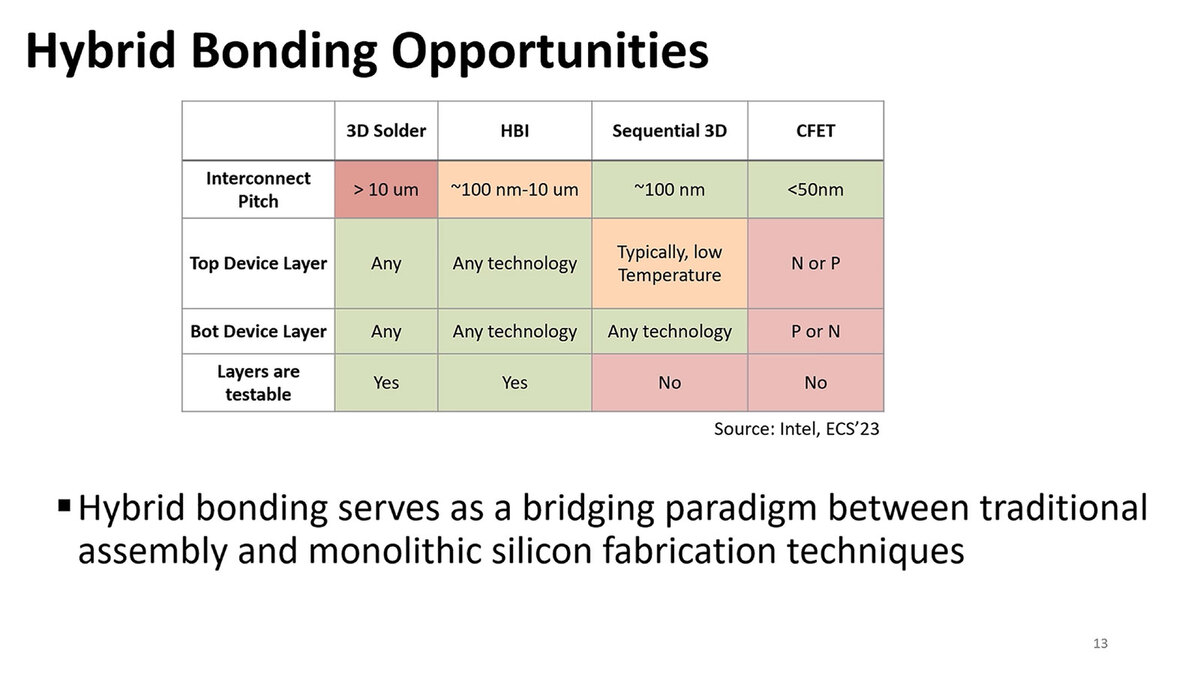

Hybrid Bondingは次世代のダイ間接続のインターコネクトとして非常に有望。3D Solderというのが従来型のBump、次いでHBI(Hybrid Bonding Interconnect)、Sequential 3D(ダイ単位で分離せずに、直接複数のデバイスを積層していくというもの。LSIのトランジスタ層を複数重ねるものと考えればいい)、CFET(前回説明した)の4つを比較して、一番有望(グリーンが多く、ピッチも3D Solderより小さ目)とするが、CFETはインターコネクトとは違う気もする

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります