第803回

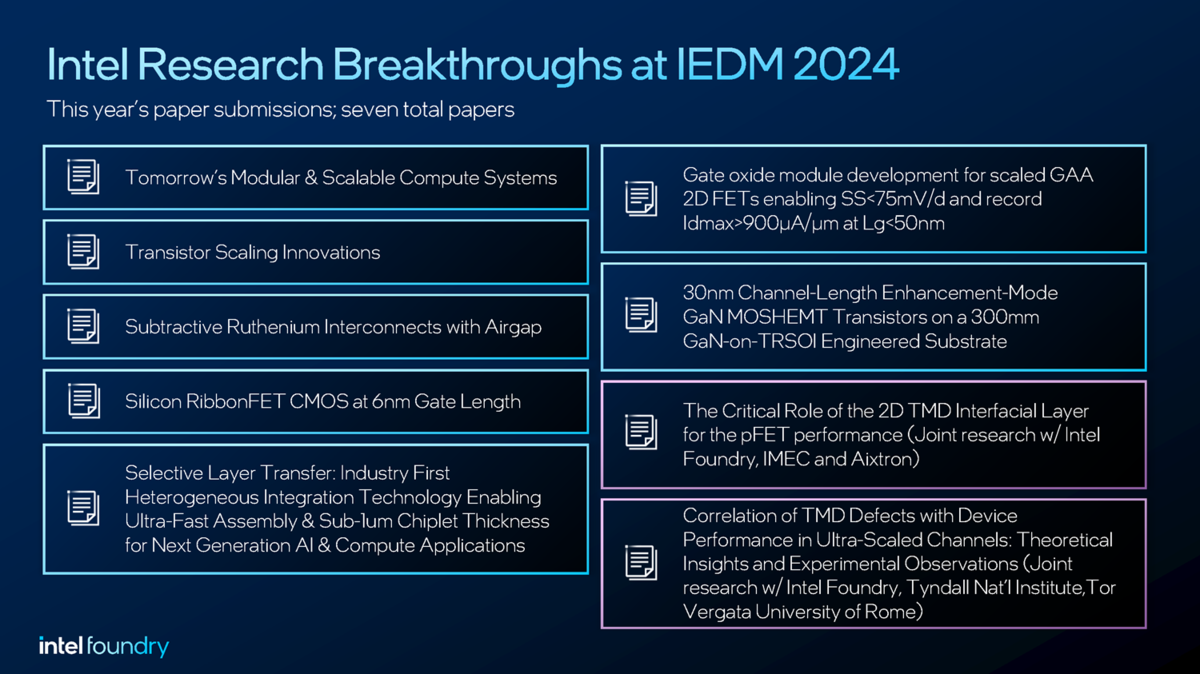

トランジスタの当面の目標は電圧を0.3V未満に抑えつつ動作効率を5倍以上に引き上げること IEDM 2024レポート

2024年12月23日 12時00分更新

電圧を0.3V未満に抑えて動作効率を5倍以上に引き上げつつ

性能は0.65V動作のトランジスタの半分程度まで引き上げるのが目標

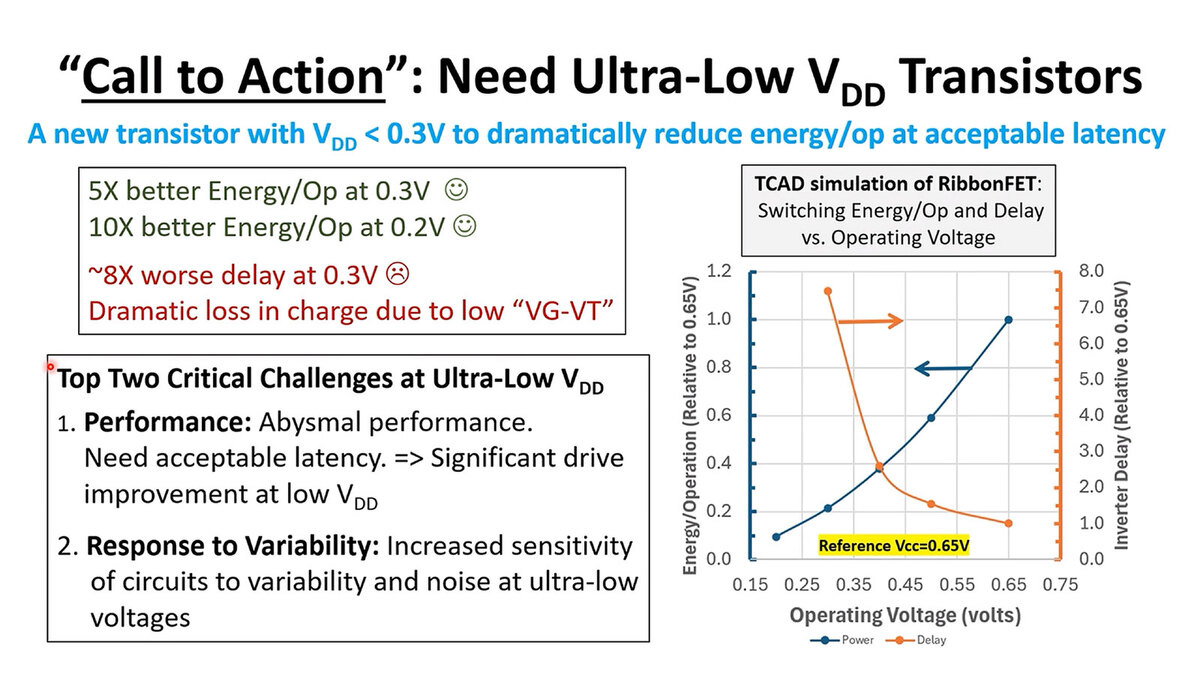

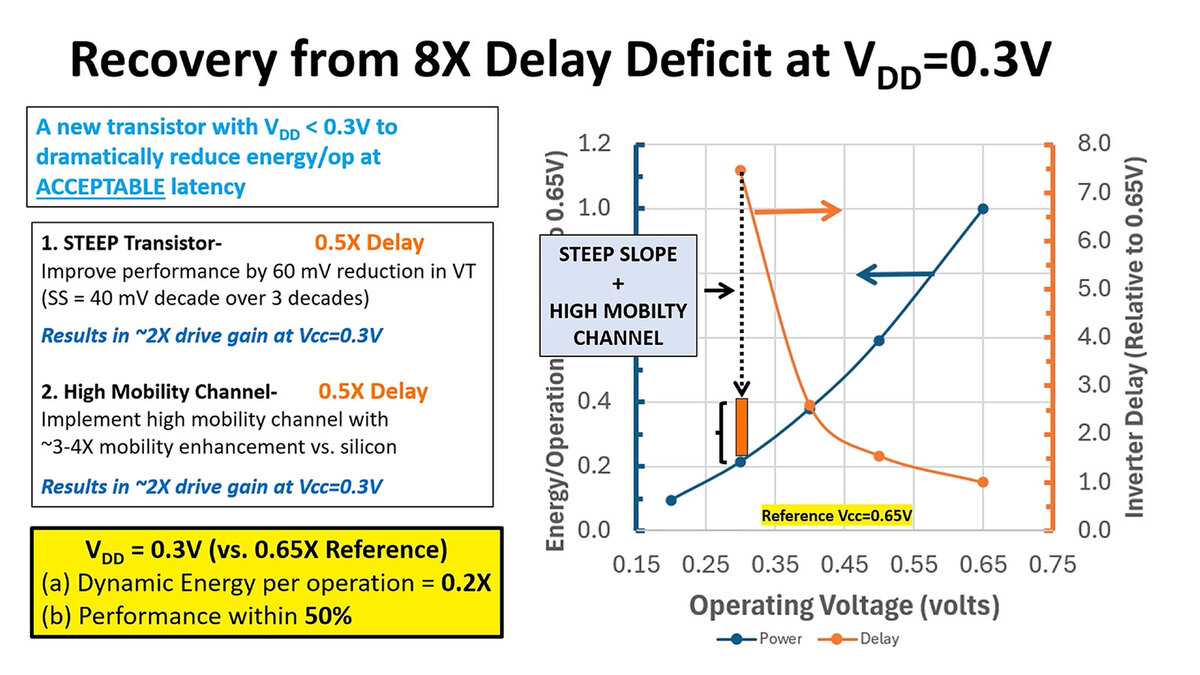

ただ、2030年を目指すにあたっては、単に面積の縮小だけでなく、消費電力と放熱の問題も解決する必要があるとする。まず消費電力にからむ話で、とにかく電圧を下げないことには消費電力が下がらないのだが、電圧を下げると同時にトランジスタの速度も大きく落ちてしまう。

0.6Vで動作するトランジスタを0.3Vまで落とすとエネルギー効率は5倍に向上するが、トランジスタのスイッチング速度が8分の1になってしまう。

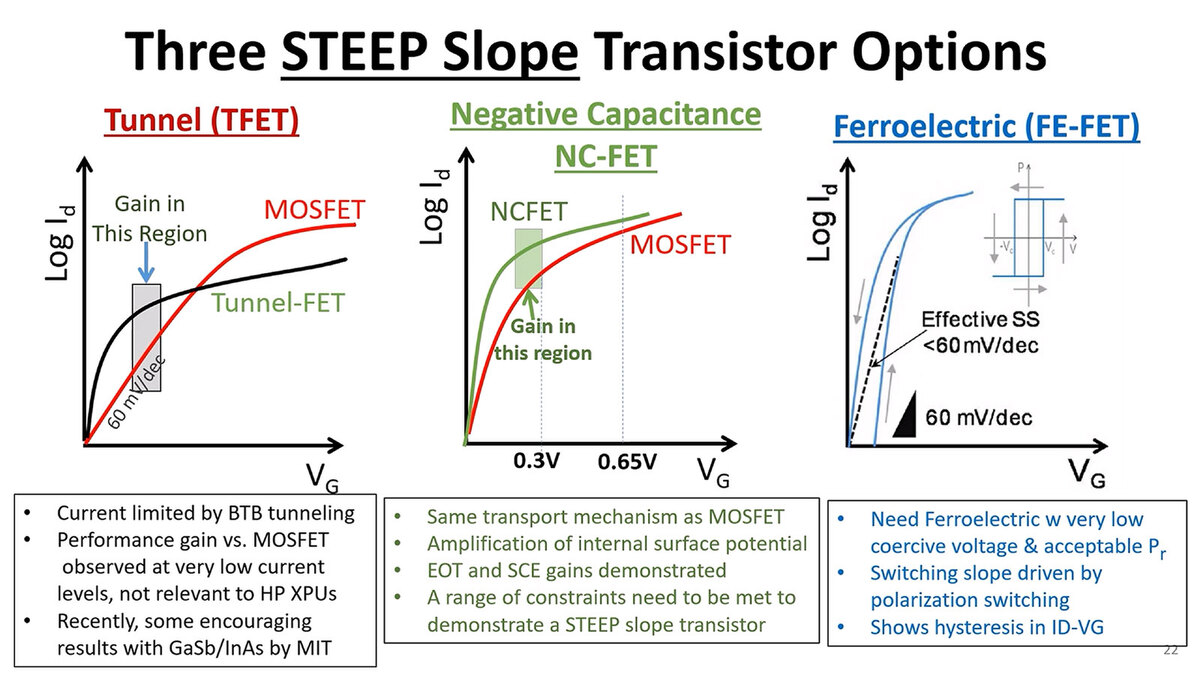

これを改善するトランジスタの構造をSteep Slope Transistorとして各社さまざまな技法を検討している。

トランジスタそのものが遅くなることそのものは仕方ないとして、その遅くなる程度を許容範囲内に抑えたい、というのが現在の目標になっている。また、電荷の移動速度を高速化する技法を併用することで、実用につなげたいというわけだ

そのSteep Slope Transistorの候補して現在はTunnel FET(トンネル効果を利用したトランジスタ)、Negative Capacitance FET(NC-FET:強誘電薄膜をゲート絶縁膜に利用することで、負の電界容量を持つ状態を作り出し、これを利用したトランジスタ)とFerroelectric FET(同様に強誘電体膜をゲート絶縁膜に用いる技法だが、Negative Capacitance FETとは異なる)の3つを候補として挙げている。

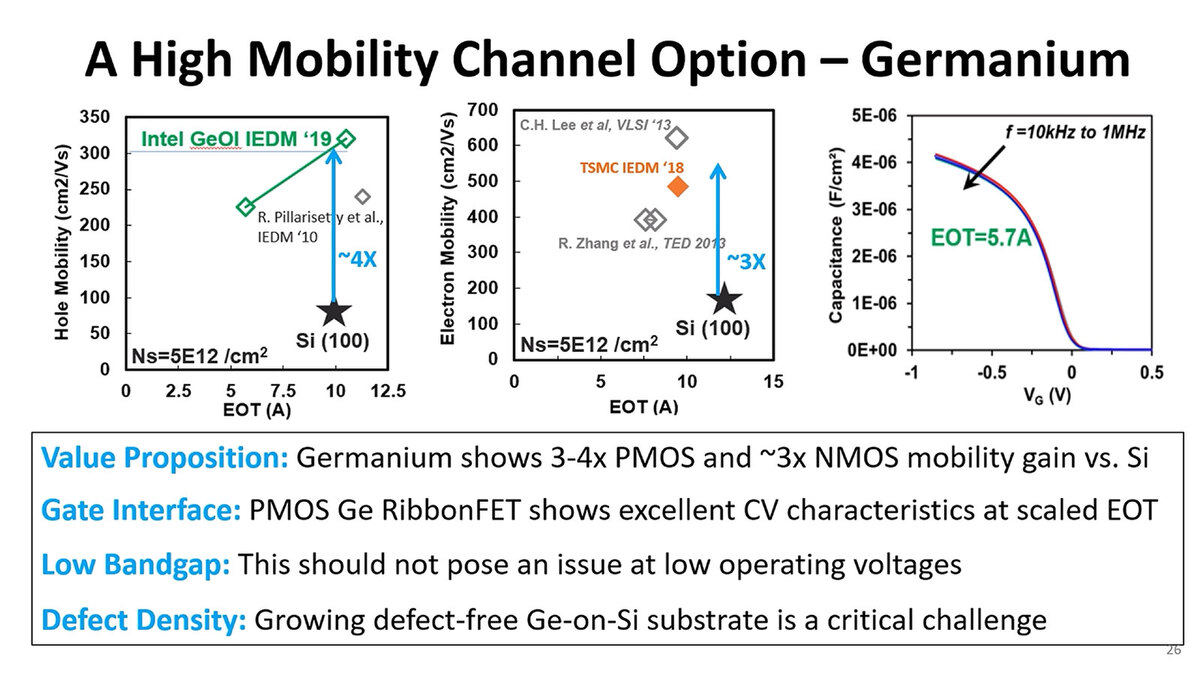

一方チャネルの電荷移動量の改善に関しては、シリコンをGe(ゲルマニウム)に変更することで、大幅に性能が改善される(PMOSで3~4倍、NMOSで3倍)ために有望である、としている。

これを組み合わせた、1つのビジョンが下の画像だ。電圧を0.3V未満に抑えて動作効率を5倍以上に引き上げつつ、性能は今の0.65V動作のトランジスタの半分程度まで引き上げることを目指している。

ただこれはトランジスタレベルでの改良であり、実際にはチップにする際にまた別の配慮が必要であるが、それは別の招待講演で説明されたので、次回はそちらをご紹介しよう。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります