第788回

Meteor Lakeを凌駕する性能のQualcomm「Oryon」 Hot Chips 2024で注目を浴びたオモシロCPU

2024年09月09日 12時00分更新

OryonのROBエントリー数は600以上!

インテルのSkymontに負けない規模の構成

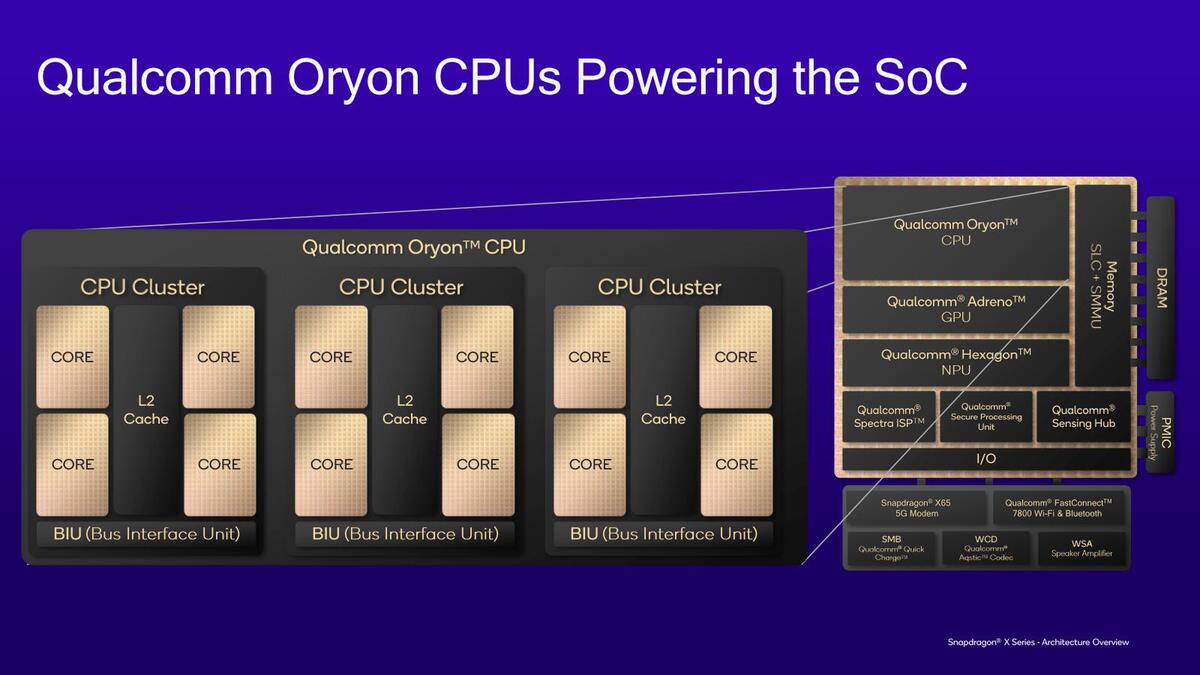

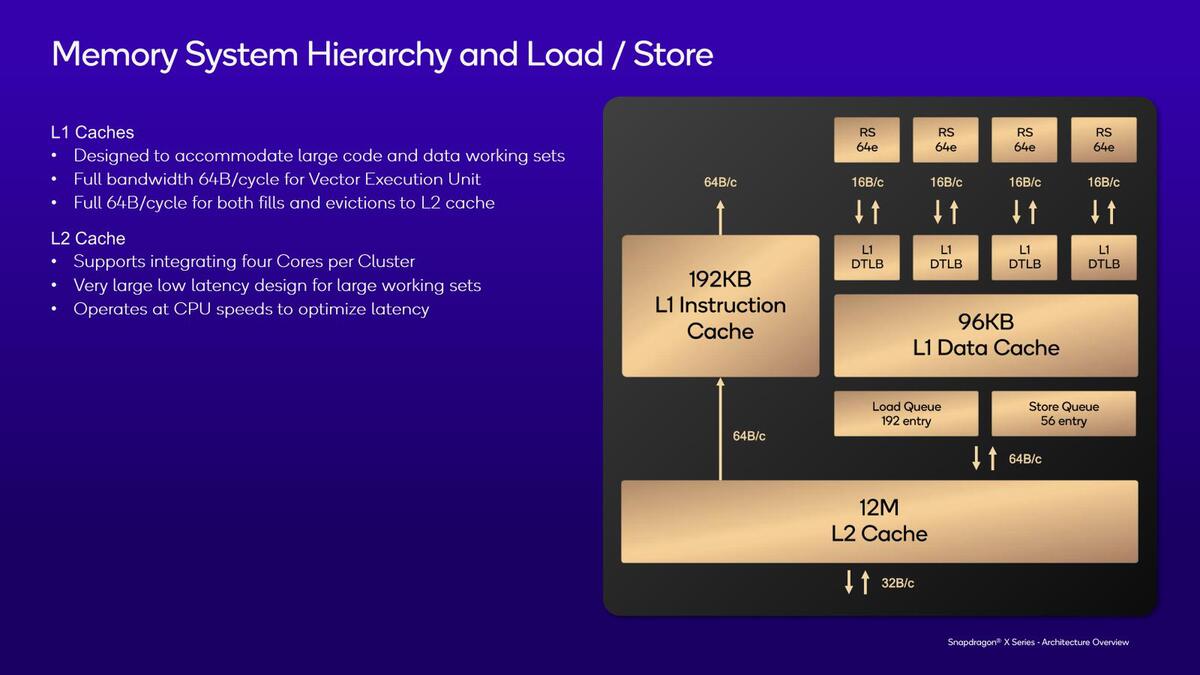

そんなOryonだが、基本は4コア単位のクラスターでの構成になるようで、2次キャッシュは4コアで共有になる。

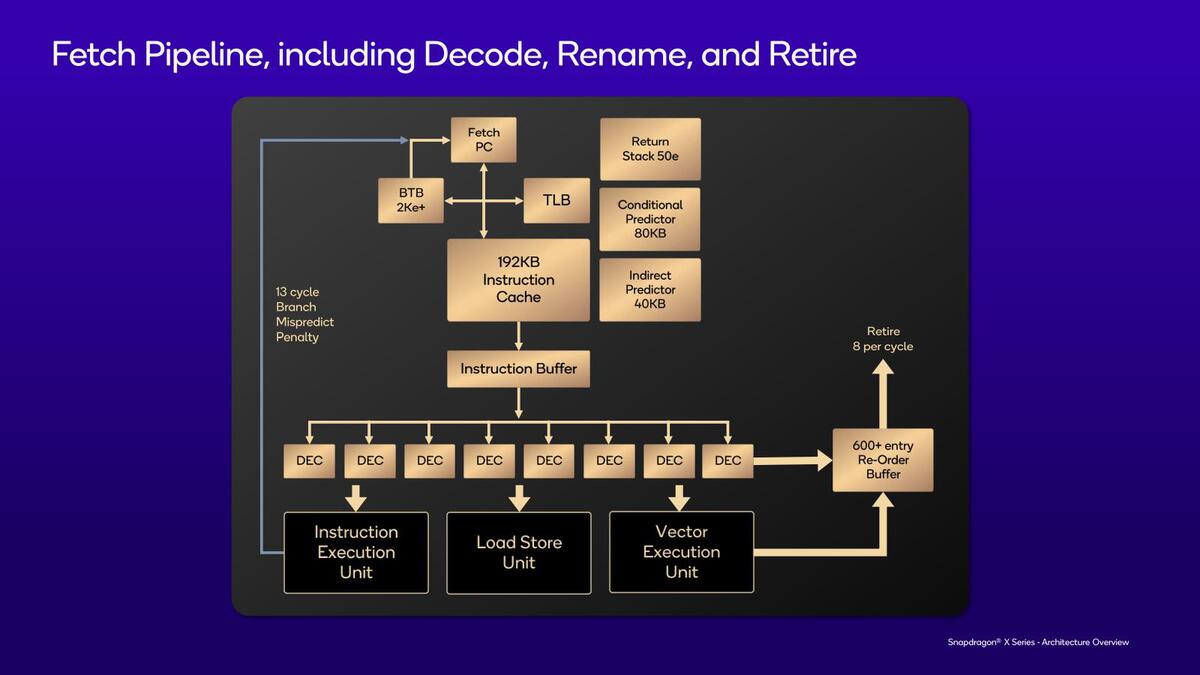

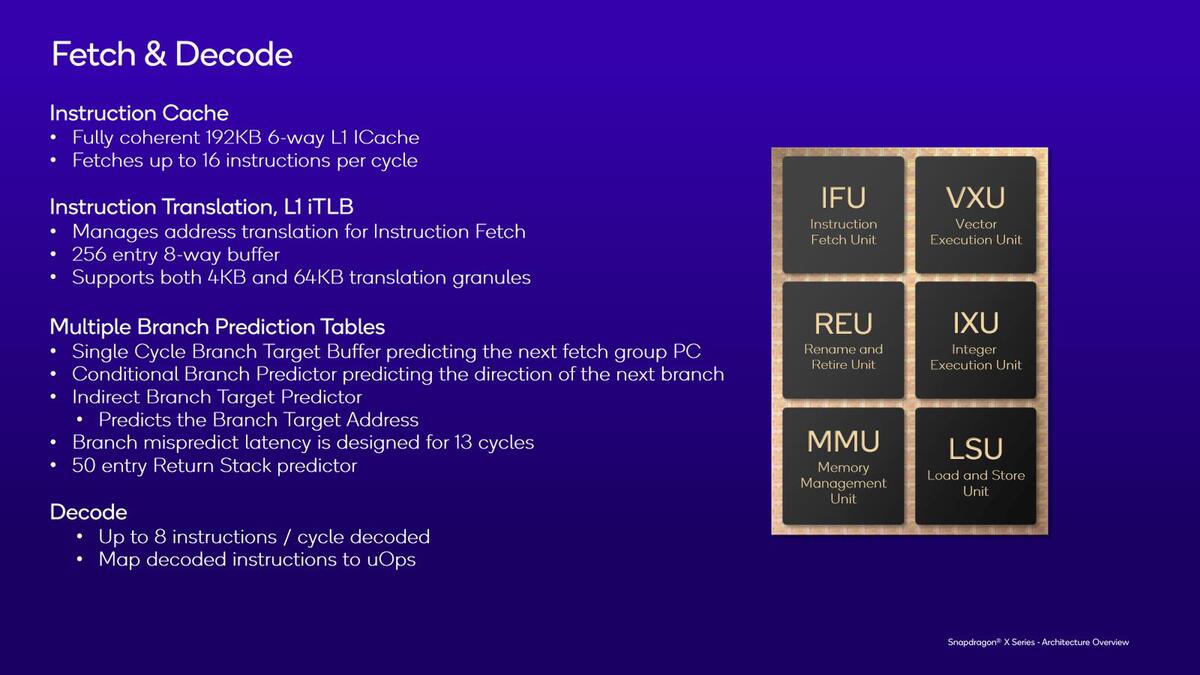

それぞれのコアの構成は下の画像のとおり。まずフロントエンドだが、8命令/サイクルのデコーダーと192KBのL1 I-Cache、強力な分岐予測と50ものRSP(Return Stack Predictor)と、インテルのSkymontに負けない規模の構成になっていることがここから大まかに見えてくる。

コアの構成。Cortex-X4は10命令/サイクルのデコード/ディスパッチ。Oryonはディスパッチが何命令/サイクルなのか未公表なのでなんとも言い難いが、ALUの数を考えればこの8命令で十分という気はする

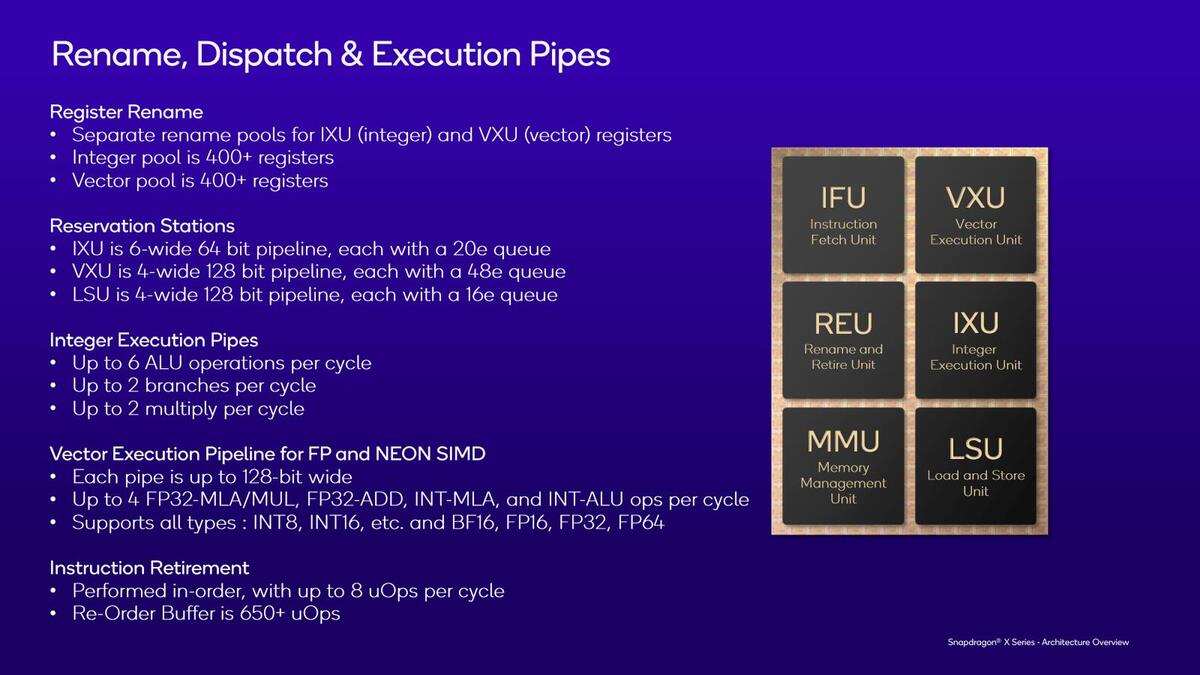

実際の構成を見ると、ROBのエントリー数が600以上(実際は650以上)というすさまじい数になっており、一体どれだけの数の命令をインフライト状態で保持しているのか? という疑問が湧いてくる量だ。

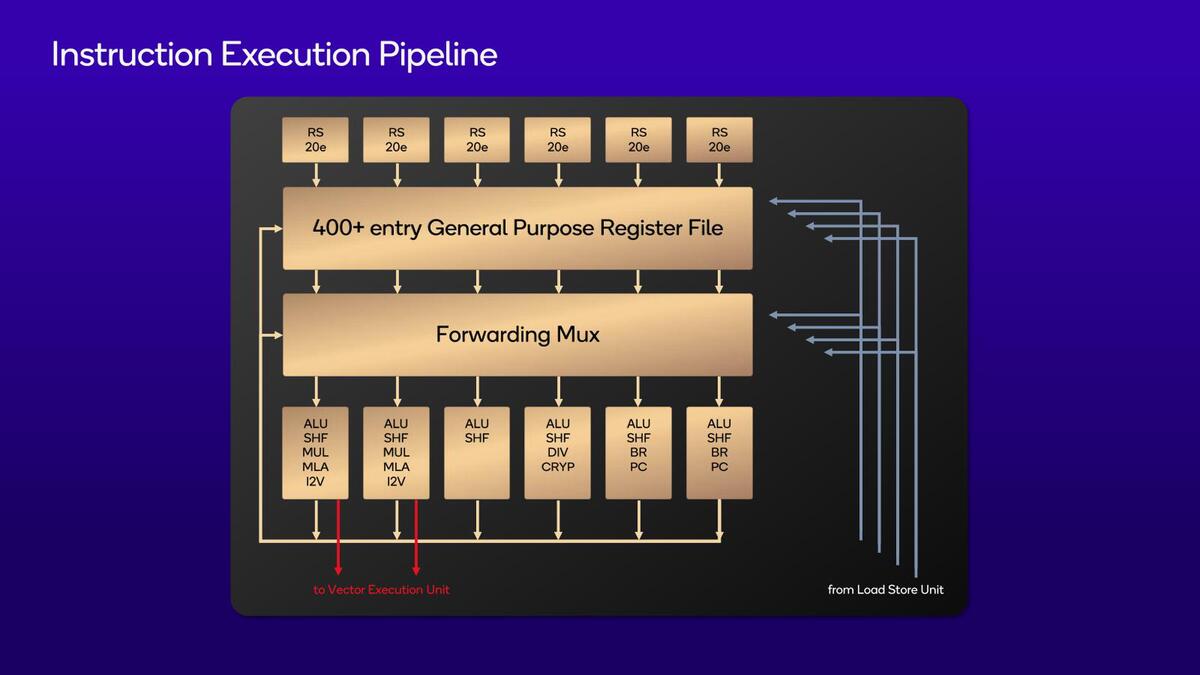

一方、バックエンドの方はALUこそ6命令/サイクルだが、分岐命令を2命令/サイクル実行でき、またレジスターファイルをALU/FPともに400以上というから、こちらも相当の命令をインフライト状態で保持できることがわかる。

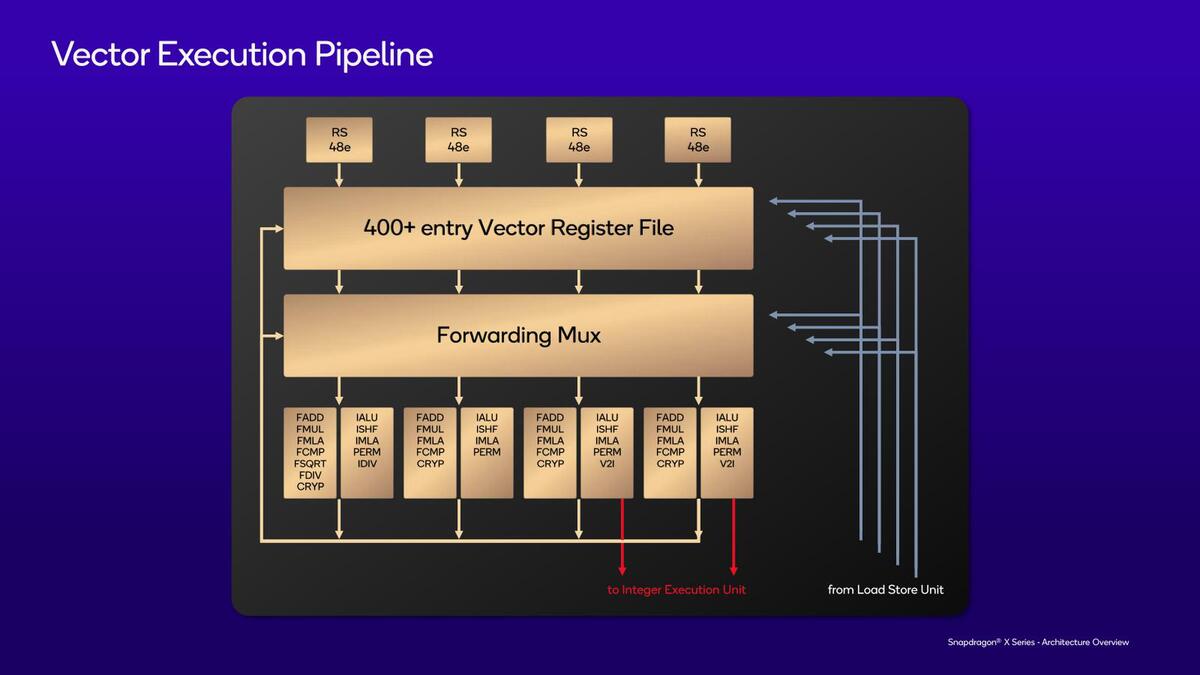

SVE/SVE2をサポートしないのは意図的という気もする。AI/ML用途以外では、SVE/SVE2を使うアプリケーションはごくわずかなのを勘案してのことかもしれないし、あるいは訴訟に絡む話も関係しているのかもしれない

またFPUに関して、SVE/SVE2には未サポートであるが、NEONを最大4つ実行できるというあたりはかなり強力な構成である。もう少し詳細にみると、Integerの側は下の画像のように6つのIssue portが用意され、おのおの20エントリーのRS(Reservation Station)が付く格好だ。左の2つのユニットのみVector Unitへのリンクがあるが、これはI2V(Integer to Vector)用と思われる。

同様にFP側は、Issue Portは4つだが、おのおの128bit幅である。ほぼ対称型(FDIV/IDIV/Cryptography/V2Iのみ違っている)なので、例えばもし将来それが必要と判断されたらSVE2を実装することは可能で、ただ現状では不要と判断されたように見える。RSもおのおの48エントリーなのでかなり多い。

全体として見ると、構成そのものはそれこそSkymontやCortex-X4にはややおよばず、CrestmontやCortex-X3などに近い。ただしCrestmontやCortex-X3に比べると、インフライトの形で保持できる命令数が明らかに増えているように思える。おそらく8つのALUをそこそこの利用率で使うより、6つのALUをギリギリまで使い切る方が効率が良いと判断したのであろう。

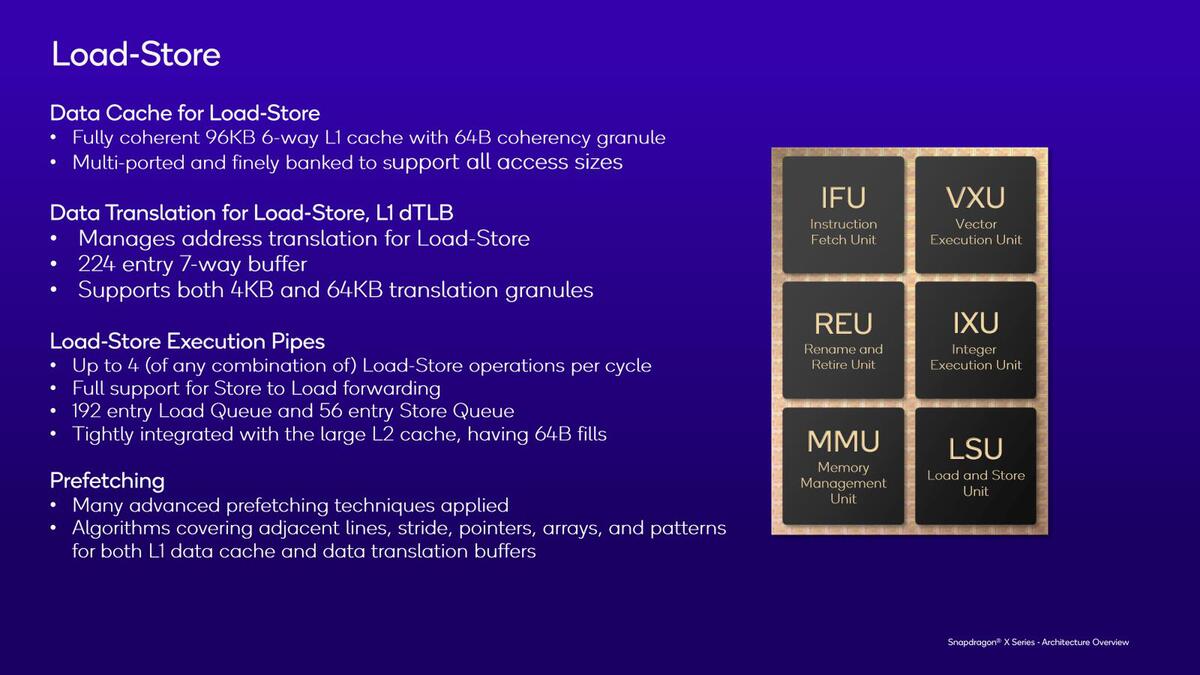

これを支えるロード/ストアーユニットであるが、L1 D-Cacheは96KB。ロード/ストアーユニットは4基用意されている。またL1 D-TLBが224エントリーというのは、これまでのQualcommのプロセッサーと比較すると少し多いが、これはターゲットがスマートフォンからPCに変わり、より大量のデータを扱うようになることへの対策なのかもしれない。

L1はインストラクション/データともに64Bytes/サイクルの帯域になり、L1/L2も64Bytes/サイクル、L2の先は32Bytes/サイクルになっている。L2は12MBと、これもQualcommのプロセッサーとしては大容量だが、4コアで共有(つまりコアあたり3MB)と考えると妥当な線なのかもしれない。

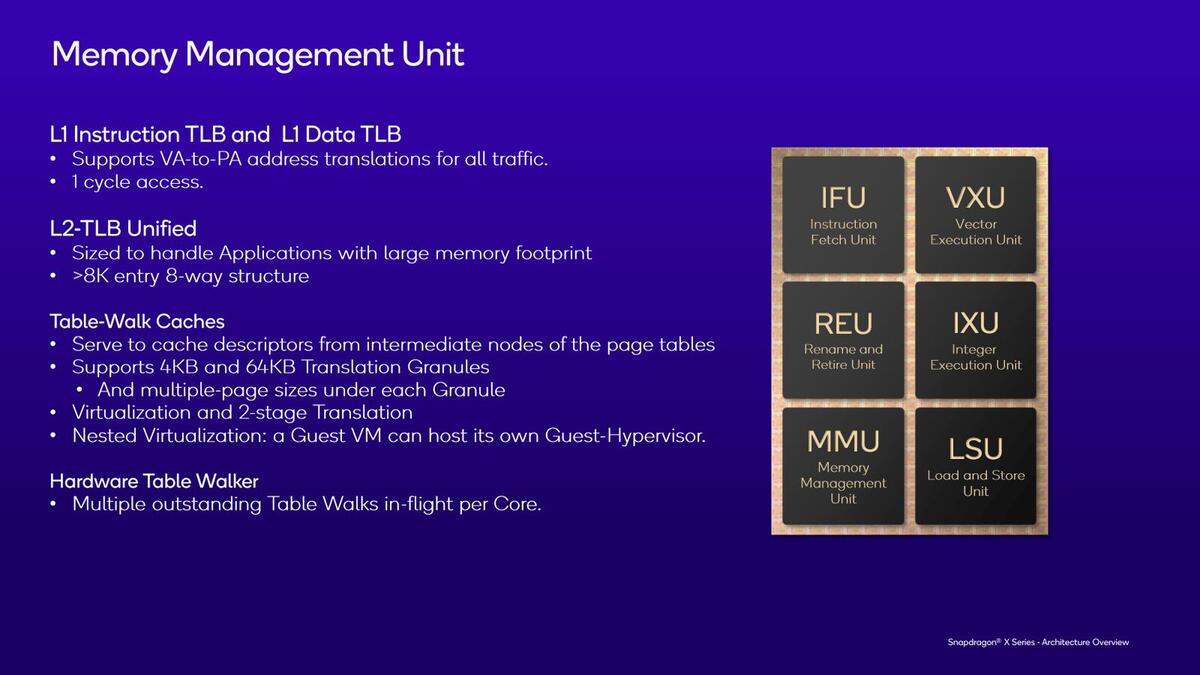

メモリー管理周りは、VMを多用することを考えてか、けっこう重厚な構成である。Table Walkを同時に複数発行できる、というあたりもスマートフォン向けというよりはPC向けのCPUという感じだ。興味深いのは、メモリーアクセスのGranularityが16bitなことで、このあたりはスマートフォン向けだと感じる。

メモリー管理周りの構成。さすがに1GB Tableは未対応の模様。64bit OSに対応といっても、Oryonのターゲットはモバイルなどの省電力向けなので、そこまで重厚な対応は不要と判断したのだろう。1サイクルで仮想アドレスから物理アドレスに変換などは、PC向けはできて当然というものだが、これまでのスマートフォン向けCPUは2~3サイクルが当たり前だった

※お詫びと訂正:記事初出時、命令の名称に誤りがありました。記事を訂正してお詫びします。(2024年9月11日)

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります