4月27日にインテルは2023年第1四半期の決算発表を行なった。売上は1170億ドル(約15兆8900億円)で、28億ドル(約3800億円)ほどの営業赤字を記録するといった大変な状況ではあるのだが、これは事前予測よりも良かったということで、むしろ株価がわずかながら上がる(29ドル→31.79ドル)という、おもしろい事態になっている。

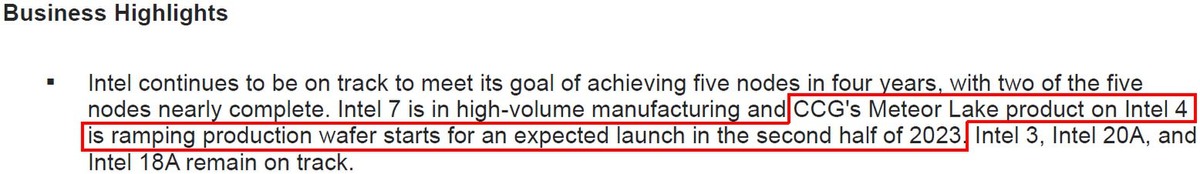

それはともかくとして、この決算発表のリリースの中にこんな一節がある。

赤線部が問題の箇所。Intel 7は“high-volume manufacturing”なのに、Intel 4は“ramping production wafer start”と控えめな表現なことをどう考えるか

表現を見る限り、まだフル稼働状態にはかなり遠い感はあるが、とにかくIntel 4を利用しての量産がスタートしたことを正式に表明した格好だ。5月30日から始まるCOMPUTEX TAIPEIでは、あるいはMeteor Lakeの動作プロトタイプにお目にかかれるかもしれない。そのMeteor Lakeの話がいろいろ流れてきたので、今週はまとめて説明したい。

特許取得で判明したMeteor Lakeの内部構造

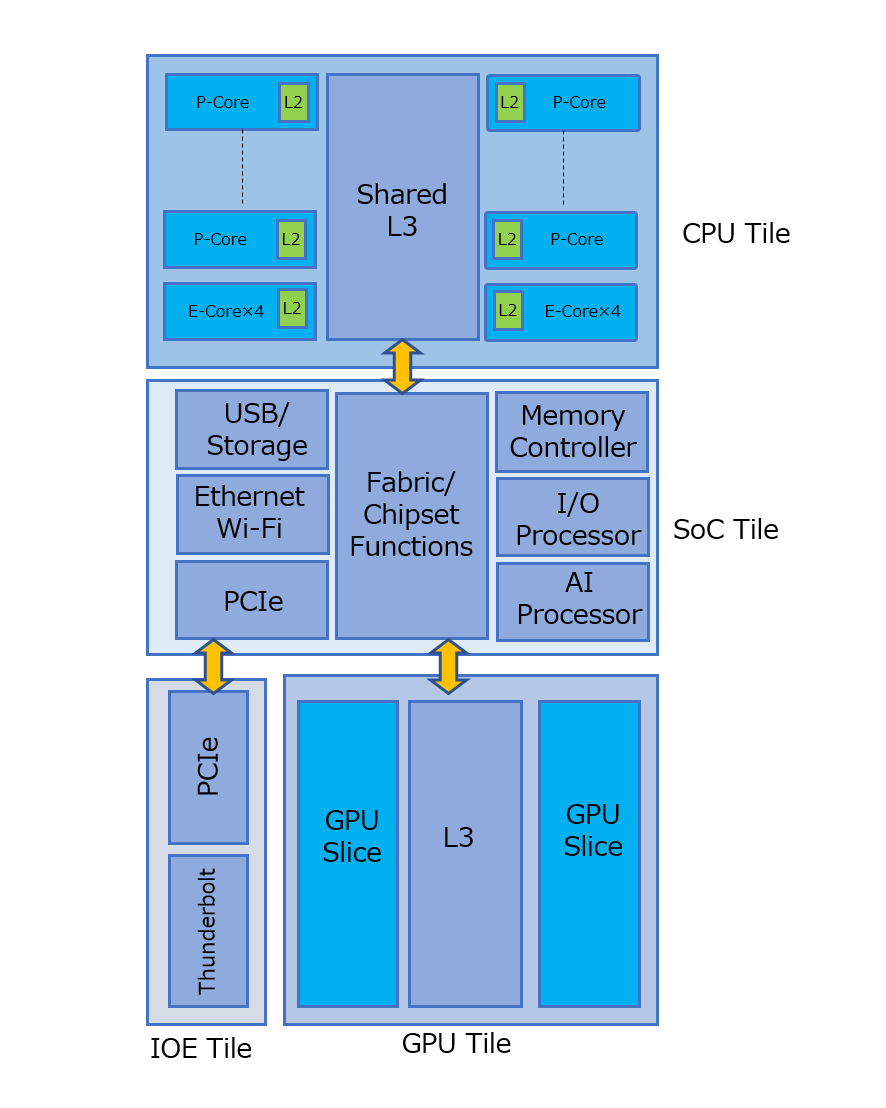

Meteor Lakeの内部構造の推定は、連載682回で解説したが、ひょんなところからこの内部構造が出てきた。ネタ元は米国特許US20210081538A1である。Google Patentsを見ると、2020年12月にまず米国で出願され、その後欧州/日本/中国でも出願されている。

発明者の筆頭はインテルのVincent Zimmer氏(Senior Principal Engineer)。タイトルは“Early platform hardening technology for slimmer and faster boot”で、要するにブートの際の時間を高速化するために、ハードウェアとファームウェアを協調動作させる手法に関するものである。

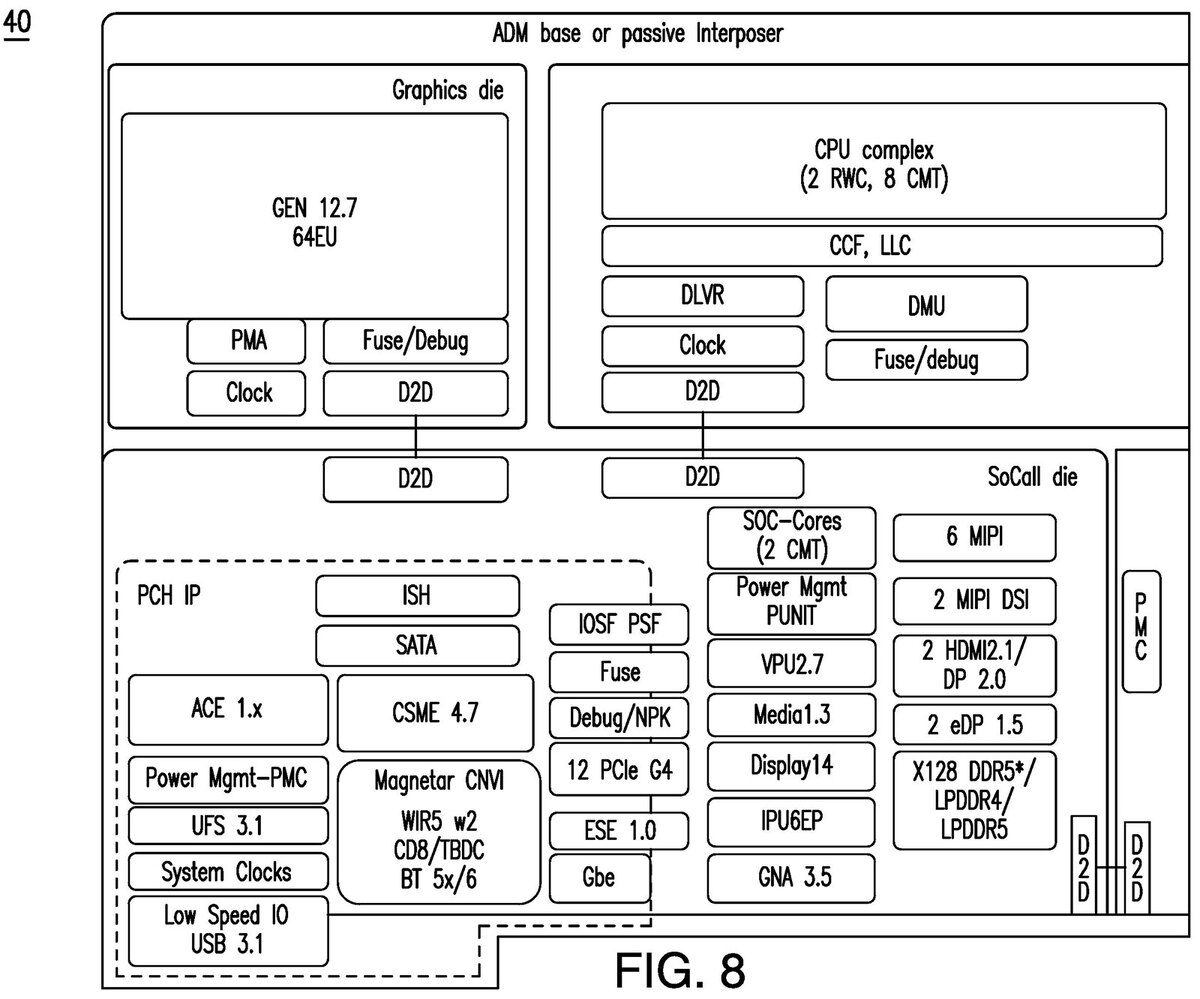

特にセキュア・ブートではどうしてもブート時間が長くなりがちであり、これを高速化するためのテクニックだ。この特許のFigure 8を見ると、これはどうみてもMeteor Lakeだな、と考えざるを得ない。

もっともこれはトップエンドモデルではなく、ディスクリート・グラフィックス用のPCIeも省き、またP-Coreは2つのみなので、U/Y SKU向けのものと思われる。

まず右上のCPU complexはRWC(RedWood Cove)×2とCMT(Crestmont)×8という構成。RedWood CoveはRaptor Coveの延長にあるコアで、大きなアーキテクチャー上の変更はない模様。一方のCrestmontはTremontの延長にあるGracemontと異なり、アーキテクチャーを刷新したとされているが、こちらも詳細は不明なままである。こちらの分析は後ほど。あと、LLCはSoCダイではなくこのCPUダイに搭載されている。

次いでグラフィックス・ダイ。こちらにはGen 12.7で64EUの構成のものが搭載される。このGen 12.7ってなに? という話だが、扱いとしてはIntel DG2に属するものになる。

要するにAlchemist世代のGPUだ。Alchemist世代ではXe-Core1個あたり16EUなので、これは4 Xe-Coreということになる。Intel Arc A380の半分であるが、統合GPUで専用メモリーを持たないことを考えれば、これ以上強化しても性能向上は見込みにくいだろうから、妥当な構成と思われる。

ちなみに以前の想像図ではGPUダイに3次キャッシュを入れておいたのだが、これを見ると3次キャッシュがない(CPU タイルの方にはLLCの表記があるので、ここに3次キャッシュが入っていると考えられる)。全SKUでLLCがなしなのかどうかまでは正直判断できない。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります