ARMの新マルチコア技術「DynamIQ」 「AIの可能性を拡大」はあくまでもたらされる結果

2017年03月24日 10時00分更新

英ARM社は、3月21日、中国北京で発表会を開催、DynamIQと呼ばれる新技術について発表を行なった。発表を行ったのは、ARM社副社長兼コンピュートプロダクト事業部部長のナンダン・ナヤンパリー氏だ。

DynamIQには、複数の要素が含まれる。具体的には

・新しいマルチコア構成

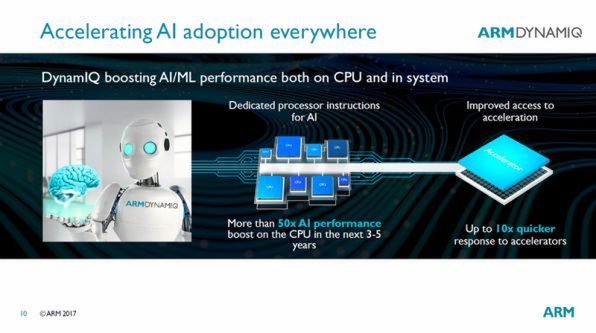

・ARMv8用の新命令

の2つが含まれている。プレスリリースなどに表現されている「AIの可能性を拡大」という部分は、AI用の新規命令による高速化と新しいマルチコア構成による高速化の2つが合わさった“効果”であり、DyamIQの新命令以外の部分はAIに特化したものではない。またDynamICは、現時点ではCortex-A用のもので、Cortex-Mシリーズなどには関係がない。

次世代のCortex-Aプロセッサではマルチコアに変化

最大8つのコアや高性能なコアのみの構成が可能

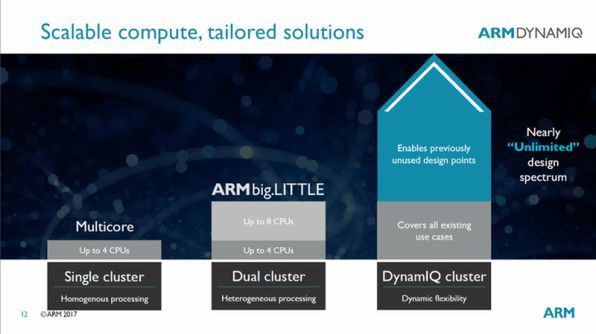

しかし、この発表で最も重要な部分は、マルチコア構成が変わることだ。従来のCortex-Aプロセッサは、Cortex-A9で導入されたマルチコア技術をベースに発展してきた。ARMのマルチコアは「クラスター」と呼ばれ最大4個のコアを1組として1つのクラスターを構成する。Cortex-A9でこのクラスター構成が可能になった。

その次の段階として、高性能なプロセッサと高い電力効率を持つプロセッサを組みあわせて使う「big.LITTLE」プロセッシングが導入された。このとき、big側、LITTLE側をそれぞれクラスターとする。つまりbig.LITTLEは2つのクラスターで構成される。

このため、最大で8つのプロセッサを、1クラスター最大4コアの2つのクラスターで構成する。クラスターを分けるのは、マルチコアとしてクラスター内で組みあわせることができるのは同種のコアに限られているからだ。

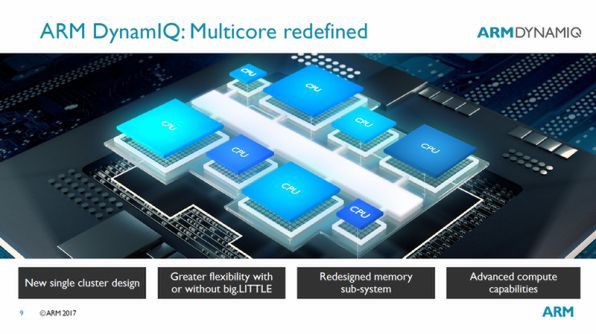

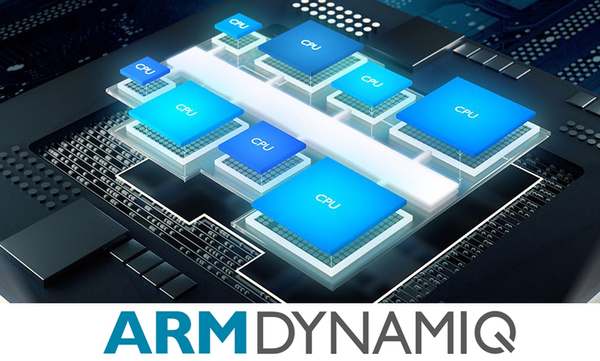

今回発表されたDynamIQは、このクラスターの構成をまったく新しいものに置き換えた。

1クラスターには、最大で8つの異なる種類のコアを配置できる。

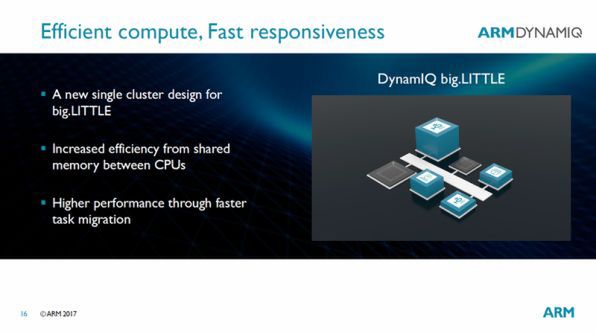

また、big.LITTLEのようなプロセッサの性能や電力効率によるタスクの自動切り替えをクラスター内で行うことが可能になった。このため、1クラスターで最大8つという範囲内で、bit側、LITTLE側のコアを自由に組みあわせることが可能になった。

スマートフォン以外の用途、特にサーバー向けなどを考慮し、LITTLEコアを含まない、高性能コアのみでクラスターを構成することも可能になった。クラスターはL2やメモリアクセスの単位でもあり、DynamIQでは、メモリサブシステムを新しいものとして、自動電力管理機能などを組み込む。

電力管理機構を改良して

さらに効率のいいプロセッサの開発が可能に

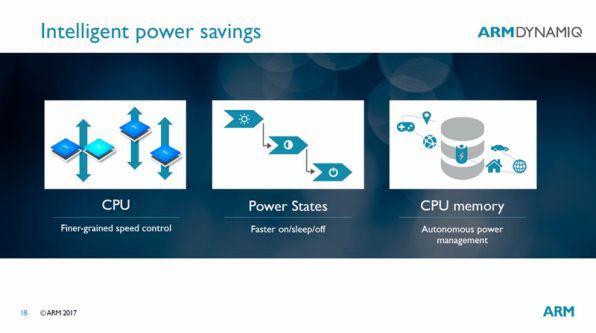

また、クラスター内のコアの電力管理機構を改良して、従来よりも、高速な、クロックや電圧の変更、コア状態(電源オフ、スリープ、電源オン)の切り替えを可能にする。

クロックや電圧の変更は、負荷に応じて、処理速度を切り替えるもの。高いクロックのときには、高い電源電圧が必要になるが、クロックを落とせば、電源電圧も下げることができ、より消費電力を小さくすることができる。これは、ハードウェアで制御されるため、ソフトウェアよりも高速な切り替えが可能だ。

こうした新しいクラスタ構成により、ARMプロセッサは、より高い電力効率で動作でき、また、より高速に動作できるようになる。ただし、DynamIQに対応するのは、現時点では未発表のCortex-Aプロセッサであり、既存のプロセッサがDynamIQに対応するわけではない。

現時点では、クラスター構成が改良され、より高速化が可能になるということだけが発表されており、新プロセッサコアやクラスター間接続の内部バスなどについては、今後、具体的な製品が発表されていくことになると思われる。

今回の発表は、DynamIQというマルチコア技術の発表であり、AIやMRといったものは、高速化などの結果として表れるものにすぎない。ARMがDynamIQで行おうとしているのは、マルチコア(クラスター)を改良し、より高い性能で電力効率の高いプロセッサコアを投入できるようにすることだ。重要な技術ではあるが、これ自体は理解しやすいものでもない。

今回の発表で一番理解しやすい部分は、新命令の追加によりAI処理が高速化する部分。この部分を強調しすぎたため、プレスリースなどがあのような記載になってしまったようだ。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります