第870回

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか?

2026年04月06日 12時00分更新

DDR5-8800か、それとも容量か

AGI CPUのメモリー仕様に見えるトレードオフ

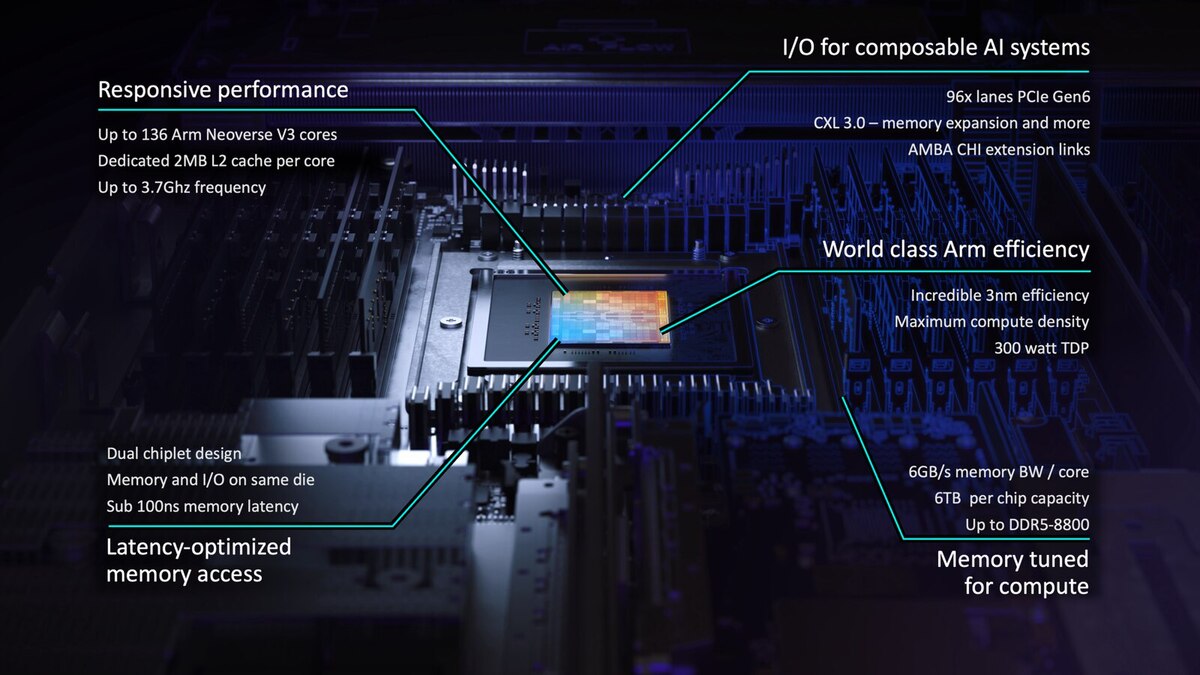

現時点で示されているAGI CPUのスペックは以下のとおり。

ベースとなるのはNeoverse V3で、これがトータル136個。それぞれ2MBの2次キャッシュが搭載され、動作周波数は最大3.7GHzである。TSMCの3nm(N3なのかN3Pなのかは判断できない)という動作周波数を考えるとそれほど高速とはいえないが、その代わりにTDPは300Wとコア数のわりには低めに抑えられているのがわかる。

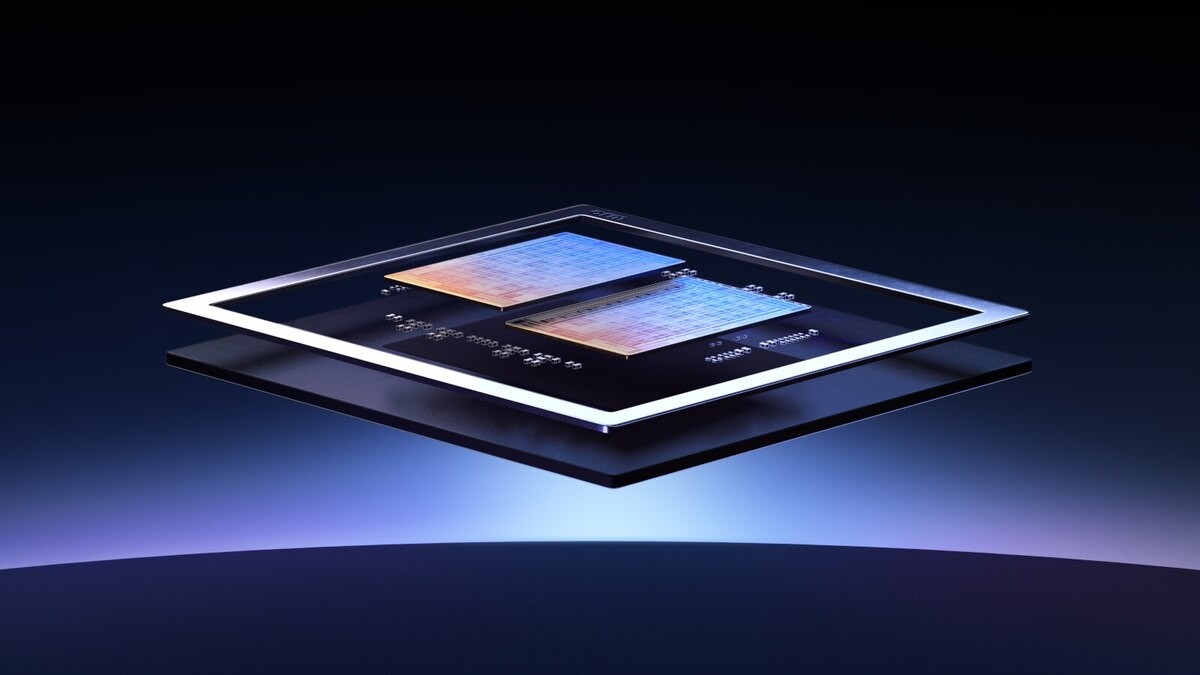

全体は2つのダイからなるチップレット構成になっており、同じダイを180度反転させて接続する構図になっている。

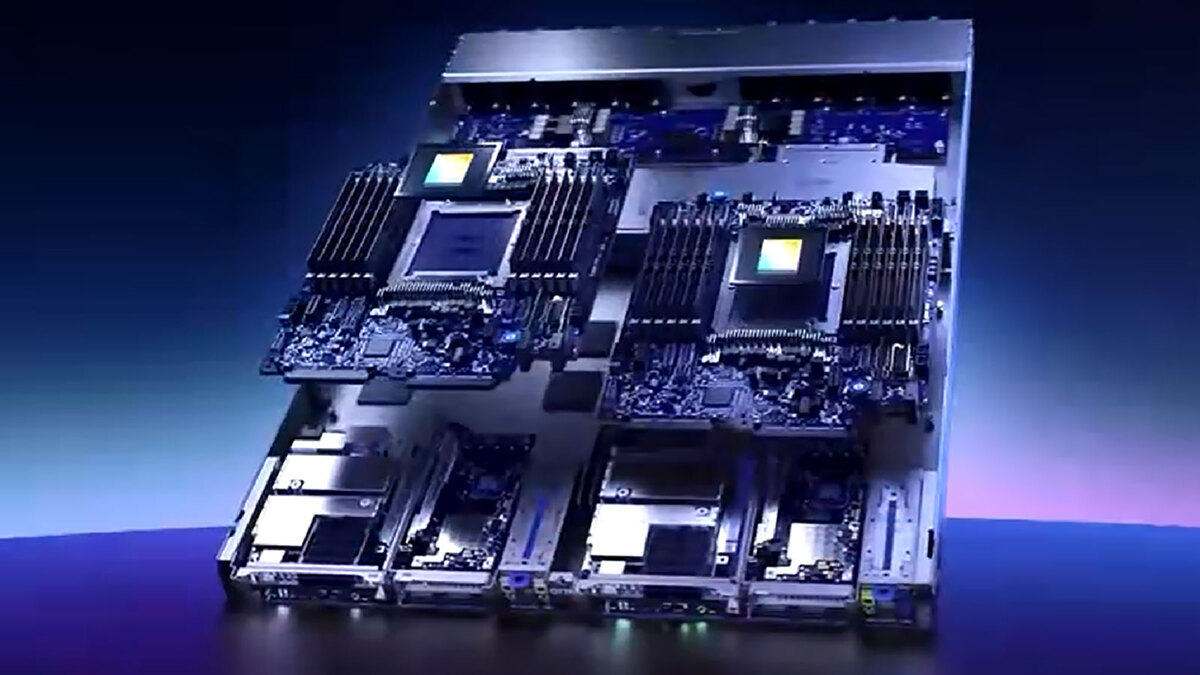

中身の話はこの後するとして、機器構成例として示されたのが下の画像だ。ここからみるとAGI CPUは1チップあたりDDR5を12チャンネル搭載する構成になっているようだ。

ただここで問題なのが、このページ最初の画像で"6TB per chip capacity"とされていることで、6TB÷12枚=512GB/枚のDIMMを使うことになるのだが、現実問題としてそんなDIMMは存在しない。筆者が思うに2つ上の画像にあるキャリアボードは速度優先構成で1DIMM/チャンネル構成になっており、最大容量は256GB×12=3TBだが、最大DDR5-8800まで利用可能である。

一方、2つ上の画像とは別に2DIMM/チャンネル構成のキャリアボードも存在し、こちらのケースでは256GB×24=6TBが可能であるが、速度はDDR5-4400やDDR5-4000程度に抑えられてしまうだろう。仕様上は2DIMM/チャンネルも可能だが、普通に提供されるのは1DIMM/チャンネルのキャリアボードのみで、顧客から要望があったら2DIMM/チャンネルのキャリアボードも提供可能という程度の扱いかもしれない。

ちなみに扱えるのはあくまでもスタンダードDDR5のみで、MRDIMMやLPDDR5xベースのLPCAMM2などには対応しない(できない)という話であった。

拡張性に一抹の不安?

PCIe Gen6 96レーンとCXL 3.0サポートの評価

次にインターコネクトであるが、PCIe Gen6を96レーン搭載し、CXL 3.0をサポートするところまではいいが、96レーンというのはこのクラスのCPUとしては少し物足りないところだ。特にCXLを利用したメモリー拡張を想定しているならばすぐ足りなくなりそうだ。

それはともかくとして、謎なのがしれっと追加されている"AMBA CHI extension link"である。AMBAというのは"Advanced Microcontroller Bus Architecture"(大昔は"ARM Microcontroller Bus Architecture"の略だったが途中で変更された)というもので、本来はSoC内部のブロック(CPUブロックやメモリーコントローラーなど)同士を接続するインターコネクト用のI/F仕様とプロトコルを定義するものである。

そしてCHIはCoherence Hub Interfaceの略で、そのAMBAの上でキャッシュコヒーレンシを取るためのプロトコルである。これは結構広く利用されており、例えば連載843回で説明しているNVIDIAのGB10は、CPUダイレットとGPUダイレットの間をNVLinkで接続する格好だが、物理的にはUCIeの上にAMBA CHIを通し、その上にNVLinkのプロトコルを載せる格好になっている。

もっといえば、連載838回で説明したNVLink Fusionも、AMBA CHIの上にNVLinkを通す仕組みになっている。ただAMBAは先程も書いたようにSoC内部の接続用であり、最近はチップレット間を接続できるようなところまで拡張はされているが、チップ外部に配線を引き出せるような構造にはなっていない。この"extension links"なるものが物理的にどういう形で実装されるのか、現状さっぱり判断できないところだ。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります