第868回

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価

2026年03月23日 12時00分更新

寿命マージンを性能に転換!

DMPAと劣化抑制のメカニズム

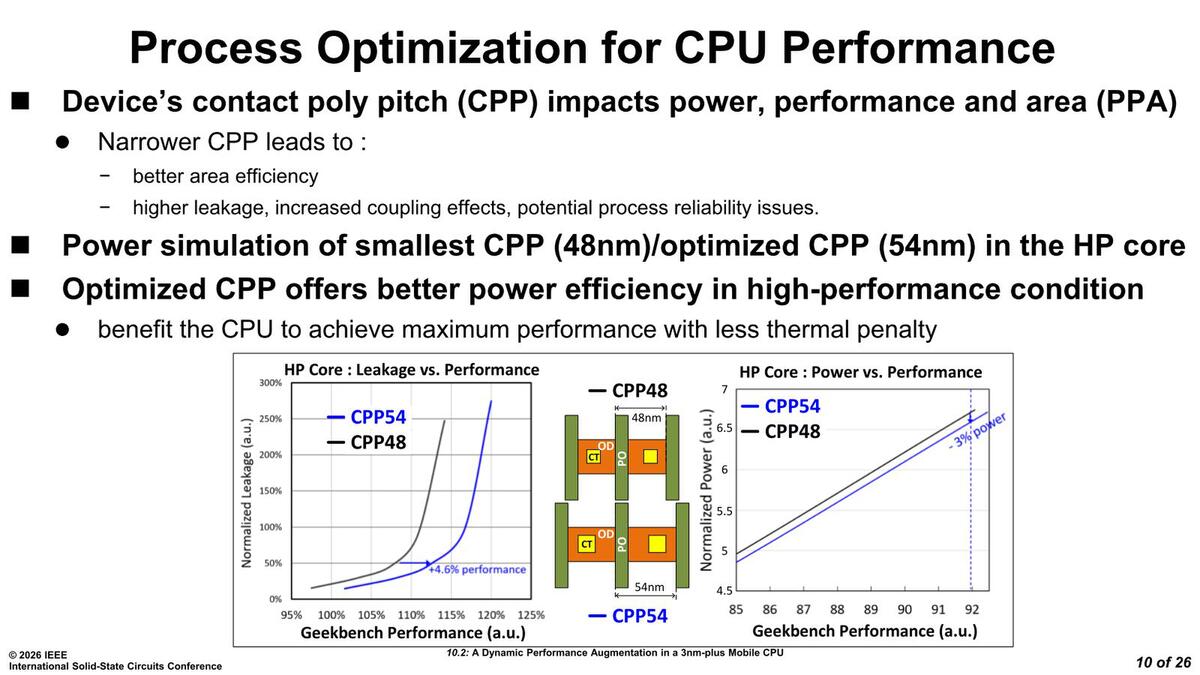

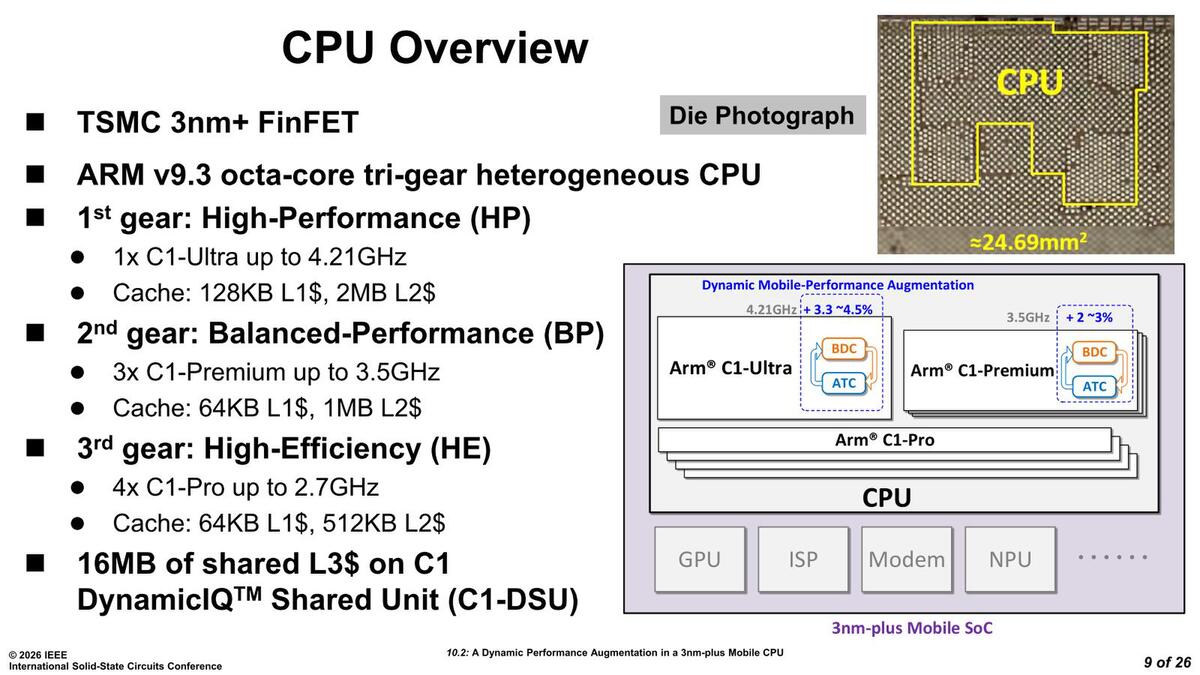

Dimensity 9500の概略が下の画像である。C1-ProにはDMPAが実装されておらず、C1-UltraとC1-PremiumにのみDMPAが実装されているとわかる。DMPAによる効果はコアによって異なるが、3%台の向上は無視できない数字だろう。

Dimensity 9500の概略。サイズは、ほぼ25mm2。8コアとしては小さいのだろうが、半分はC1-Proが占めていることを考えると、C1-Ultra/C1-Premiumは相応の大きさなのだろうと推定できる

次がプロセスの話で、C1-UltraについてCPP48とCPP54を比較したところ、密度という意味ではCPP54の方が高くできるのだが、同一リーク時の性能、あるいは同一周波数における消費電力ではCPP54の方が優秀で、CPP54を選択したとしている。

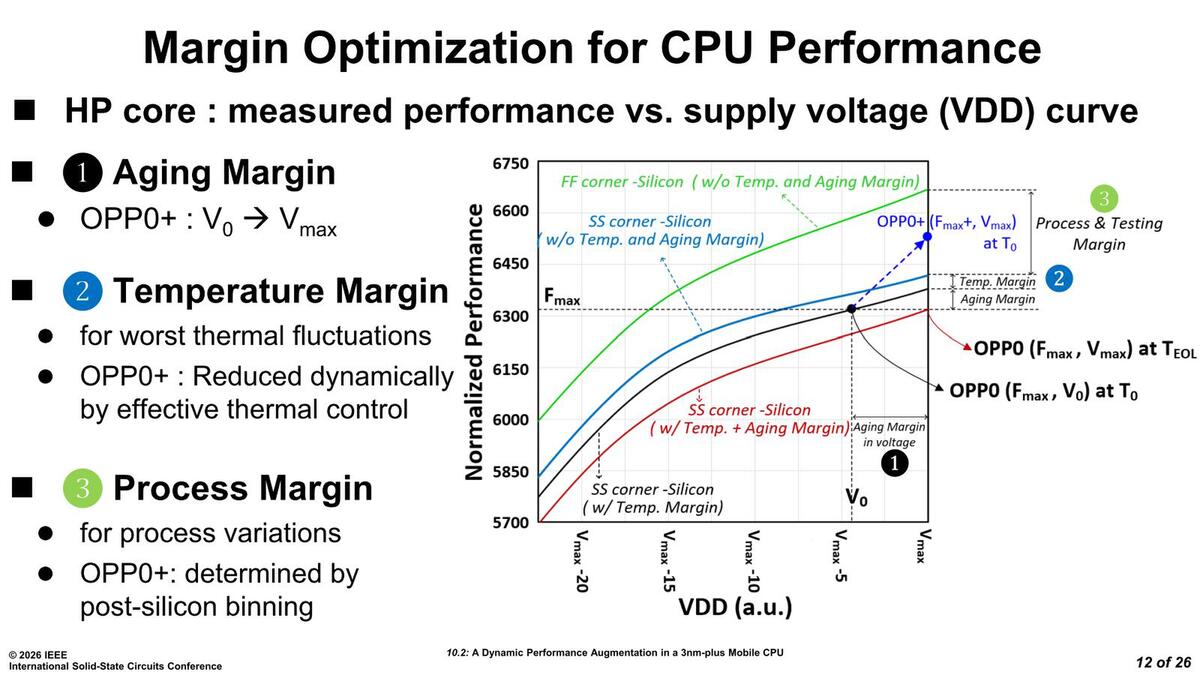

さて、DMPAに入るための基本が下の画像だ。グラフの縦軸がGeekBenchのスコア、横軸が駆動電圧である。赤が最悪値の状態で、これ以下に下がることはないカーブ、黒が設計値、青が温度のマージンを全部使った場合、緑が寿命のマージンを全部使った場合のグラフとなる。

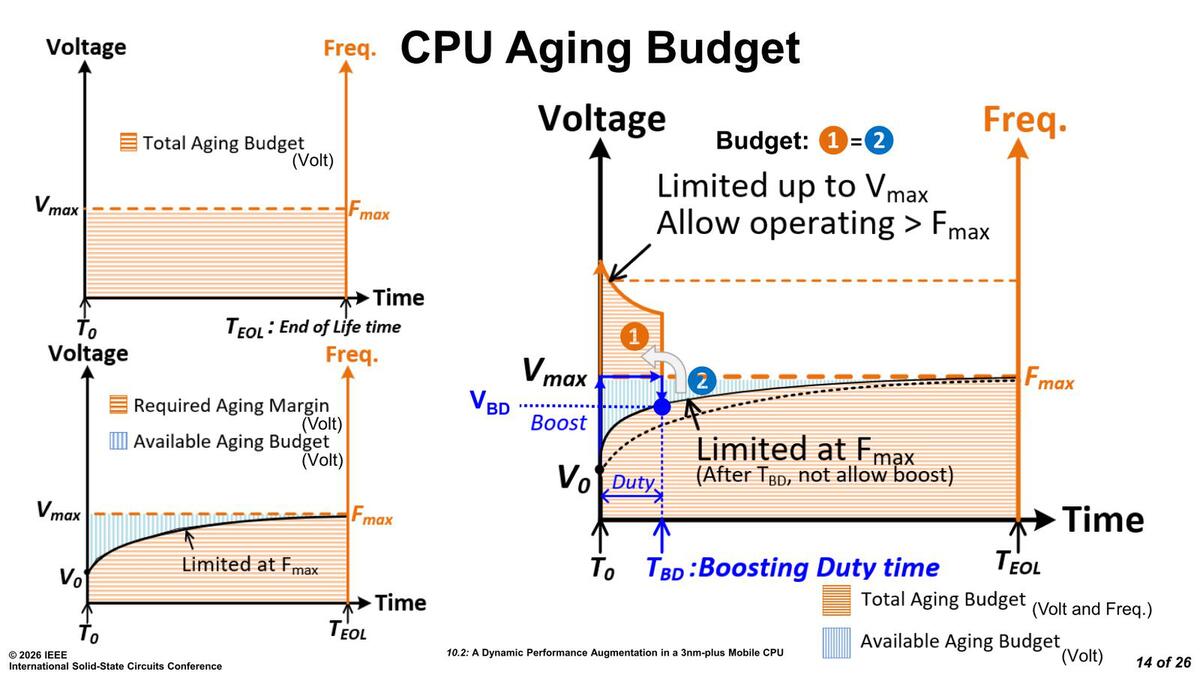

ではDPMAはどう動くか? というのが下の画像だ。現在T0(初期時間)にいて、そこで電圧(と動作周波数)は最大値より低い。ここで電圧をVmaxに引き上げると、しばらく時間をかけて(TEOL-T0)から動作周波数は最大値(Fmax)に到達する(黒点線)。

当然これは緩やかなカーブとなる。そこで、一時的にであるがVmaxを超える電圧をかけることで、より早く動作周波数がFmaxに到達するようになる。この一時的にVmaxを超えた分の電圧×時間(図中①)と、T0~TEOLの間のマージン分(図中②)を同じにする、ということで劣化の加速を抑えようという仕組みだ。

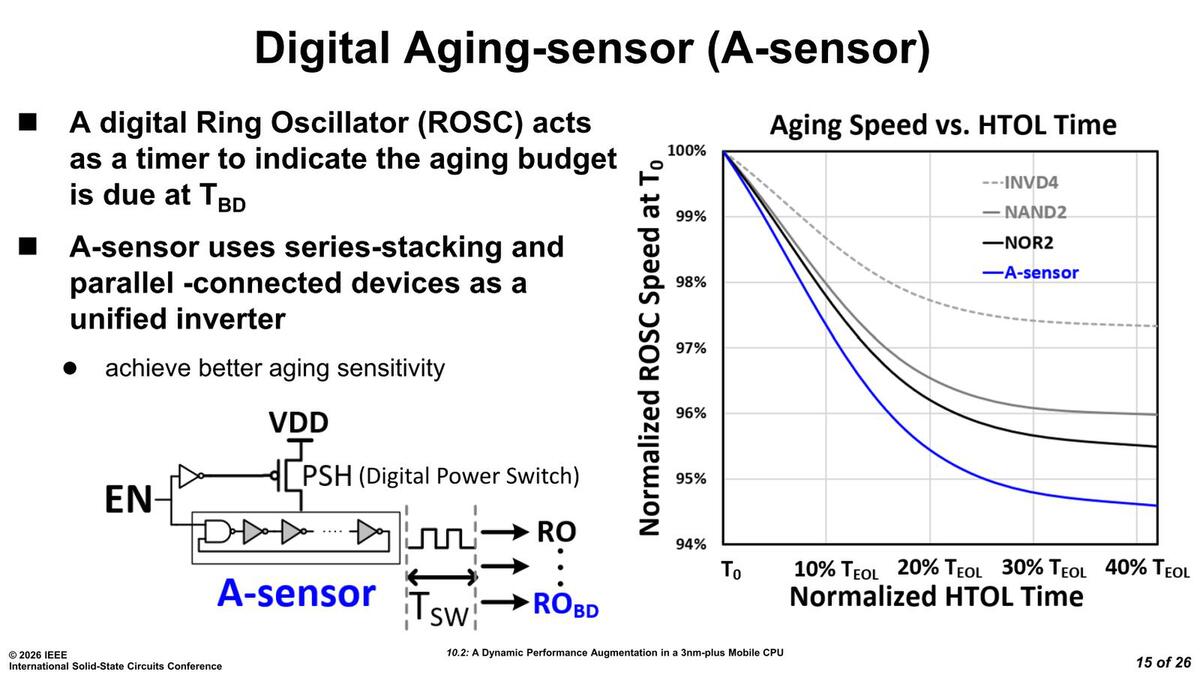

これを実行すると、予期せぬ形でシリコンの劣化が加速する可能性がある。そこで劣化具合を確認するためのAging-sensor(A-sensor)を搭載する。

グラフの横軸のHOTLはHigh-Temperature Operating Lifeの略。縦軸がRing Oscillatorの動作速度であり、動作速度が定格から5.5%程落ちるとほぼ寿命の40%近くを消費していることになる。このあたりはデバイスによっても異なり、インバータ4つやNAND2つ/NOR2つなどではそこまで速度が落ちない。Ring Oscillatorを使う方が検出が容易になる

といっても本来シリコンの劣化具合というのは分解して断面写真でも撮らないとわからない(その際にSEMやTEMが使われるわけだ)ので、疑似的にRing Oscillatorを利用している。Ring Oscillatorとはインバーターを複数個、リング状につないで動作させる仕組みである。

ここに信号を入れると、NOTゲート経過時にレイテンシーが発生するので、複数個並べると遅延が検出可能なほど大きくなる。この遅延を測定することで、トランジスタの動作状況を確認し、そこから疑似的に劣化具合を判断する仕組みである。

これはCPUの回路とは別に設けられているが、かけられる電圧はCPUの回路と一緒であり、Ring Bufferの特性を検出することでCPU本体の劣化具合を同時に確認できる。この劣化具合を計算に入れることで、電圧をかけ過ぎてCPUの劣化が加速しないように工夫するわけだ。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります