前回はDRAMセルの話だったので、今回は配線の話をしていく。IEDM 2025のショートコースで、IBM Researchの本山幸一博士による"Advanced Interconnect Technologies for Cu Extension and Beyond"という講演があった。

講演そのものは、配線がアルミニウムから銅に移行を始めた1997年頃からの歴史を全部おさらいしており、復習の意味では有益な話なのだが、そこから説明を始めると長くなりすぎるので、後半の"Post-Cu alternative metal interconnects"の内容を中心にお伝えしよう。

トランジスタより配線が壁? 微細化を阻むCu(銅)の課題

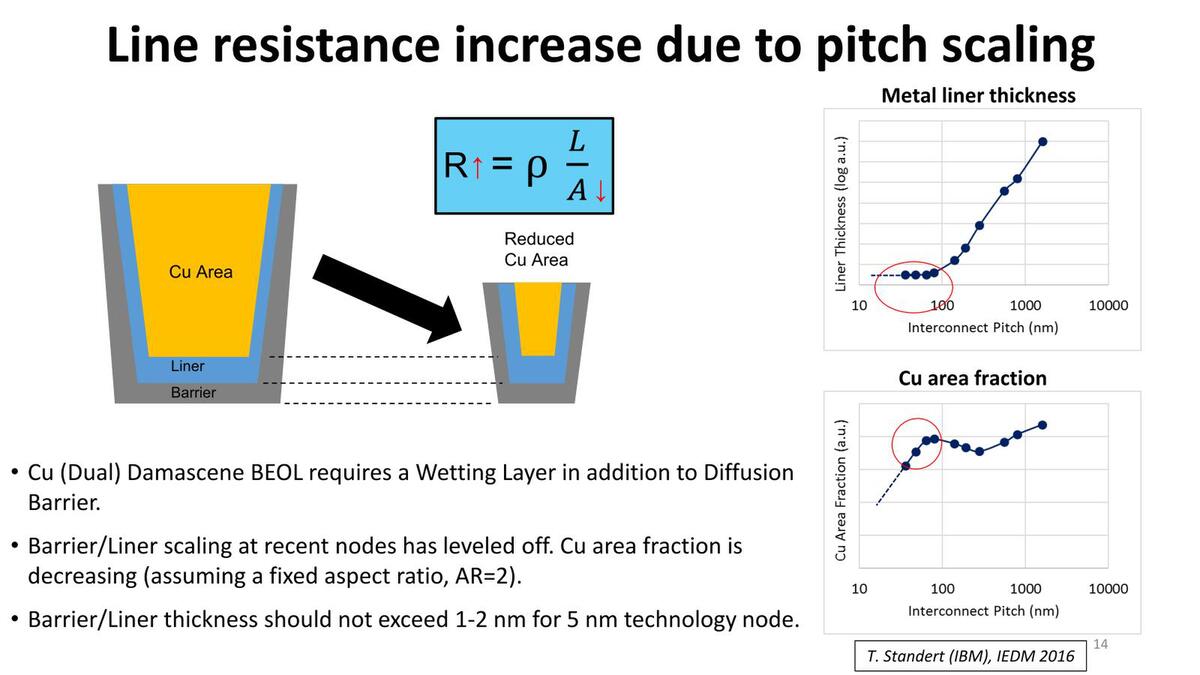

ポストCu世代に入る前に、Cu世代の問題について簡単にまとめておく。連載809回で、インテルがRu(ルテニウム)を配線に利用する話を書いたが、まずこの手前の話。配線ピッチを詰めていくと、配線層に占める銅の断面積がどんどん減り、抵抗が増えてエレクトロマイグレーション(材質に欠損が生じる現象)も起きやすくなる。

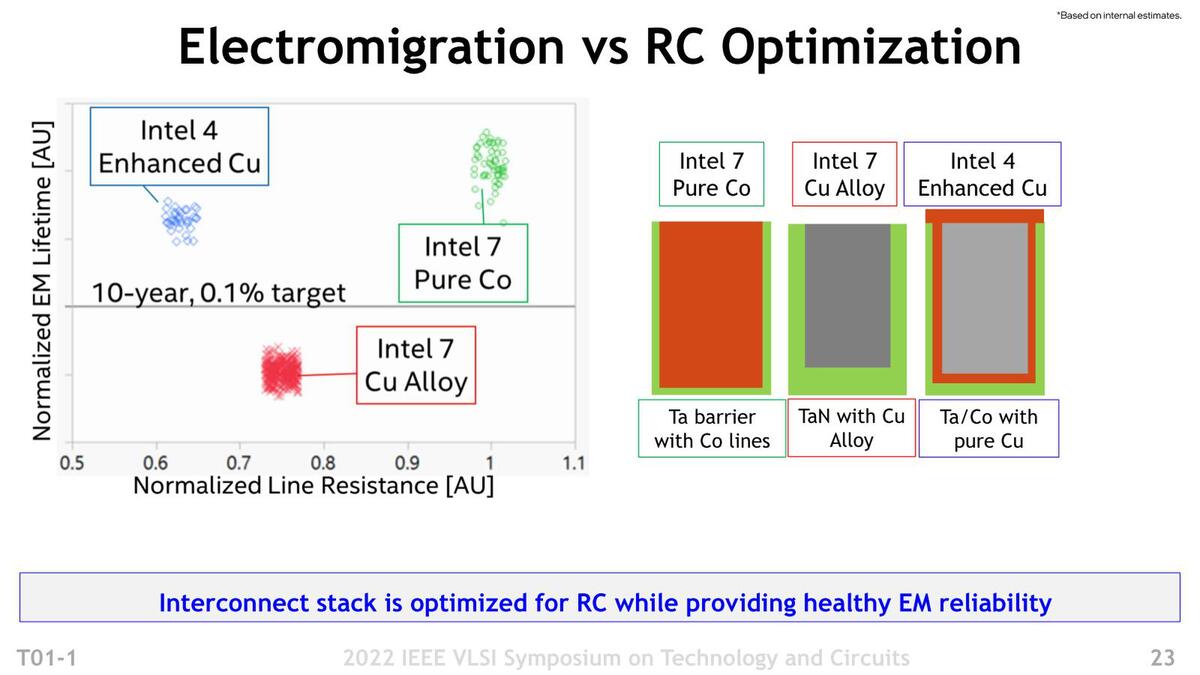

これをカバーするために、例えばインテルはTa/Co with pure Cu(銅配線の周囲をコバルトで覆い、その外側をタンタルでカバーする)という技法を編み出した。

IBMはTaとTaN(窒化タンタル)をバリア層に積層し、Cuの粒子サイズを大きくすることでエレクトロマイグレーション対策をするなど、いろいろ工夫をしているが、もうすでにプロセスの微細化はトランジスタそのものより配線の方がボトルネックになっている現状では、より微細化が求められることになり、もうCuのままで進めることは難しいと判断されている。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります