限界を迎えた微細化と信頼性の壁

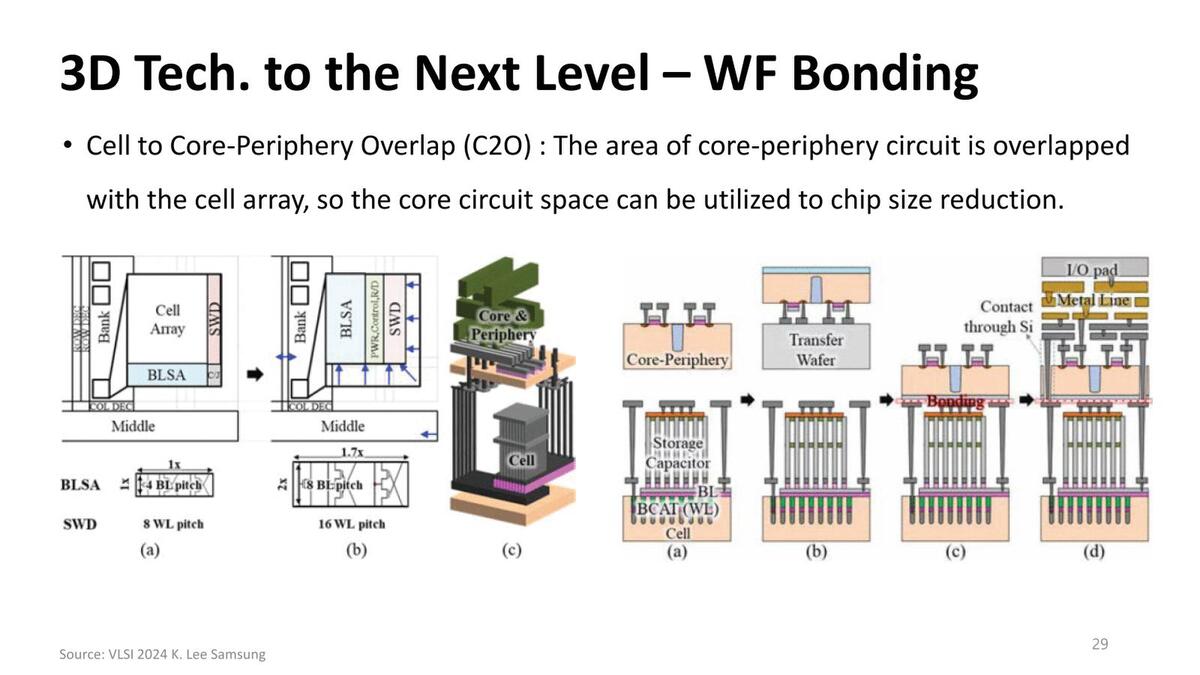

DRAMはNANDフラッシュ同様の3D化へ

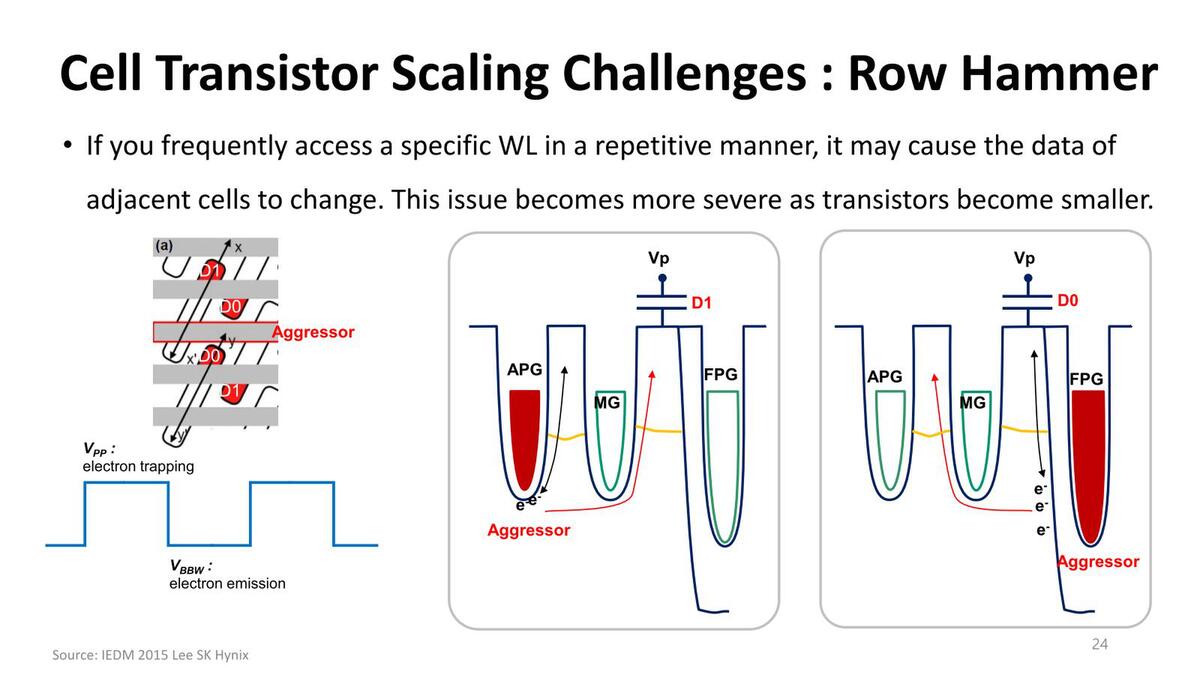

Row Hammerも昔から知られている副作用で、DDR2世代までは大して問題になっていなかったが、DDR3世代以降で問題になり始めており、現在も無縁ではない。

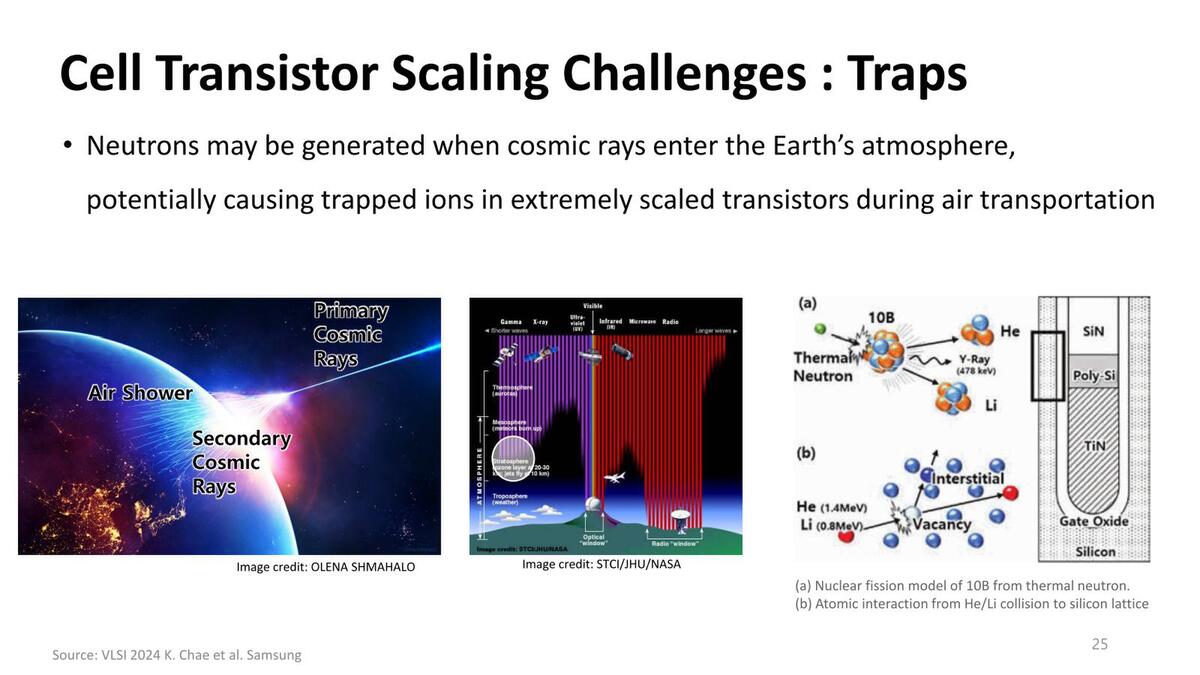

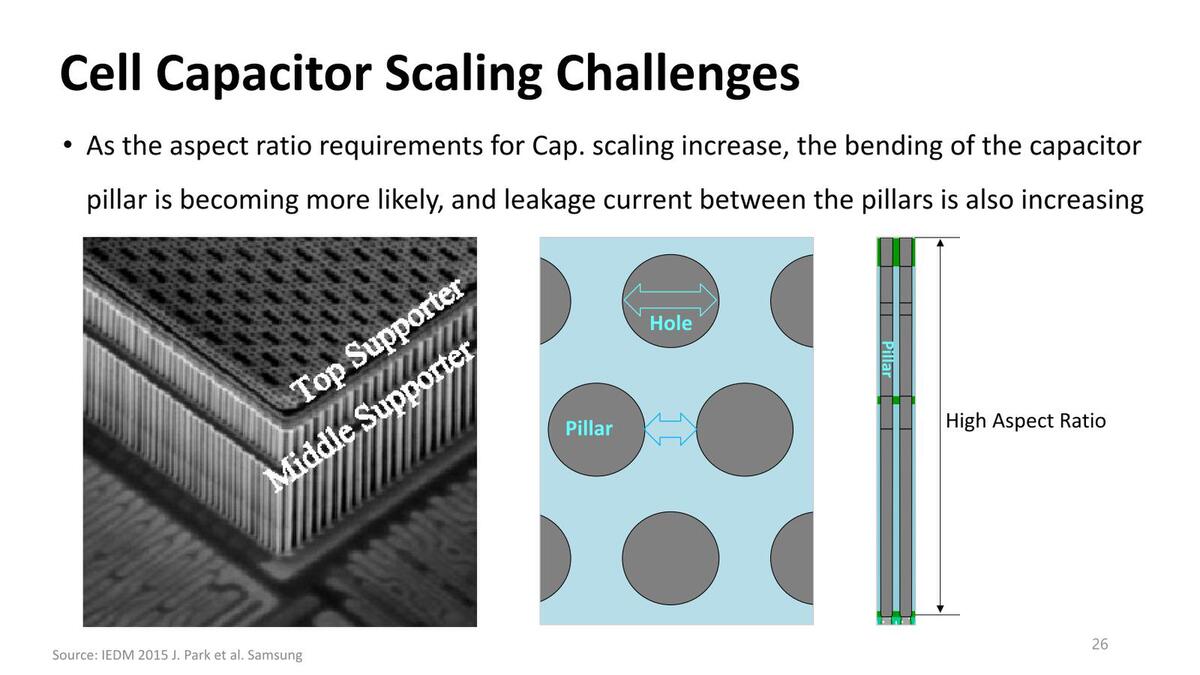

宇宙線などに起因するセルの書き換えに弱くなっているのも事実である。また先にアスペクト比の話をしたが、もうこれ以上アスペクト比を高めるのは構造が崩れかねないため難しく、微細化にともなって穴同士の間隔が狭まった(=絶縁層の厚みが減った)ことに起因するリーク増大も問題である。

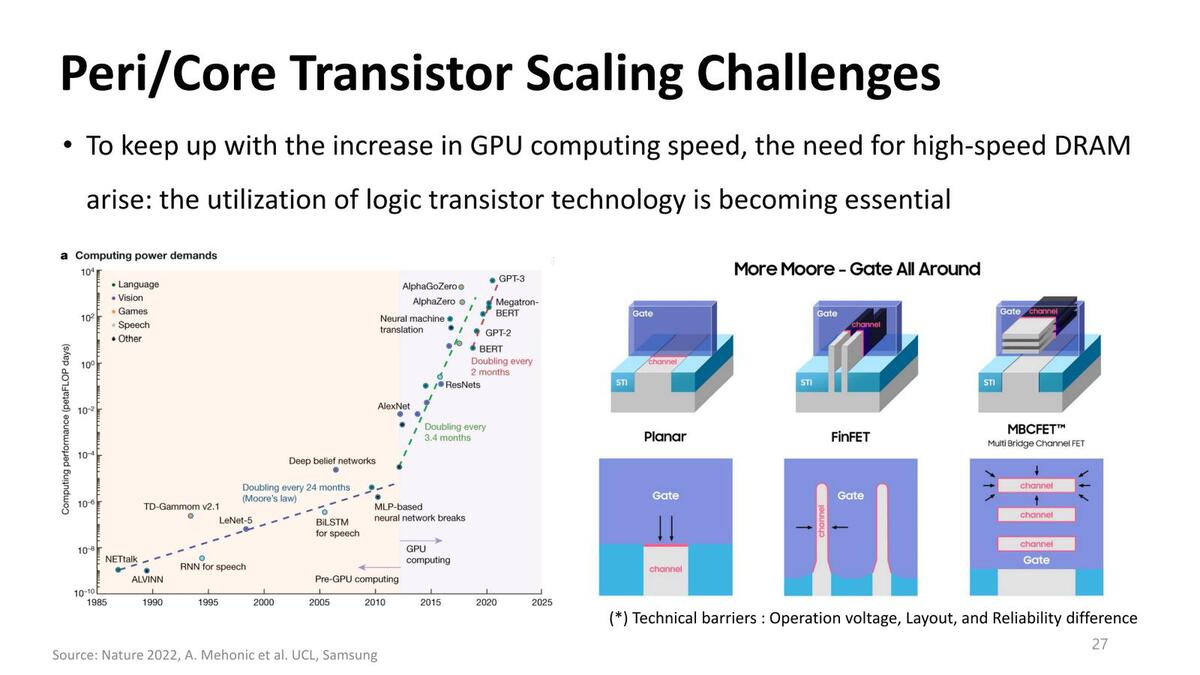

さらに、DRAMアクセス用のトランジスタも、DRAMセルそのものの高速化にともない高速なものが求められている。

ここまでが現状の問題である。これらの問題をどうにかできるのか? というと結論から言えば無理である。もちろん遠い将来にはもっと優れた材料がそろって、現在の問題を解決してさらに微細化を進められるかもしれないが、現時点で見えている範囲では無理である。ではどうするのか? というと、フラッシュメモリーと同じく3D化の方向である。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります