第861回

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説

2026年02月02日 12時00分更新

電源供給配線の最適化で配線抵抗を減らすことに成功

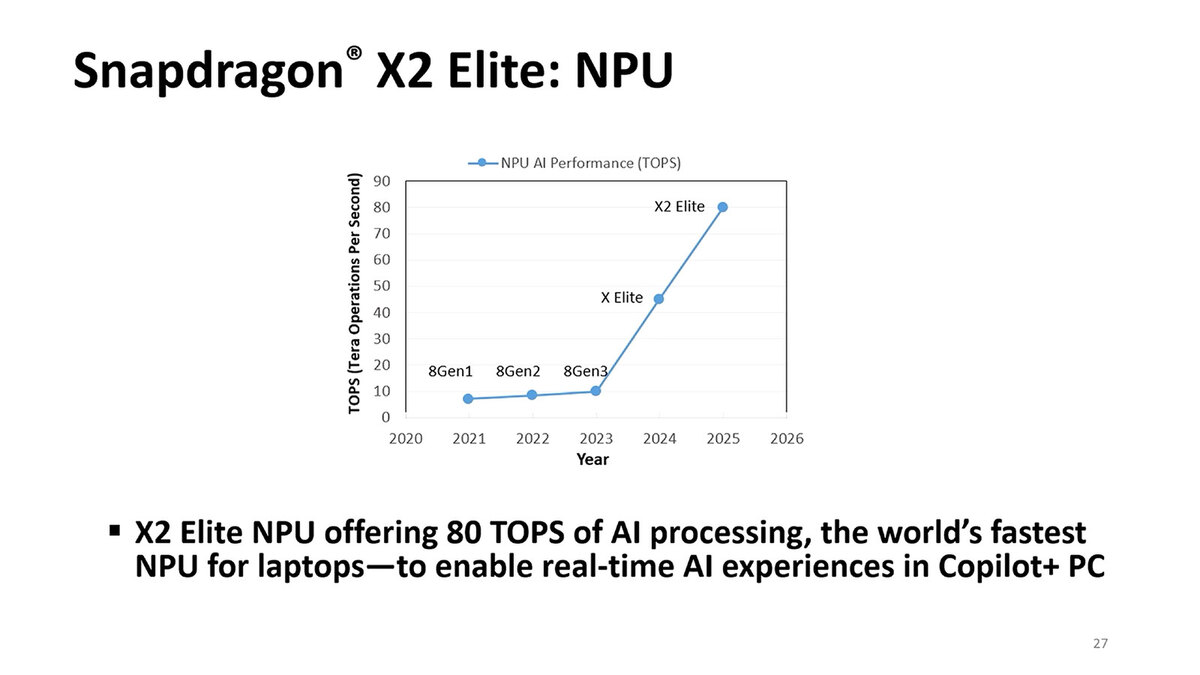

前モデルよりもCPU/GPU/NPU性能が大きく向上

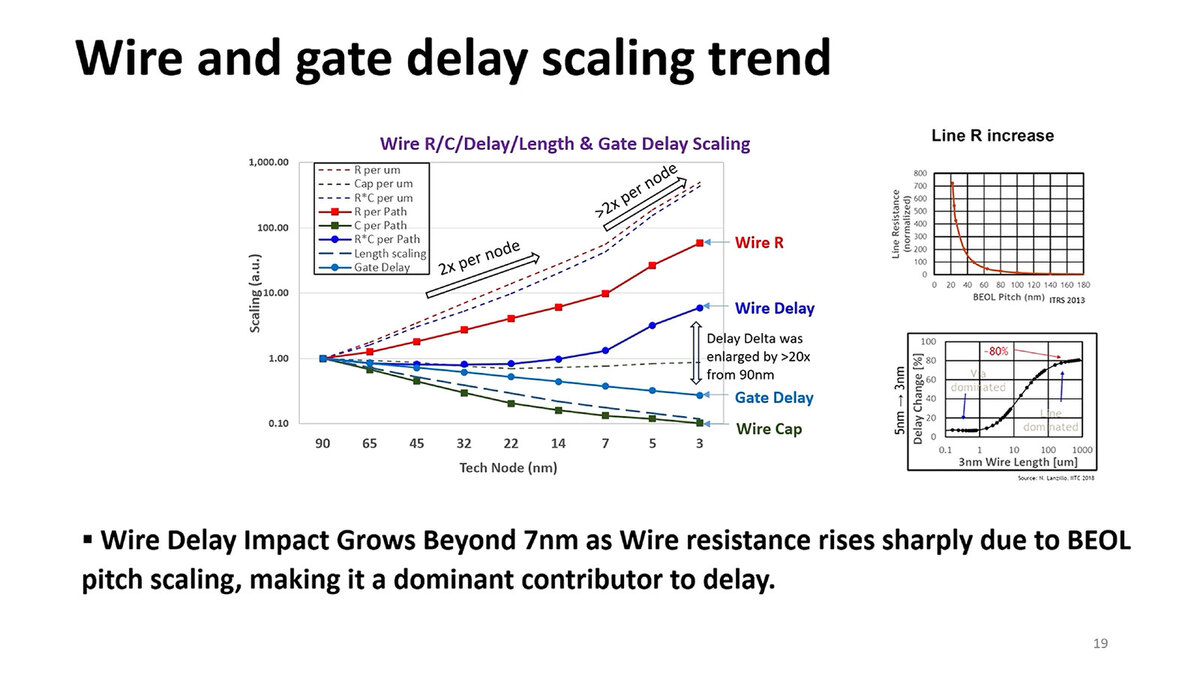

トランジスタだけでなく配線による遅延も問題である。下の画像は昨今のトレンドを示したものだが、ゲート遅延と配線遅延を比較すると、90nm世代と比較して20倍以上の開きがあるとされる。

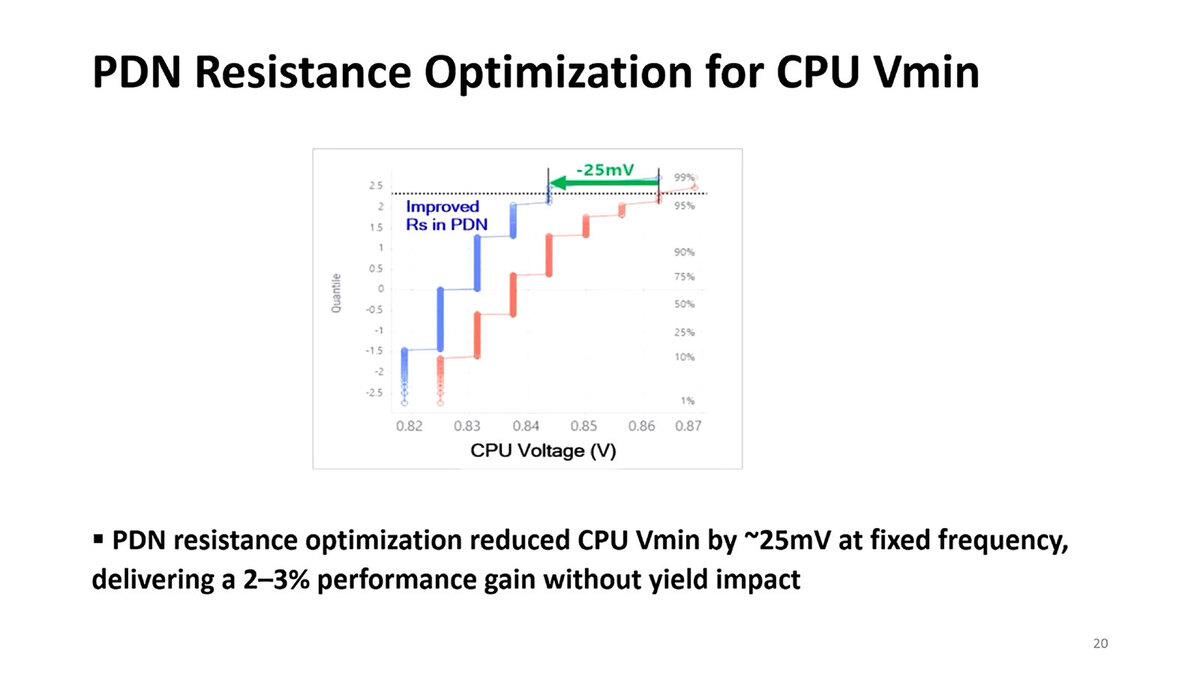

もっとも、だからといって配線そのものの最適化は設計段階でやっているし、新材料を使うというわけにもいかないのだが、PDN(Power Delivery Network:電源供給配線)の最適化をしたことで、PDNの配線抵抗を若干減らすことに成功、これにより電源電圧を25mVほど引き下げることに成功したとしている。

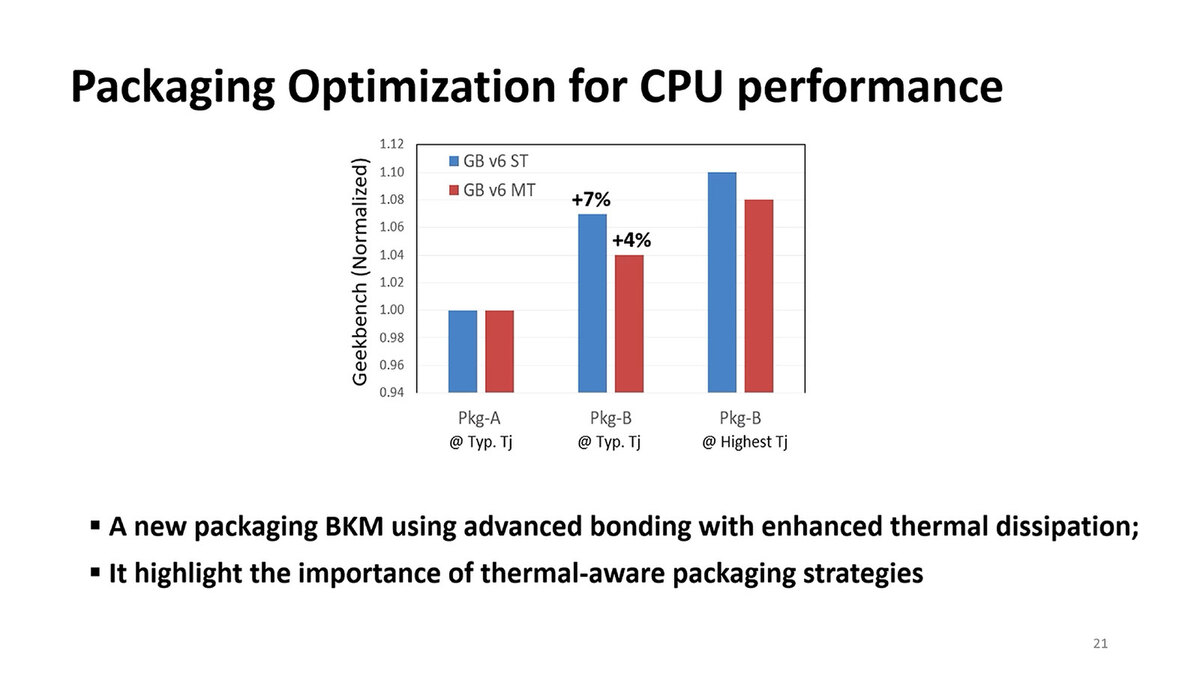

ほかにも、パッケージ構造の最適化により、GeekBench v6のスコアでシングルスレッドで+7%、マルチスレッドで+4%の性能改善ができた。

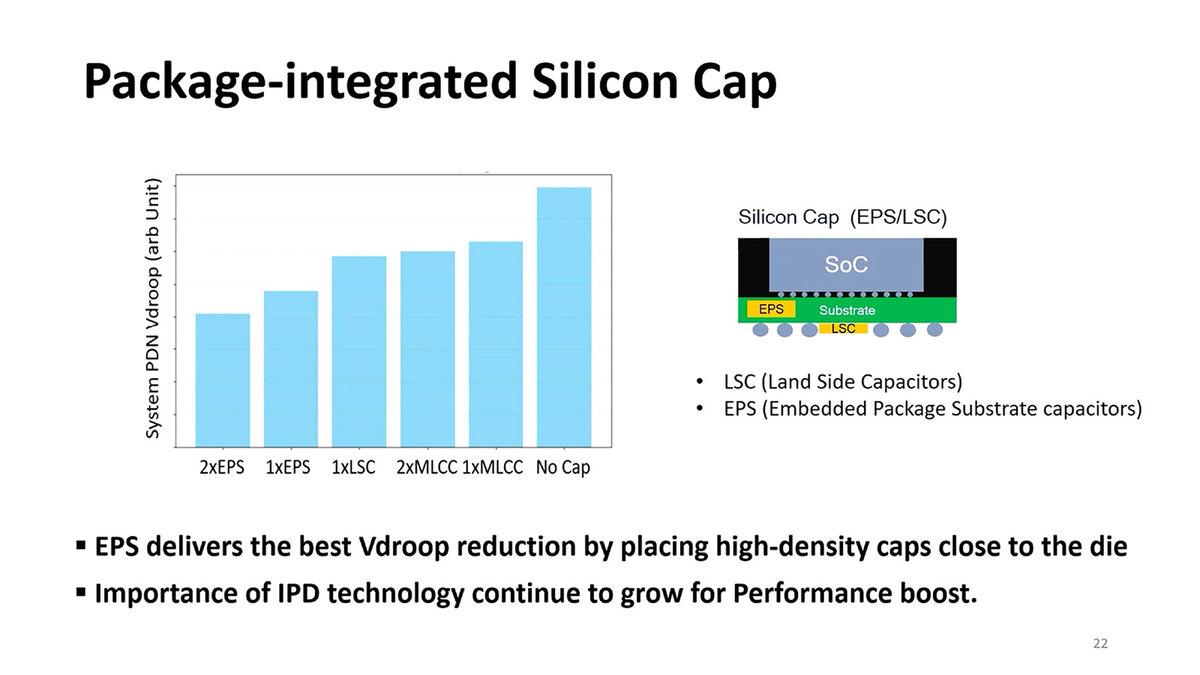

電源周りでパスコンをどう配置するか? では、パッケージ配線内に埋め込むEPS(Embedded Package Substrate Capacitors)を複数配するのが一番電圧降下が少なかったとしている。

通常はMLCC(積層コンデンサ)をパッケージ周囲に配するわけだが、配線層直下に置くLSCや配線層埋め込みのEPSの方がより効果的であるとする。ただLSCはそもそも配置できる面積が少ないし、EPSはコスト増の要因になるので兼ね合い次第ではある

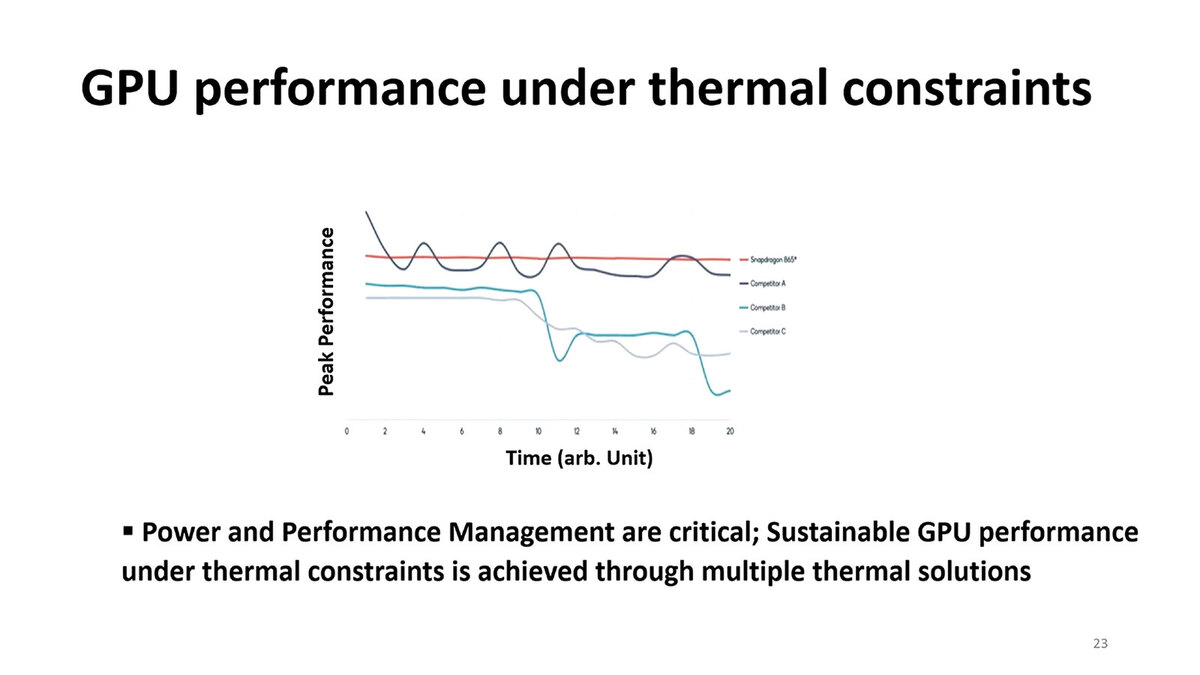

細かいところではGPUの温度をもっと精密に制御することで、競合製品に比べて一定の性能を長期間保てるとしているのだが、Snapdragon X2 EliteではなくSnapdragon 865というところが今一つ「?」である。

説明を聞くに、どうもSnapdragon 865世代から複数のサーマルコントロールを組み合わせてGPU性能をピーク近くに保つ工夫がなされており、Snapdragon X2 Eliteでもそれは実装されているらしい

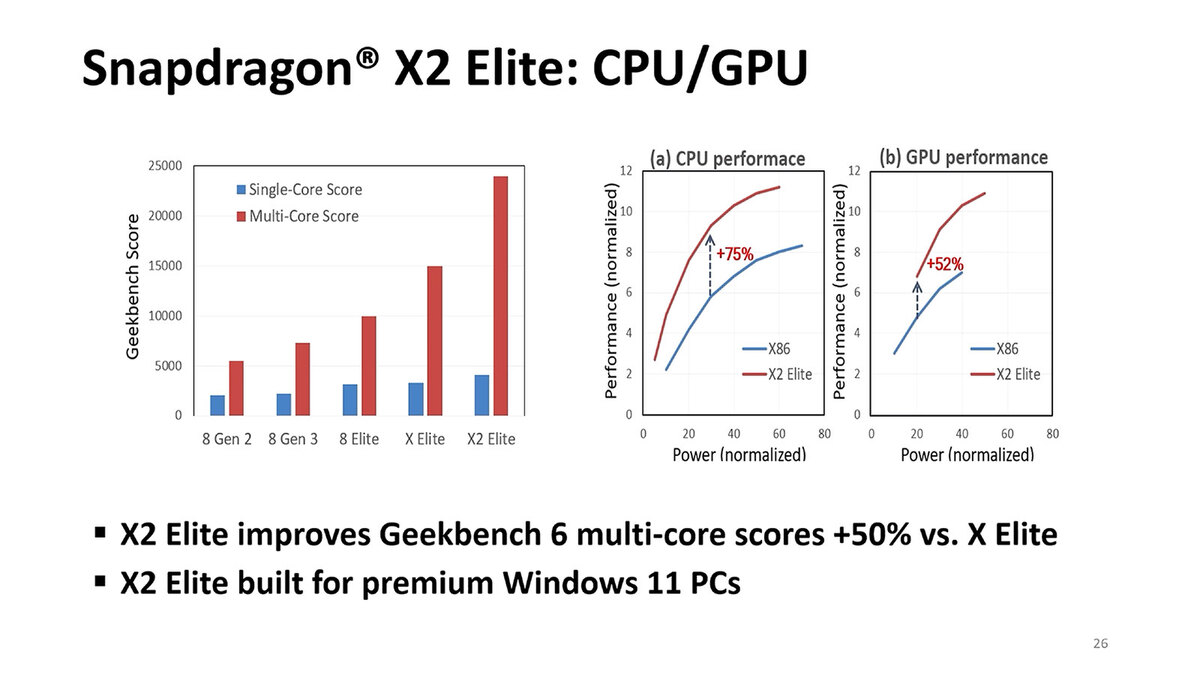

こうした工夫を積み重ねることによって、CPU/GPU性能およびNPU性能で、前モデル(Snapdragon X Elite)と比較しても大きく向上させており、またx86ベースの競合製品(具体的な名前は出てこなかったのだが、Lunar Lake世代あたりだろうか?)と比較しても大きな性能/消費電力比を実現している、と締めている。要するに、本当に細かな工夫を積み重ねることで性能が改善できた、という話であった。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります