次世代EPYCのVeniceは

第5世代EPYCとSocketの互換性がない可能性大

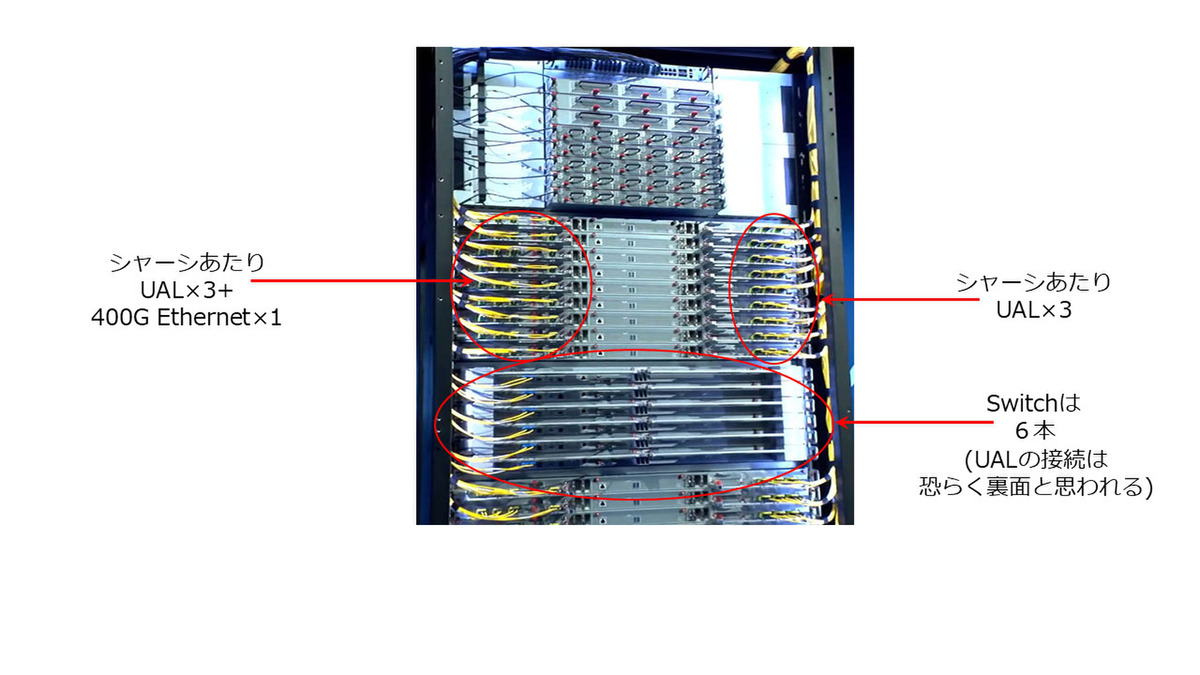

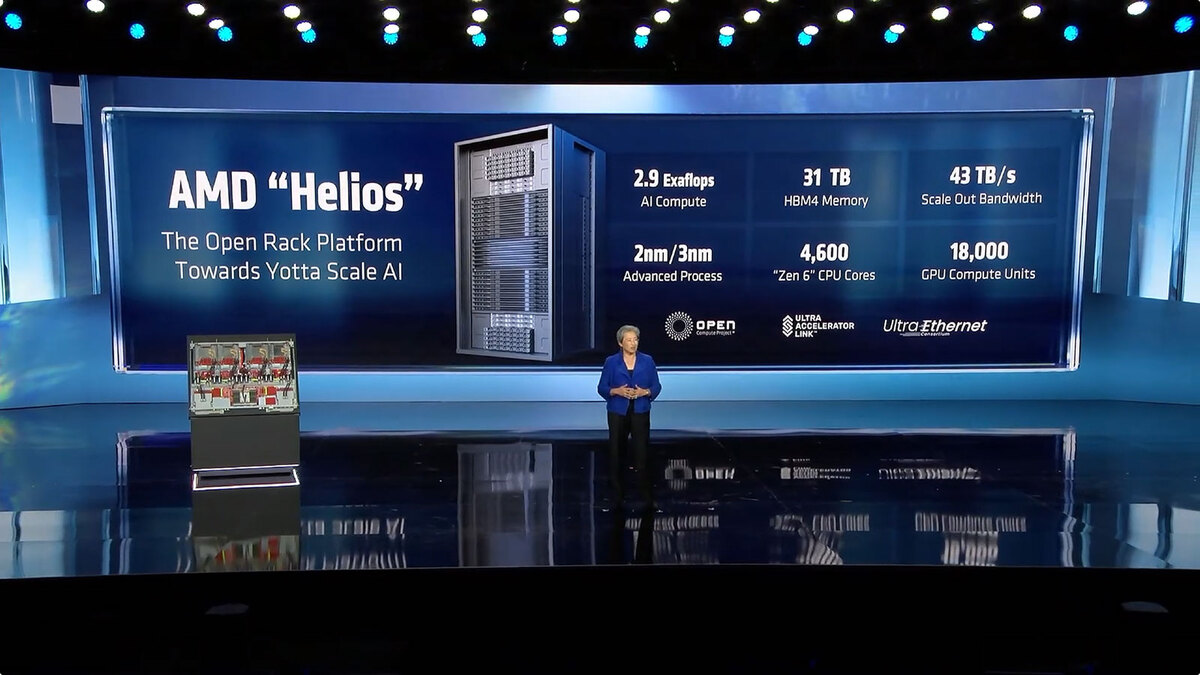

あらためて基調講演で示されたHeliosのラックが下の画像であるが、このブレードとスイッチの構成推定が下図である。

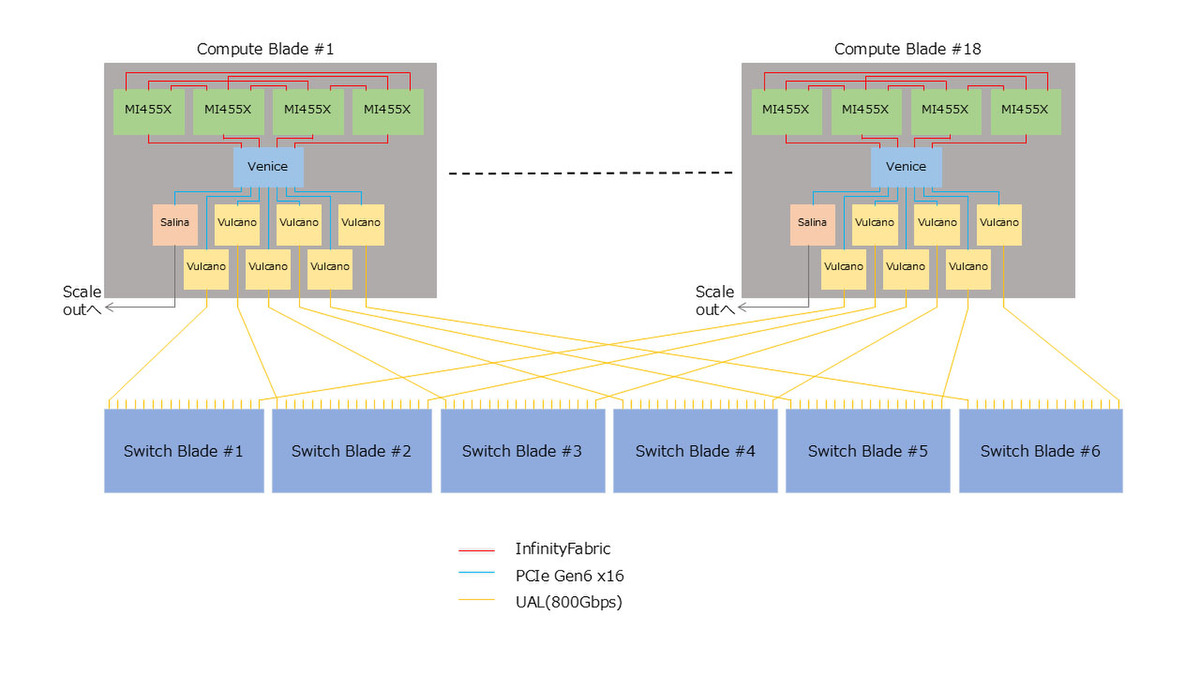

これが正しいとすると、Heliosラック全体の構成は下図のようになるのではないか? というのが筆者の推定である。

次はVeniceとMI455Xの詳細である。今回初めてHeliosの詳細が公開されたが、CPUコアは全部で4600個とある。Compute Bladeは全部で18枚なので、4600÷18=255.555……でCompute Bladeが1枚あたり256コアという計算になる(256×18=4608なので、丸めれば4600コアである)。

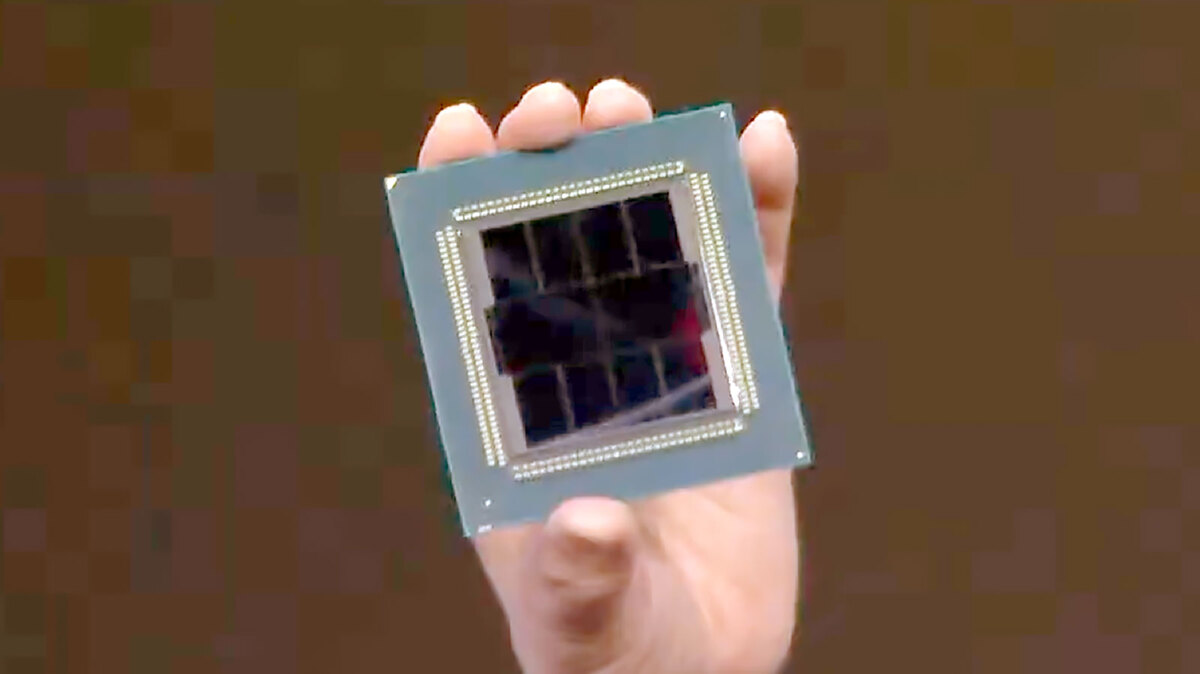

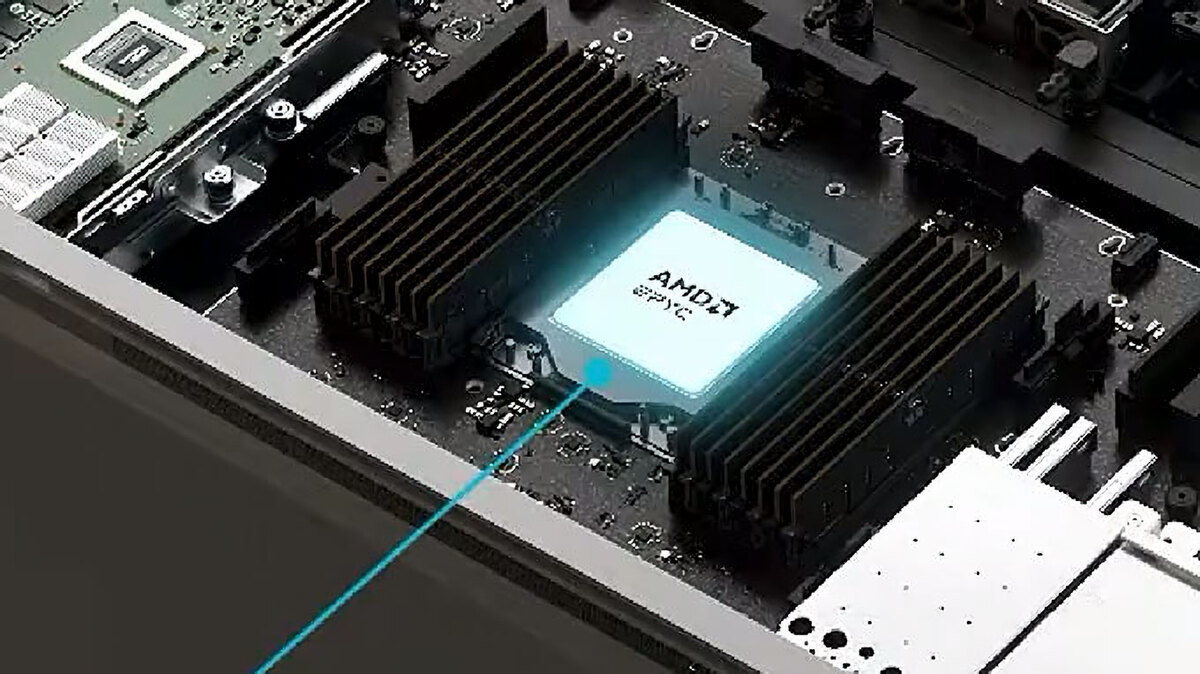

Veniceの実物も公開されたが、少し暗いのでパッケージの周りだけを明るく示したのが下の画像である。

ここからわかるのが、以下の3つとなる。

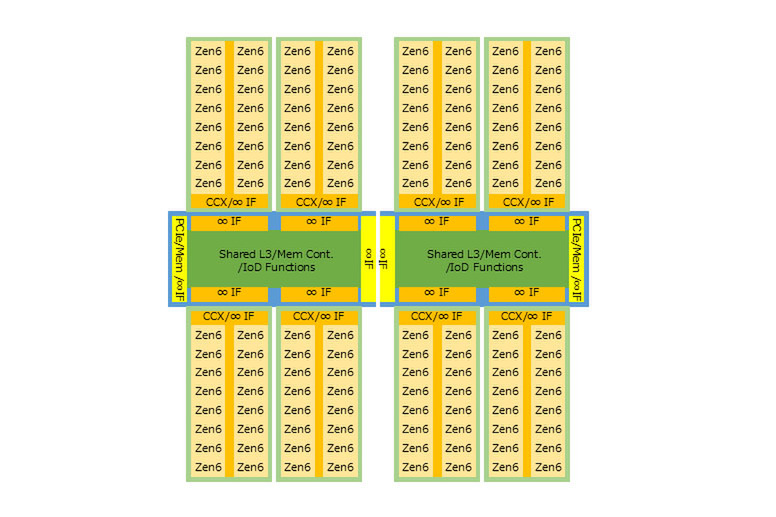

- CCDは32コアに強化された。

- 従来のMCM(Multi-Chip Module)構造から、Interposerを利用した構造に変更されたように見える。

- 従来のIoDの構造と異なっている様に見える。L3の持ち方も変わっている可能性がある。

下の画像はVenice周辺を拡大したものだが、どう見てもDIMMスロットが16本存在している。つまりVenice世代のEPYCは、第5世代EPYCとSocket互換性がないものと考えられる。DDR5 DIMMを16ch接続、という時点でSocket形状に互換性を持たせるのは不可能だからだ。

ここで気になるのはZen 6ダイのL3の持ち方だ。ダイそのものの大きさは、Zen 5cベースのダイ(Zen 5c×16コア)とそれほど変わらないように見えるが、プロセスを微細化した(3nm→2nm)とはいえ、コアを倍増できるとは思えない。可能性としてあるのは、CCDにはもはやL3を持たない可能性だ。

IoDとして2つのダイがあるというのは、下図の構造になっており、CCDはコア+L2が32個入っているだけで、L3はIoD側(IoDという名前かどうかも怪しいが)に移っているという可能性だ。

2つめの可能性は、CCDの側がZen 5の3D V-Cacheと同じく2層構造になっており、Compute Dieの下にL3 Dieが位置しており、これでL3をローカルに持つ構造だ。ただし、コストが思いっきり上がるのであまり現実的な案とは思えない。特にCCDをコンシューマー向けのRyzenと共用する構図が引き続き維持されるのだとすればなおさらだ。それよりはIoDの方にL3を置いて、必要ならそのIoDの側のL3をそれこそ3D V-Cacheのように積層する形で増量する方が妥当かと思われる。

3つ目の可能性は、前述のVeniceの実物画像に見えているIoDと思しきダイは全部L3であり、このCCD×8+L3×2のダイの下に、メモリーコントローラー(と、なんならL4キャッシュ)とインフィニティ・ファブリックを載せた大きなIoDが置かれるという構図だ。Instinct MI300Xシリーズと同じ構成である。コンシューマー向けのRyzenには不可能だろうが、サーバー向けのEPYCであれば不可能ではない。

最終的にどの構成が正解かは現時点ではなんとも言い難いが、とにかく従来のEPYCとはまったく違う構成になっていることだけは間違いなさそうだ。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります