2通りあるCFETの製造方法

それぞれの利点と欠点

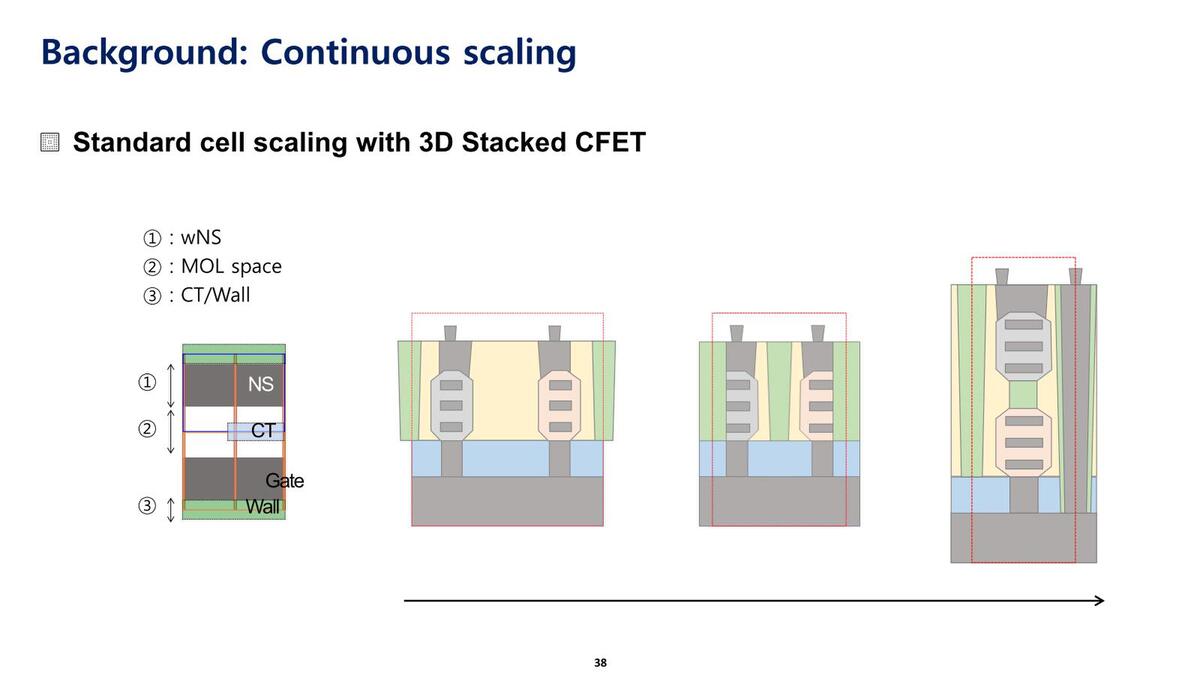

Nanosheetに続くのがForksheet世代になる。Forksheetについては連載837回で説明しているが、要するにP型とN型のトランジスタをどんどん隣接させて密度を向上させた構成である。なのだが、なぜかSamsungはこのForksheetをパスして次のCFETに話を移しているので、こちらもForksheetはパスして次の話に進む。

と言いながらいきなりForksheetが下の画像に出てくるのだが、基本は2つのGAAFETを縦積みにするという内容である。

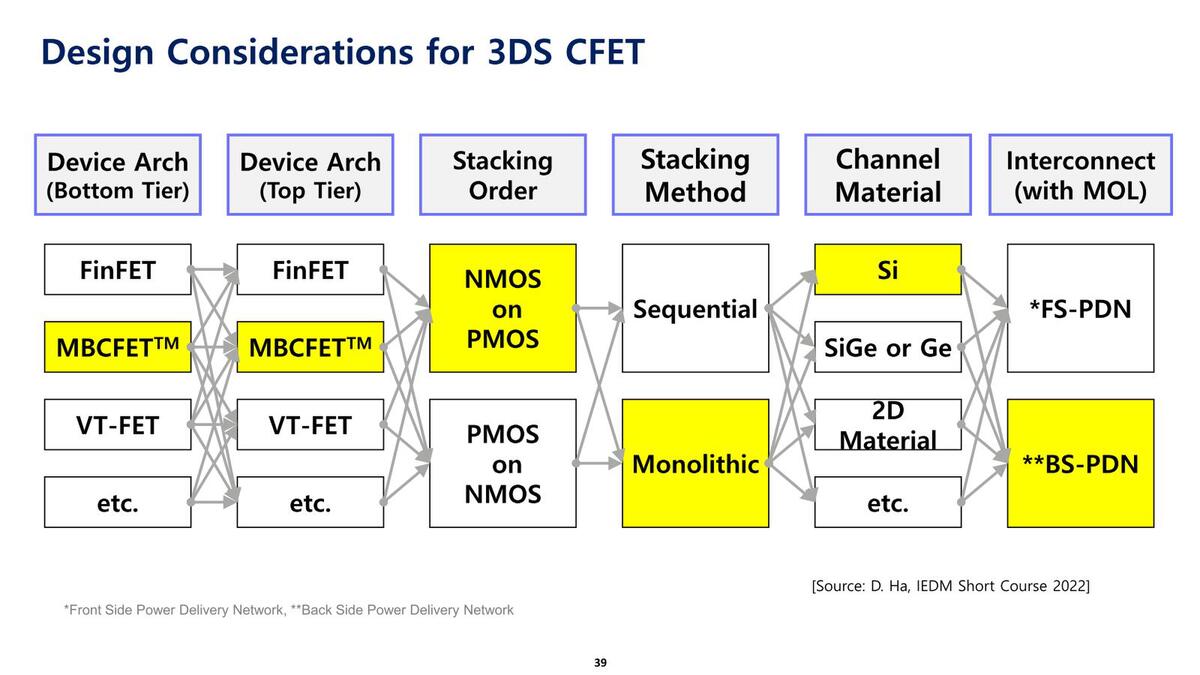

この際の選択肢として、上と下のFETになにを使うか、PMOSとNMOSのどちらを上にするか、どう積むか、チャネル材料をどうするか、電源をどこから供給するかなどの多数の選択肢があるのがわかる。

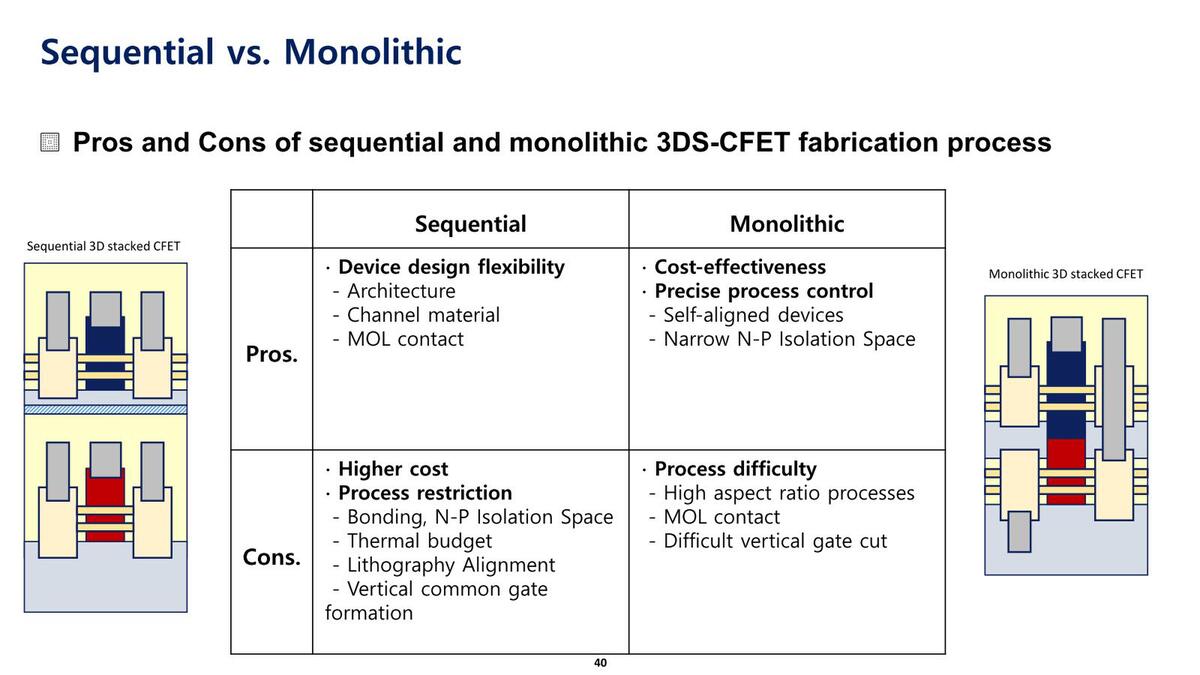

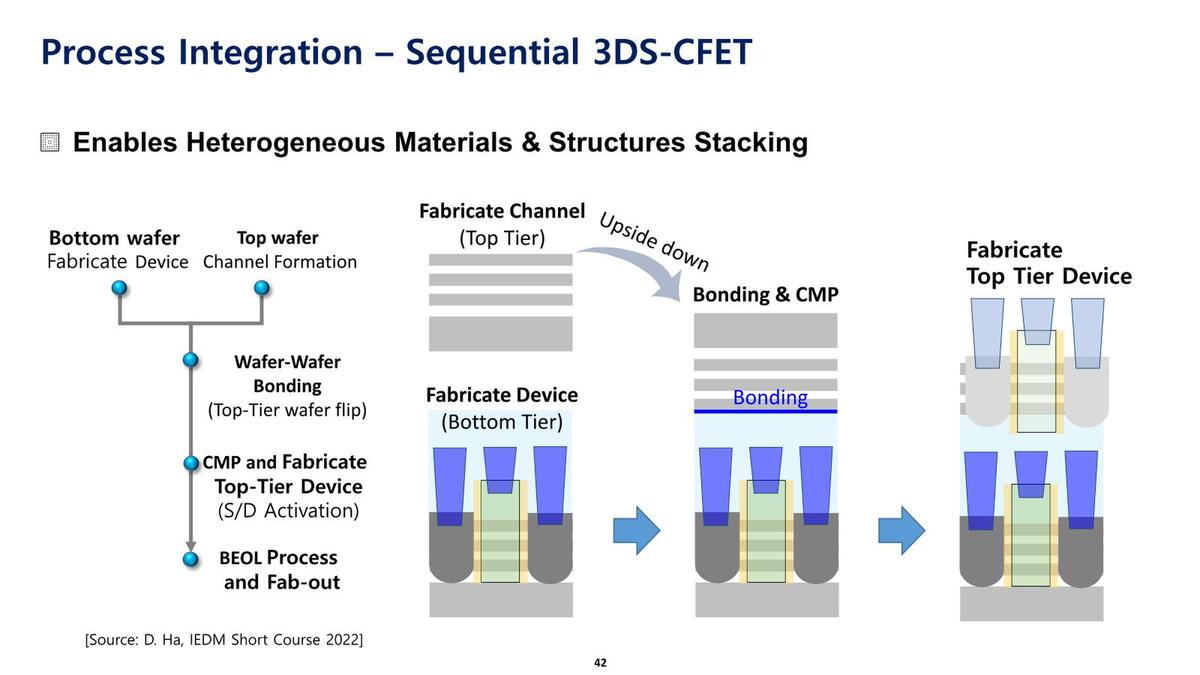

ここでFETがどちらもMBCFETであることは議論にはならないだろう。問題は、シーケンシャルかモノリシックかだ。シーケンシャルとはNMOSとPMOSを別々のウェハーで作成し、これをつなげるもの。モノリシックは、PMOSを作成し、間の配線層を作り、その上にNMOSを作り、という形で一体的に構築する方法である。

シーケンシャルの方が、個々のFETの構築は容易であるが、なにしろ別々に作ったものの重ね合わせであるため、位置合わせの精度を保つのが非常に難しい。特に縦方向のゲートの配線の調整などは相当気を使う必要がある。また当然ながらコストも上がる。

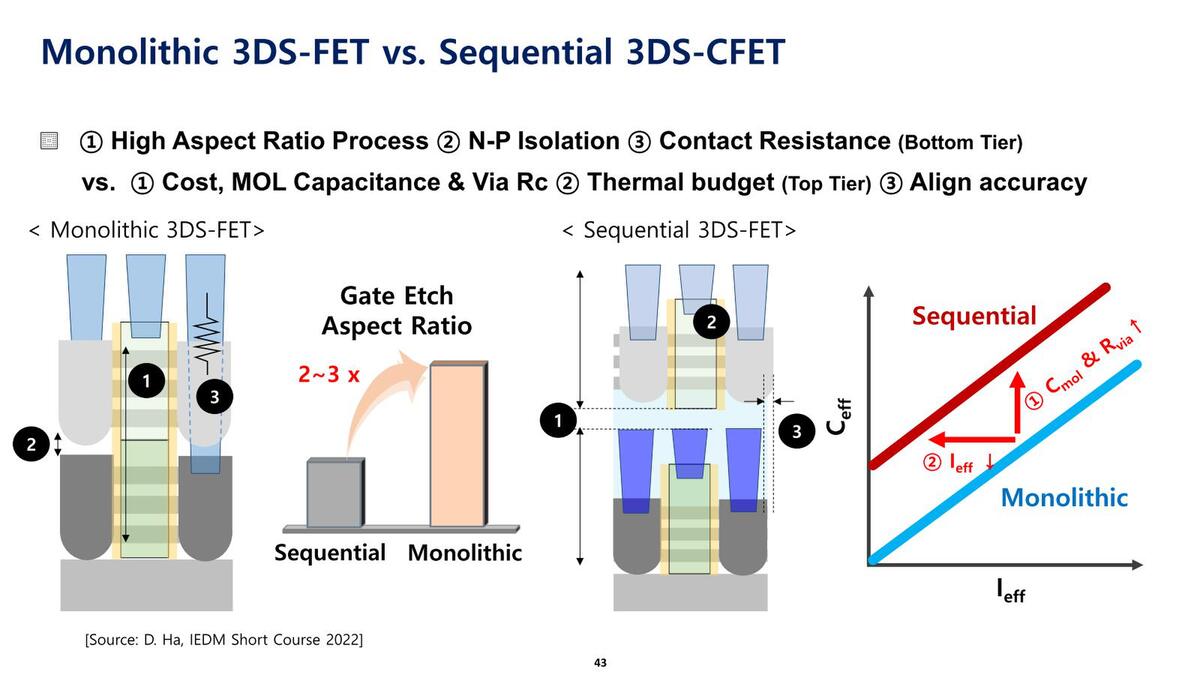

一方でモノリシックは一体的に構築するため位置合わせの精度はシーケンシャルほど厳しくないが、中間層の配線構築や、縦方向に長い(深い)配線を構築する必要がある関係で、高アスペクト比(底面積と高さの比)の穴を構築しなければいけないなど、こちらはこちらでいろいろ課題がある。

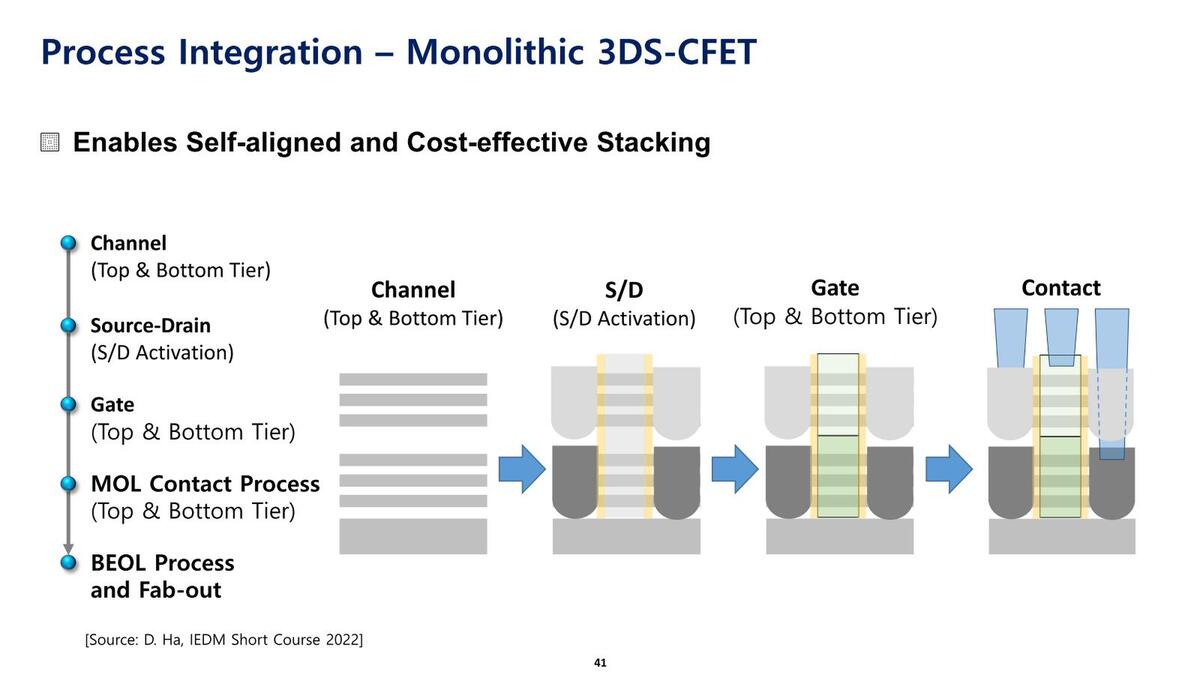

下の画像が簡単化したモノリシックでの製造方法、一方さらに下の画像が簡略化したシーケンシャルでの製造方法である。コストを度外視すれば、位置合わせの精度の問題はあるにせよシーケンシャルの方が複雑な構造を作りやすいが、今後の展開を考えた場合には多少技術的な難易度は高いにせよモノリシックで作る方が確実、というのがどのファウンダリーでも共通認識のようだ。

両者の損得を比較したのが下の画像だ。モノリシックは縦穴の構築の際のアスペクト比がシーケンシャルの2~3倍になるのと、PMOS/NMOSの絶縁の問題、それとPMOS側の接触抵抗が問題になる一方、シーケンシャルではコスト以外にMOLの寄生容量や接触抵抗、PMOS側の発熱の問題、それと位置合わせの精度が問題になるとする。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります