第850回

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ

2025年11月17日 12時00分更新

久しぶりにAMDのロードマップを紹介しよう。11月4日に第3四半期の決算発表を行なったAMDは、翌週の11月11日にFinancial Analyst Day 2025を開催した。ここでいろいろロードマップなどが公開されたので、今回はCPU周りをまとめて説明する。

Zen 6世代に新しいAI Data Typeを追加

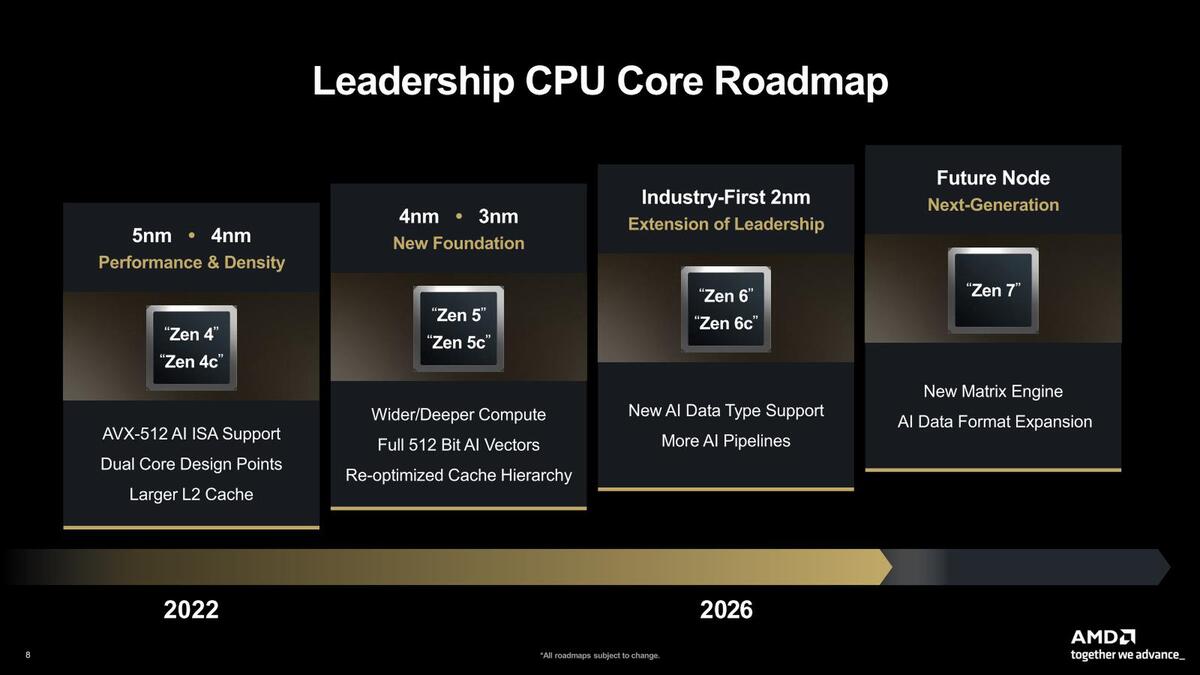

まずMark Papermaster CTOによるスライドから。CPUコアのアーキテクチャーであるが、すでに現在Zen 6の開発が進んでいることは明らかにされている。Zen 6ベースのVeniceの最初のシリコンはテープアウトが完了し、ウェハーの試作も完了したことは今年4月に明らかにされている。

今回明らかにされたのは、このZen 6の世代にも当然、高密度のZen 6cが追加されることと、新しいAI Data TypeのサポートとAIパイプラインの強化が施されていること。それとその次にZen 7が予定されていることが公式に明らかになった。

まずZen 6/6cについて。New AI Data TypeというのはAVX512-VNNIの拡張ではないかと思われる。AMDのUmesh Kalvakuntla氏(2024年6月よりAMDのCompiler Engineerとして勤務)が今年11月7日に投稿したGCC (GNU Compiler Collection)のパッチによればZen 5までのAVX512関連命令のサポートに加え、新たに以下の5命令が追加されたとある。

- AVX512_BMM

- AVX_NE_CONVERT

- AVX_IFMA

- AVX_VNNI_INT8

- AVX512_FP16

この5命令はいずれもSapphire Rapidsで新たに追加されたもの(16bit幅で言えばこれまではCooper LakeでAVX512_BF16が追加されており、これはZen 5でもサポートされていた)であり、今回これをZen 6/6cでもサポートすることになったのがNew Data Typeという話ではないかと思われる。逆に言えばFP8やFP4、FP6のようなものはまだ手付かずのようだ。

余談ながらこのSapphire Rapidsでは、ほかにCMPCCXADDとPREFETCHI命令も追加されており、PREFETCHIはもうサポートされているが、CMPCCXADDは現状未サポートのままのようだ。この理由は不明である。

まだ詳細が不明なのは"More AI Pipelines"であり、現在のAMDのAI関連命令は全部浮動小数点(Floating Point)側で処理しているから、これはつまりFPUをさらに強化する、という話になる。過去の構成をまとめるとFPUは以下のようになっていた。

| FPUの構成 | ||||||

|---|---|---|---|---|---|---|

| FPUデータ幅 | 命令実行サイクル | |||||

| Zen 1 | 128bit×4 | AVX256×1 | ||||

| Zen 2/3 | 256bit×4 | AVX256×2 | ||||

| Zen 4 | 256bit×4 | AVX256×2/AVX512×1 | ||||

| Zen 5 | 512bit×4 | AVX256×2/AVX512×2 | ||||

Zen 1~Zen 3の世代まではFPUはADDとMULが別々のパイプラインで、2つを組み合わせて1つのAVX256命令を処理できる格好だったが、問題はADD側が非対称構成(片方のADDはサポートできる命令がやや足りない)関係で、実行パイプラインの数の半分しかAVX256命令が処理できなかった。

これを解決して完全な対称型になったのがZen 4で、この世代で初めてAVX512命令をサポート。Zen 5では実行パイプラインのデータ幅を倍増させて、ついに1サイクルで2つのAVX512命令を処理できるようになった。

ならば、AVX256では4命令/サイクルになるのか? となる。しかし、連載815回で説明したようにAVX256の実行時はFPUのクロックゲーティング/パワーゲーティングが行なわれて扱えるデータ幅が半分になるので、処理性能はAVX256×2のままである。

ではZen 6は? だが、いきなり512bit×8にはならないと思われる。せいぜいが512bit×6程度ではなかろうか。それもすべての命令で対応するわけではなく、拡張された部分がサポートするのはAVX512-VNNI関連命令だけ、とか制約がつきそうな気がする。

理由は簡単で、倍増させると大幅にエリアサイズが増えるし、消費電力も増えるからだ。ちなみに以前、Zenの構造をGCCのソースコードから推定する試みを行なったが、現状まだZen 6向けのパッチがgcc/config/i386/向けに投稿されていないので、筆者の推定が正しいかどうかは判断がつかない。

続くZen 7ではNew Matrix Engineが追加されるとしている。考えられるのはインテルのAMXかArmのSME2、ないしIBMのMMAということになるが、順当に考えればAMXであろう。

問題はAI Data Format Expansionである。実はAMX、Sapphire RapidsではINT8とBF16のみ。Granite RapidsでFP16、Granite Rapids-DでComplex(FP16の複素数型)が追加され、今後登場するDiamond RapidsではFP8/TF32が追加サポートされるという話になっている。

Diamond Rapidsでは、AVX512ではなくAVX10.2のサポートになる(のでAVXもFP8をサポートする)のだが、Zen 7でAVX 10.2のサポートまでいくのか、それとも単にGranite Rapids-D相当のComplexどまり(AVX 10.1)になるのかは判断がつきかねる。なんとなくAVX10.1相当でとまりそうな気がするのだが根拠はない。

ちなみにIPCや動作周波数、内部のパイプラインの詳細などはまったく公開されていない。とりあえずZen 6世代がN2ベースなのは間違いなく、Zen 7は時期的に言えばTSMC A16も利用可能ではあるのだろうが、コストや供給能力などを考えるとN2 Phoenixどまりの可能性もありそうだ。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります