第847回

国産プロセッサーのPEZY-SC4sが消費電力わずか212Wで高効率99.2%を記録! 次世代省電力チップの決定版に王手

2025年10月27日 12時00分更新

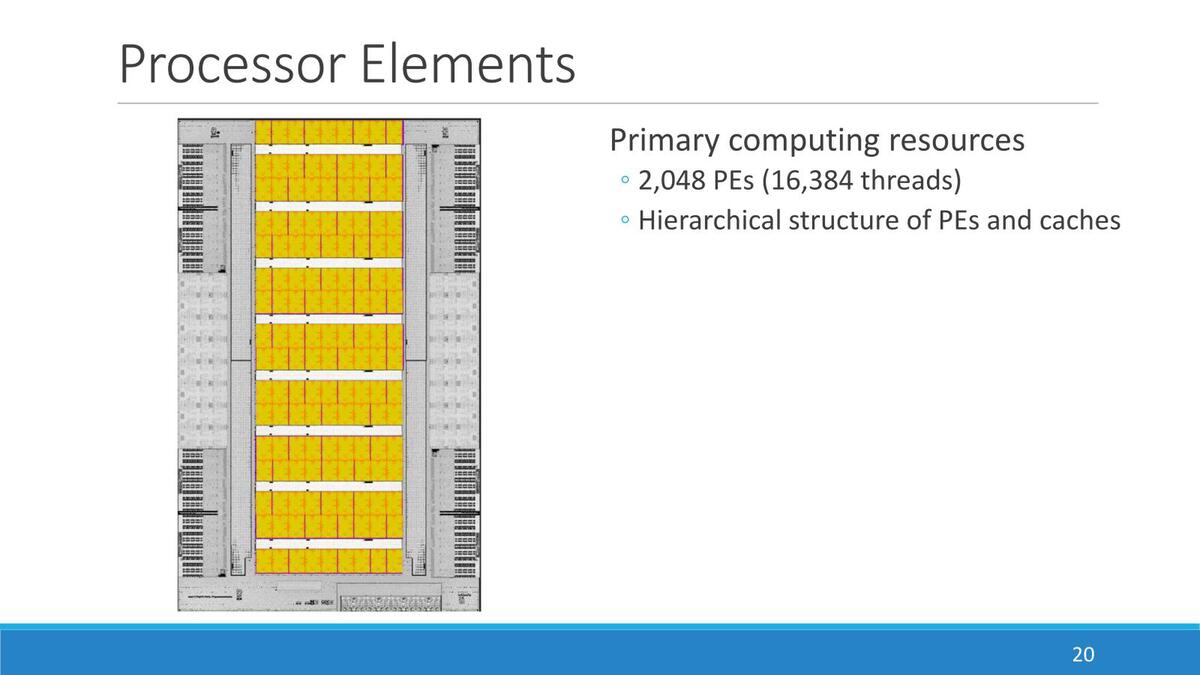

1チップで50TFlopsを達成予定の最新プロセッサーPEZY-SC4s

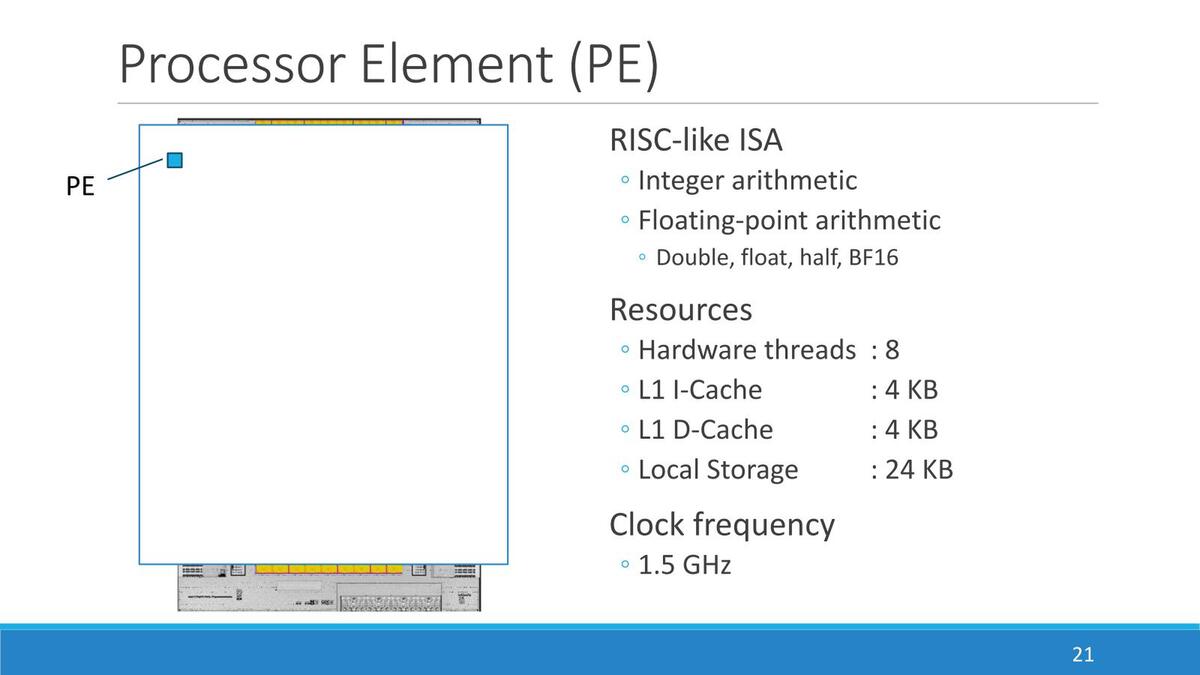

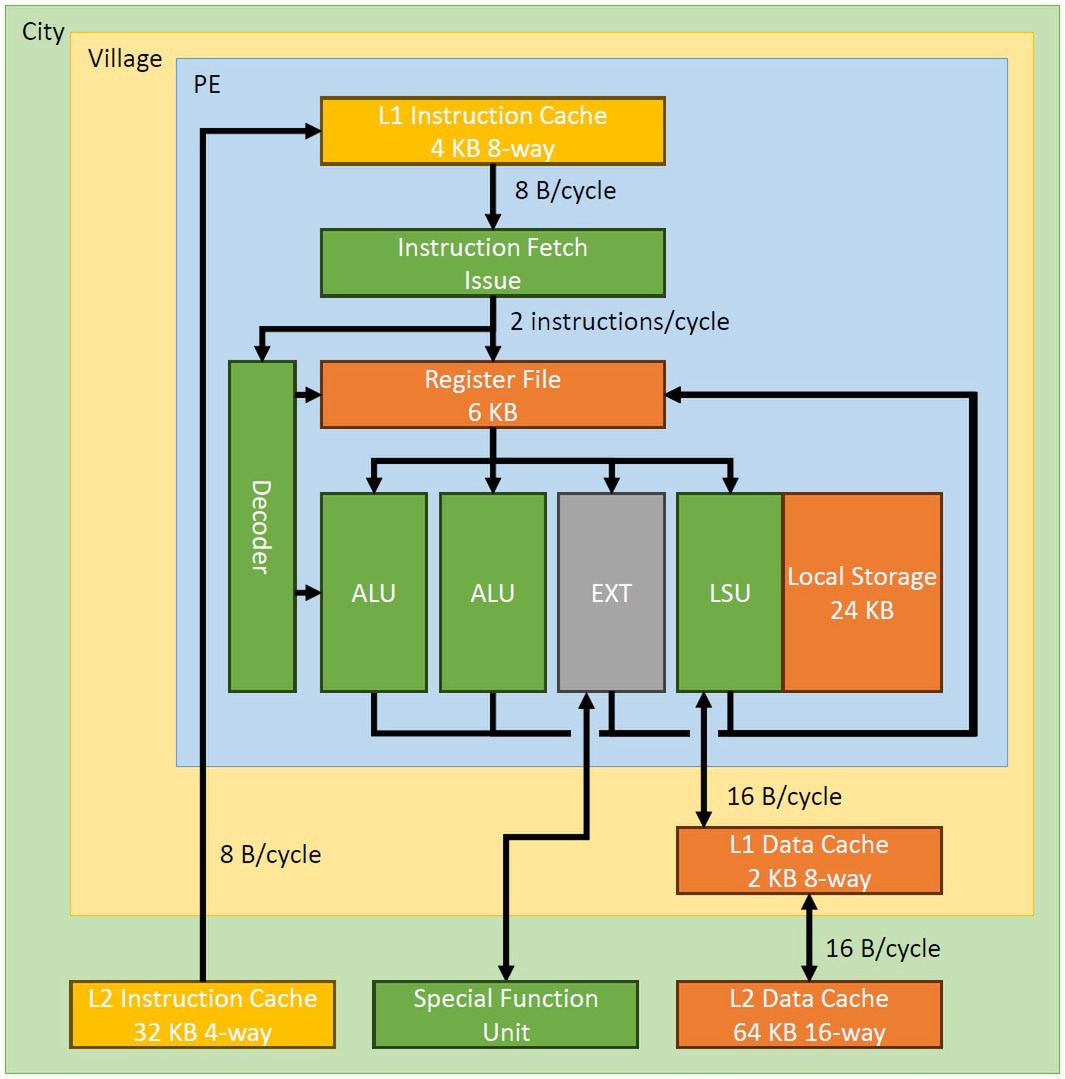

ここまでの話はPEZY-SCシリーズ全部に共通する話だが、ここからはSC4sの実装の話となる。PEそのものの構造は変わらない。

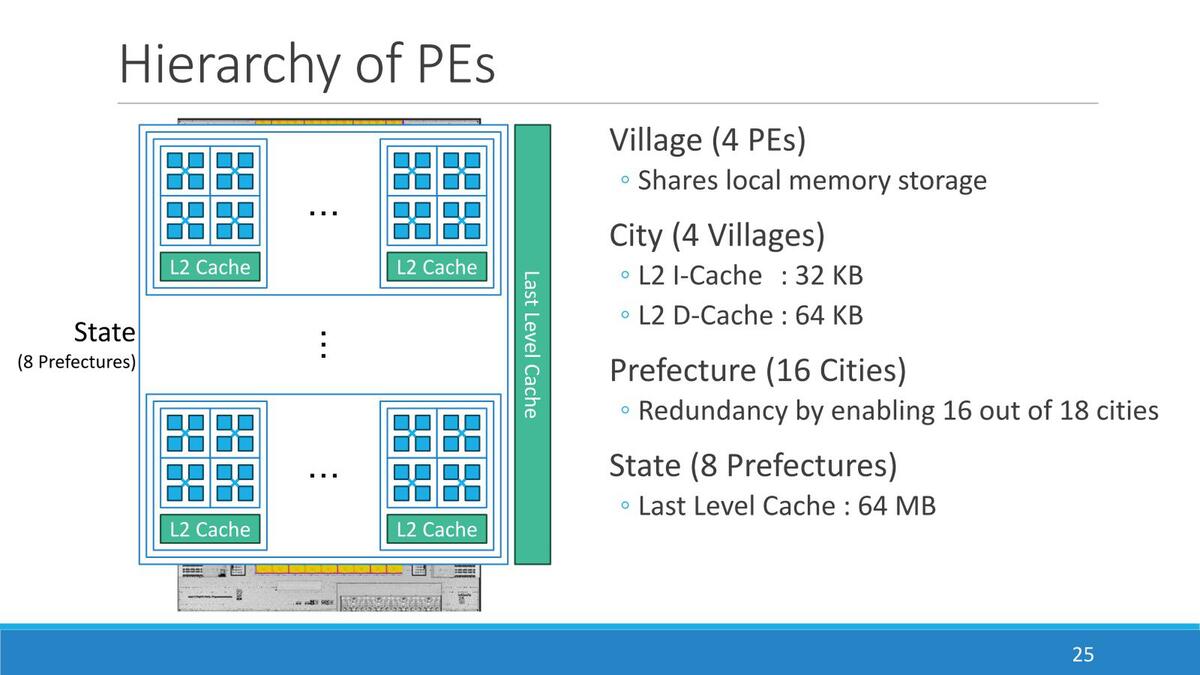

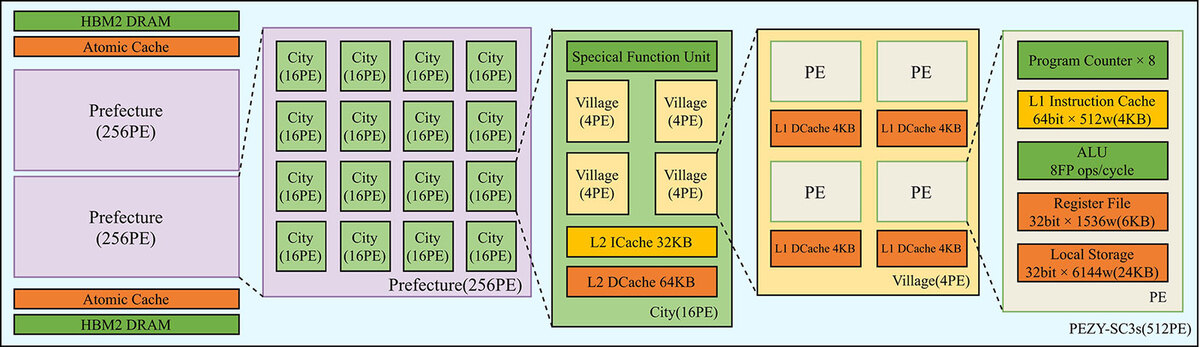

このPEを4つ集めたものをVillageと呼び、そのVillageを4つまとめたものをCityと呼ぶ。このCityには追加でL2 I-CacheとL2 D-Cacheが搭載される。

そのVillageを16個まとめたのがPrefecturesと呼ぶのだが、実際にはここで冗長Cityが2つ搭載されており、物理的には18 Cityで1 Prefectureを構成している。

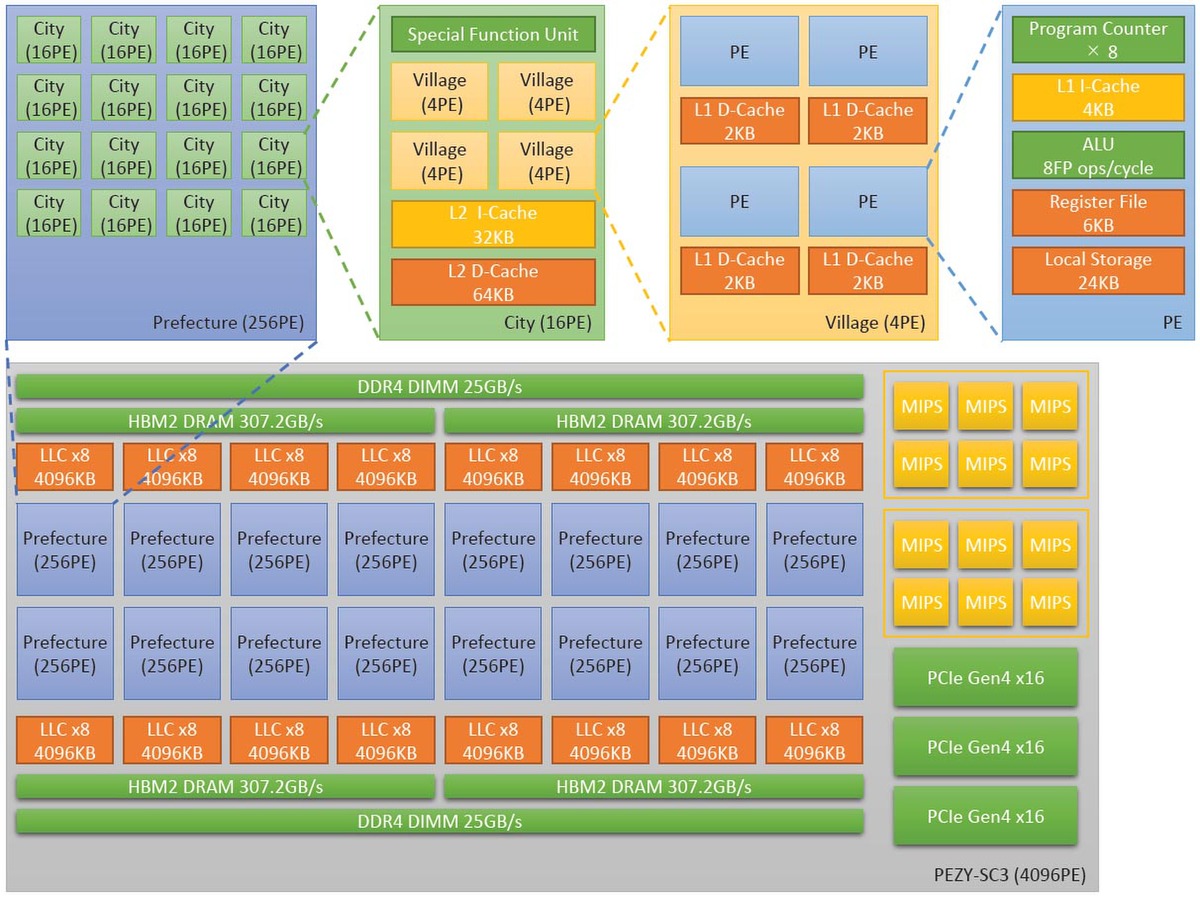

PEZY-SC4sがPEZY-SC3と異なるのはここからで、PEZY-SC4sは8 PrefectureでStateを構成しており、このStateに64MBのLLCが搭載されている。ところがPEZY-SC3では16 PrefectureでStateが構成されており、そこに64MBのLLCが搭載されていた。

さらに言えばPEZY-SC3sでは2 PrefectureでStateが構成されている。したがってPEZY-SC4sの性能はPEZY-SC3の半分程度でないとおかしいのだが、実際にはPEZY-SC3を上回る性能となっている。

Photo14がPEZY-SC3sまでのPEの内部構造であり、整数レジスターは64bit、浮動小数点は128bit SIMD構成でそれぞれ32個づつ搭載される。ALUで浮動小数点演算も可能であり、64bit倍精度ならALU1つ当たり2FLOP/サイクル、これが2つあるので4FLOP/サイクルという計算になる。

実際計算してみると、PEZY-SC3では実質3.2FLOP/サイクルほどになるが、これはメモリー不足に足を引っ張られている可能性が高い。対してPEZY-SC4では8.0FLOP/サイクルになっており、かといってALUを4つにしているとも思えないので、おそらくSIMDレジスタが256bit化されたものと思われるのだが、このあたりの詳細は今回公開されていない。

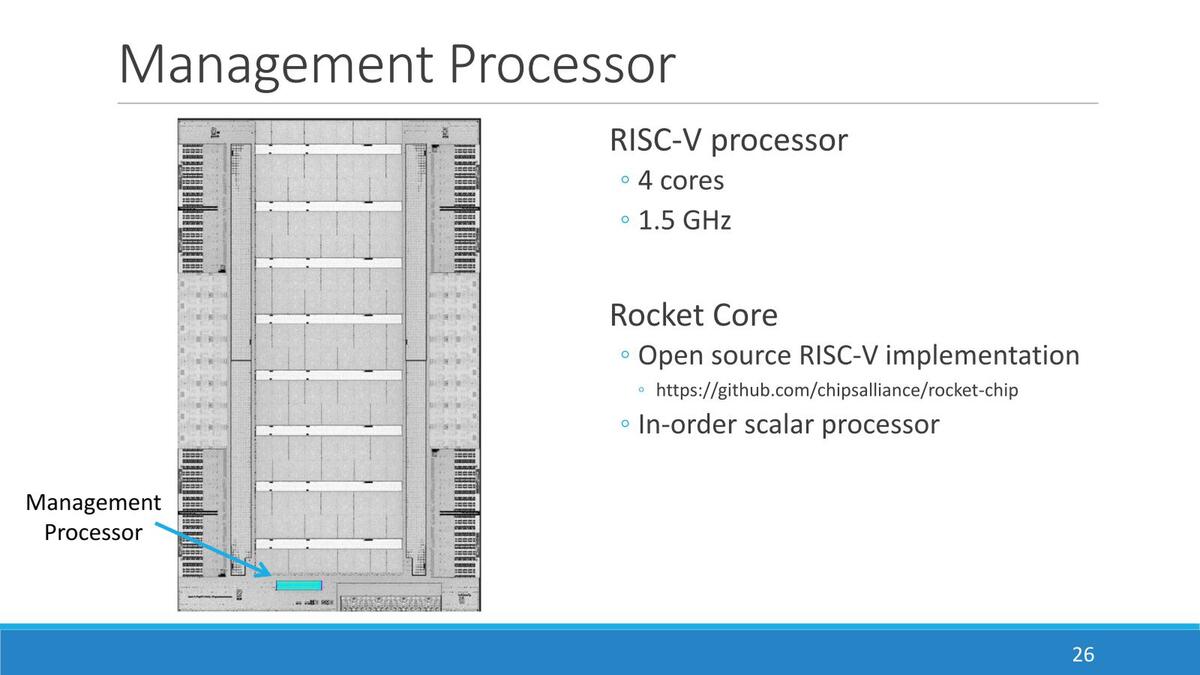

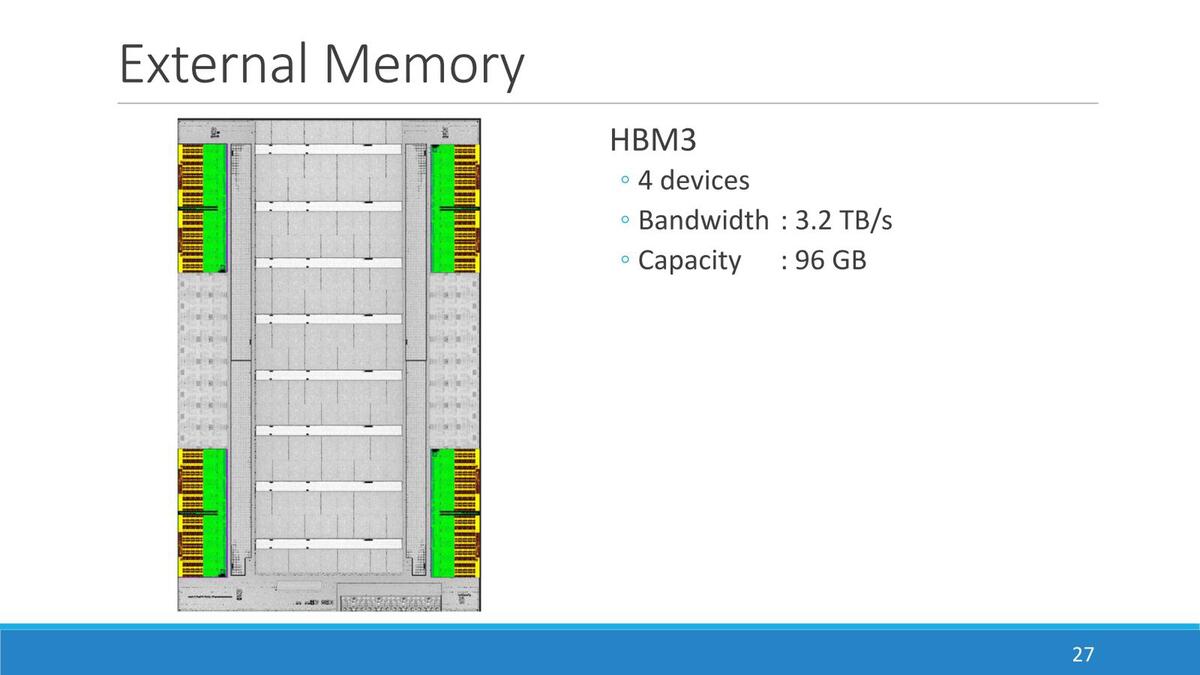

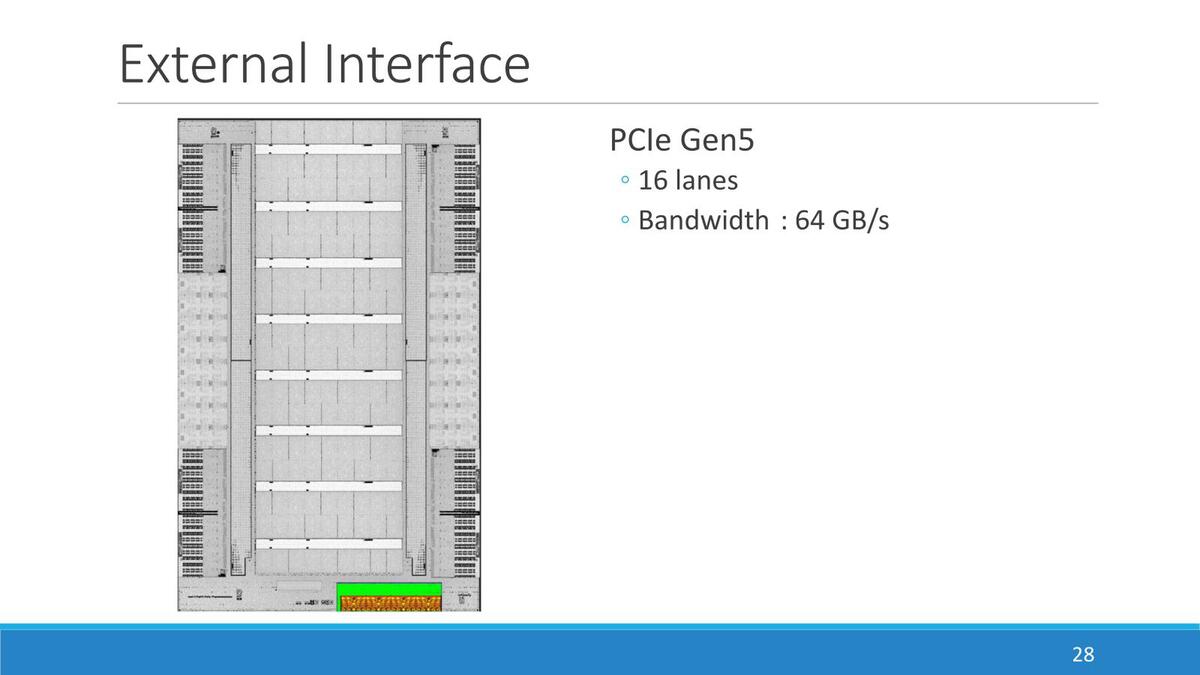

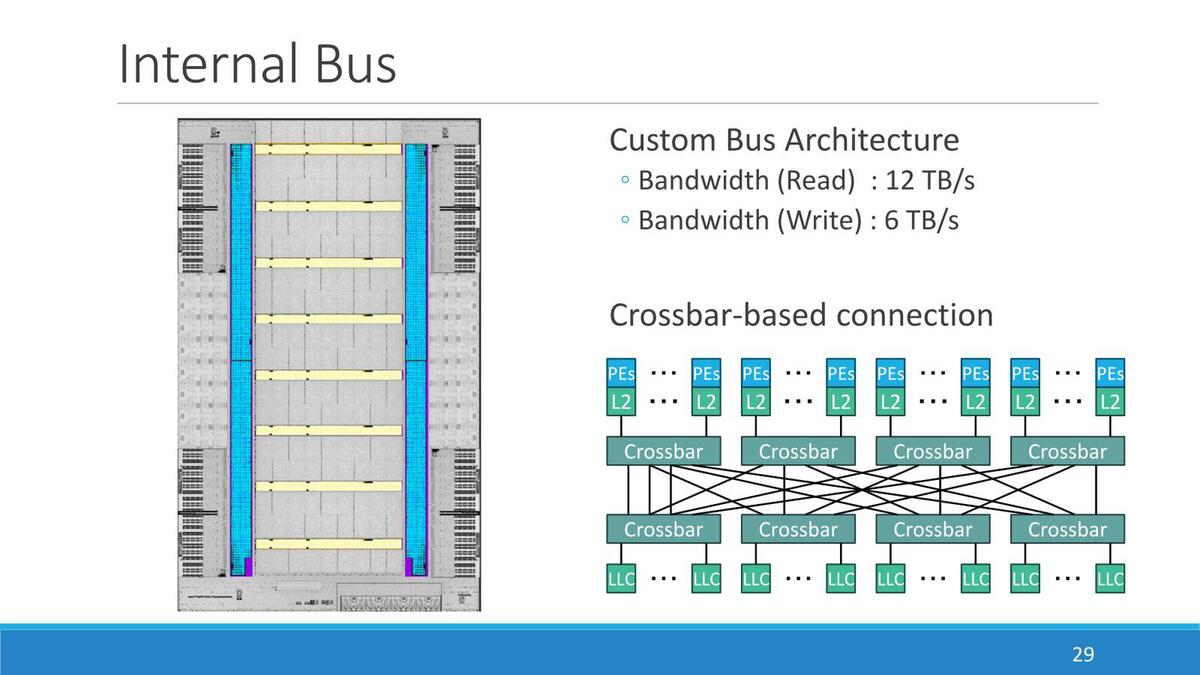

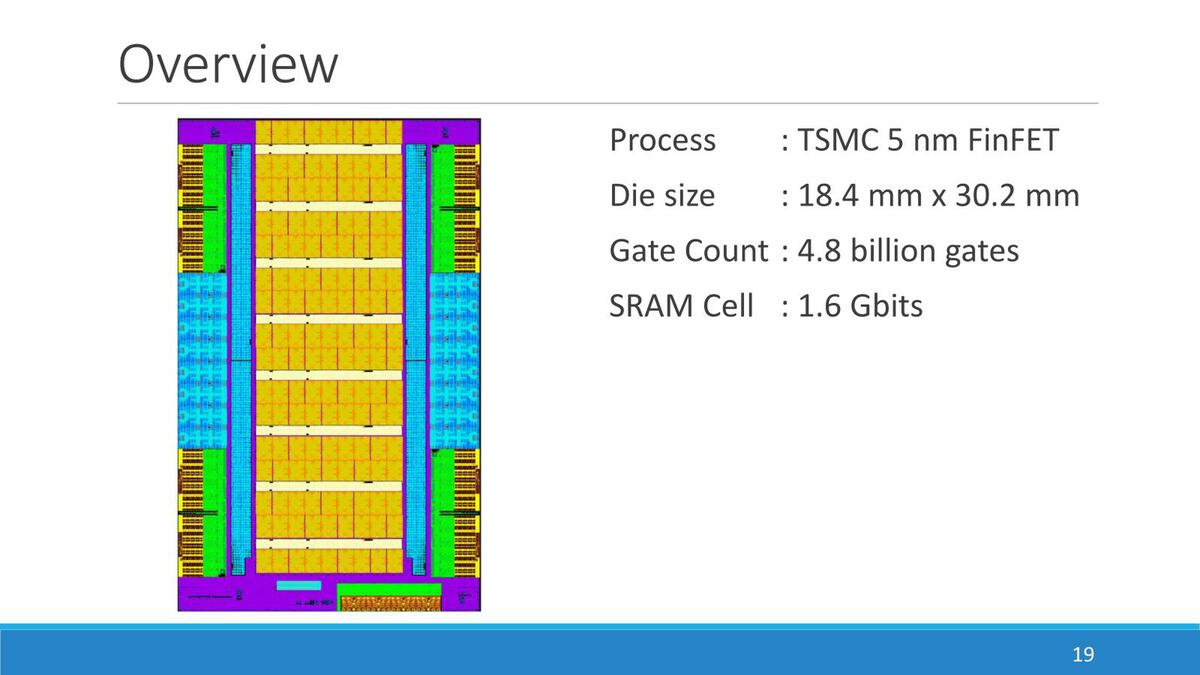

このPE(というかState)がチップの大半を占めており、他にマネジメント・プロセッサー、HBM3×4、PCIe Gen5×16、インターナル・バスなどが詰まっている。最終的なダイサイズは555.68mm2ほどになっている。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります