第845回

最大256MB共有キャッシュ対応で大規模処理も快適! Cuzcoが実現する高性能・拡張自在なRISC-Vプロセッサーの秘密

2025年10月13日 12時00分更新

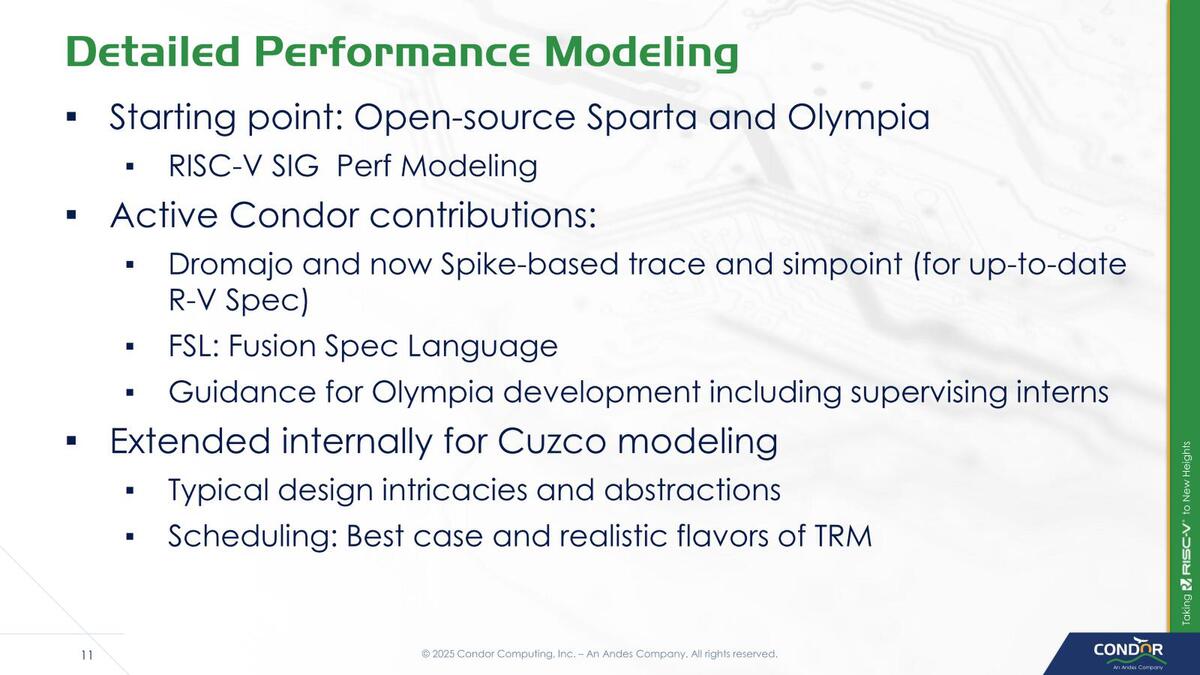

複雑なスケジューリング機構を廃し

消費電力を下げる

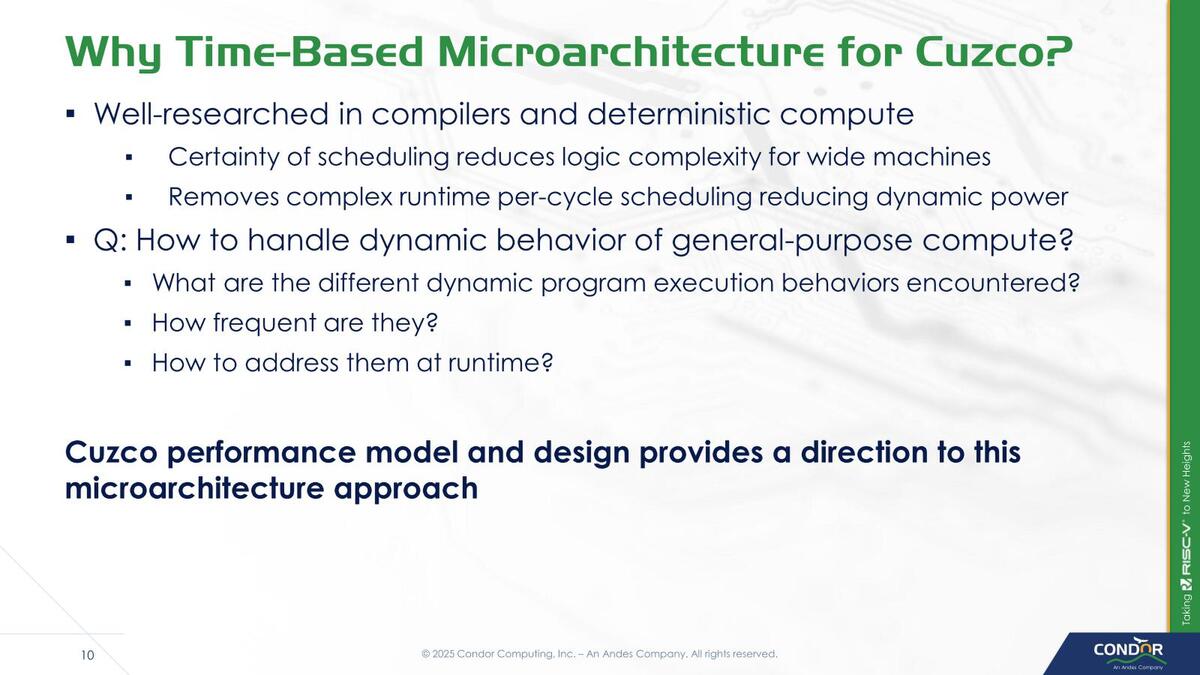

Time-Basedマイクロアーキテクチャーを採用した理由は、スケジューリングの最適化を容易にすることで、複雑なスケジューリング機構を廃し、結果的に消費電力を下げることにある、としている。

「How to handle dynamic behavior of general-purpose compute?」(汎用計算で、どうやって動的な命令の振る舞いを(time-baseで)制御できるのか?」の答えがおもしろい。要するに「これまでもできてなかったじゃん」である。まぁ、その通りだ

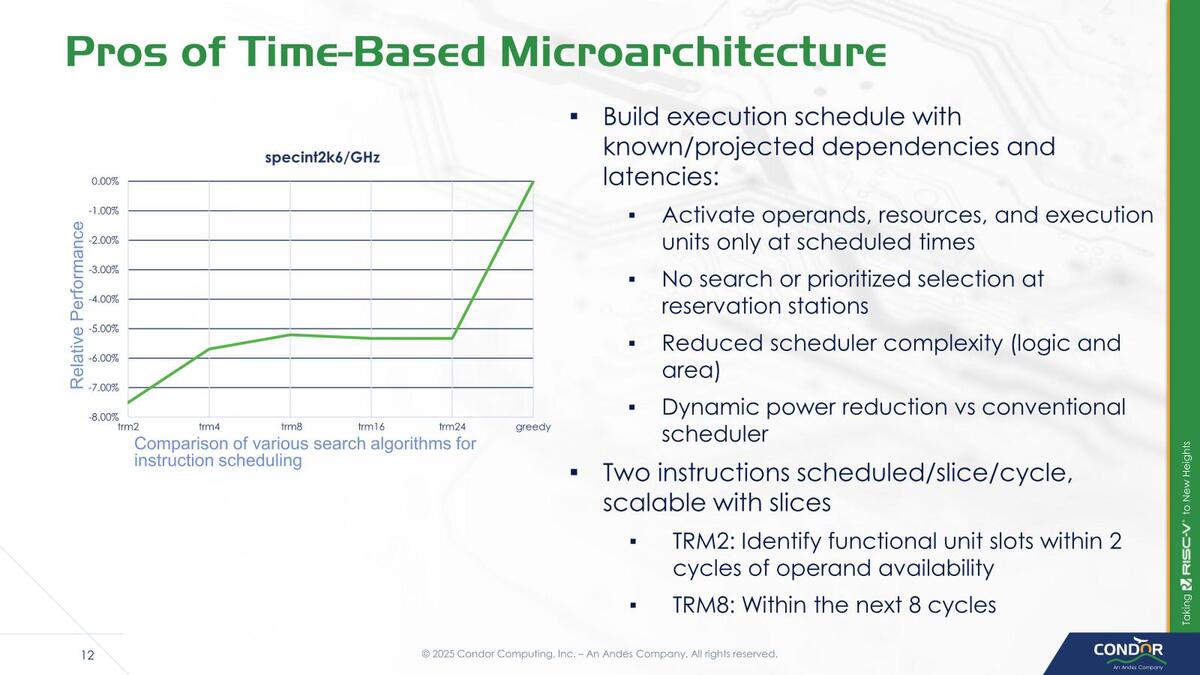

先に書いた「発行できる命令を即座に発行可能キューに叩き込んで実行ユニットに送り出す」のところは実際にはいろいろ省いている。通常キューには、実行可能な命令が複数並んでおり、それをどういう順番で送り出すかというのは結構難しい。しかもそれによって性能が変わる場合もある。これを簡単化できる、というのがCondorの主張である。

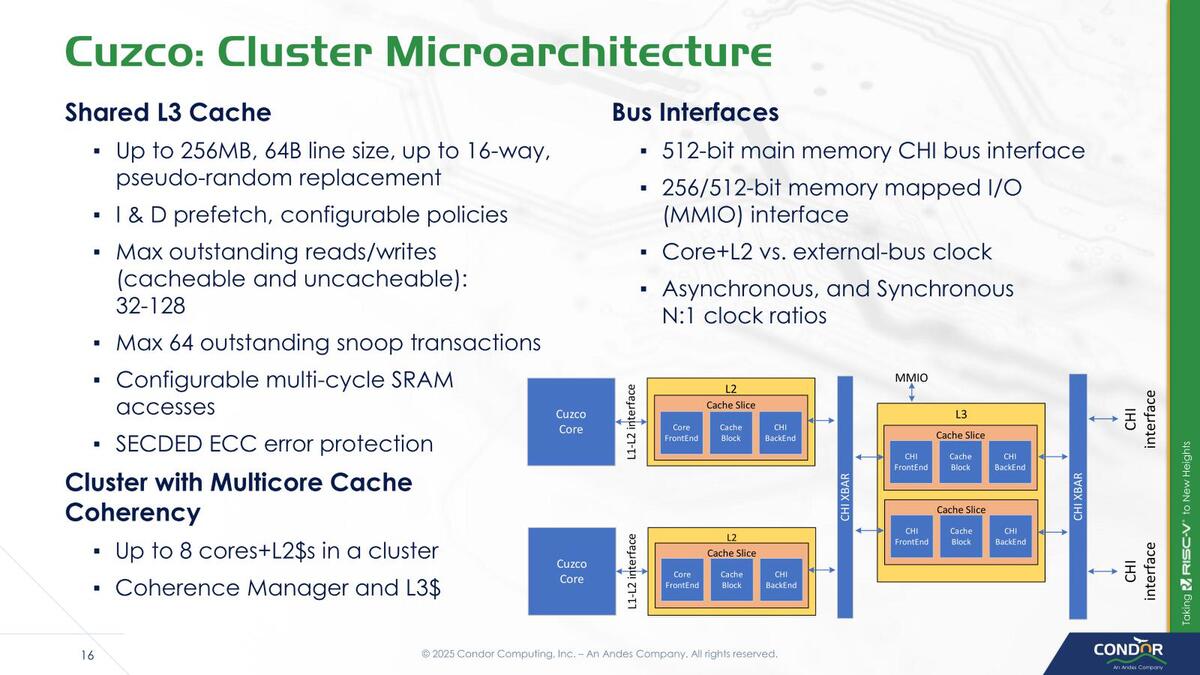

この性能に関しては、Spartaというモデリング/シミュレーションツールの上でolympiaというRISC-V Out-of-Orderプロセッサー用のモデルを利用して検証を開始したとしており、この結果がいくつか示された。

まず絶対的なパフォーマンスで言うと、従来型のスケジューラーに比べると5%ほどの低下を示すが、その一方で回路および消費電力を大幅に節約できたとする。またSliceの数と性能の比較が下の画像で、4スライスがちょうどバランスがいいことを示しているとする。

グラフの横軸は何サイクルまで記録するかを示し、8サイクルあたりがピークでそれ以上増やしてもあまり効果がない。ちなみにGreedyは従来型のスケジューラーのもの。SPECint 2006での結果とのこと

キャッシュ構成に関してはわりと自由に構成可能である。L1/L2がコアごとのPrivate CacheでL3がShared Cacheという構成だが、容量はかなり自由に選べるし、L3キャッシュに関しては速度を変更することもできる。

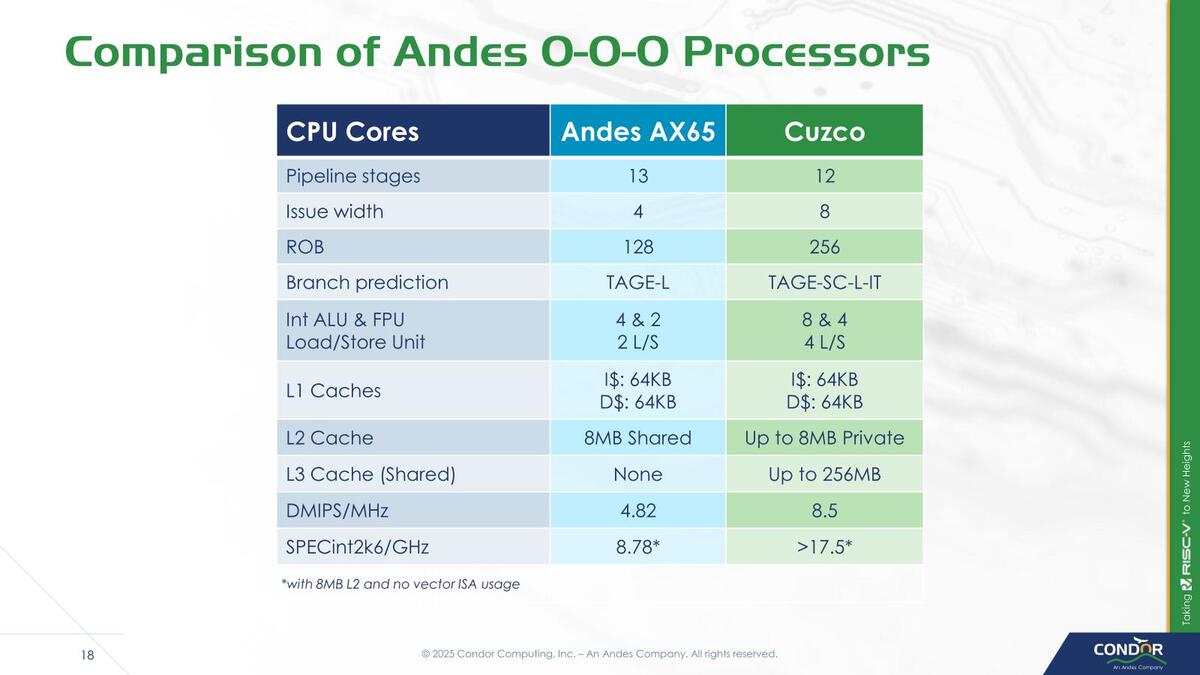

実際に親会社のAndes AX65との性能を比較した結果が下の画像だ。

AX65は4 wide decodeのOut-of-Order構成のプロセッサーなので、スペック的にはちょうどCuzcoの半分のサイズである。ただ、規模を倍にすれば性能が倍になることは普通はない(よくて5割増し程度)だから、SPECintの結果がきっちり倍になっているのはなかなか象徴的である。

すでにフロアプランも示されており、コアそのものはTSMCのN5プロセスで1.3mm2ほど、2MBのL2は1mm2なので、コア+L2がだいたい2.3mm2程度。仮にL2を最大の8MBにしても9.6mm2程度で、10mm2未満である。

動作周波数は速度優先で2.5GHz、密度優先で2GHzとやや控えめであるが、こちらは消費電力との兼ね合いもある。ゲート数で言えば700万個とそれほど大きくないサイズでこれだけのコアが実装できたのはなかなか優秀と言っていいだろう。

同じAndesのAX45(2命令同時実行のIn-Orderコア)がCortex-A72程度と言われており、AX65はCortex-7x相当(おそらくCortex-A78まではいかないはず。Cortex-A76あたりだろうか)程度の性能と目されるが、Cuzcoはこの倍になるので、Cortex-X2あたりと場合によっては互角の性能になるかもしれない。

AX65がデータセンター向けのコアという位置づけであり、実際軽負荷のサーバーであれば十分対応できる範疇だが、Cuzcoはクラウドサーバーにも使える程度の性能はありそうだ。といってもクラウド向けには単にコアだけあってもダメで、多数のコアを接続できるCoherent Networkが必要になる。ArmでいうところのCMN-700のようなものだ。今のところCondorではそうしたところまで手は回っていないようで、まずは性能が必要なアプリケーション・プロセッサー向けに活路を見出すつもりかもしれない。

Cuzcoは今年第4四半期からIPのライセンス提供を開始するとしている。さて、これを導入する顧客がどの程度集まるだろうか?

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります