第842回

双方向8Tbps伝送の次世代光インターコネクト! AyarLabsのTeraPHYがもたらす革新的光通信の詳細

2025年09月22日 12時00分更新

8対の光ファイバーに接続

双方向で8Tbps伝送を実現

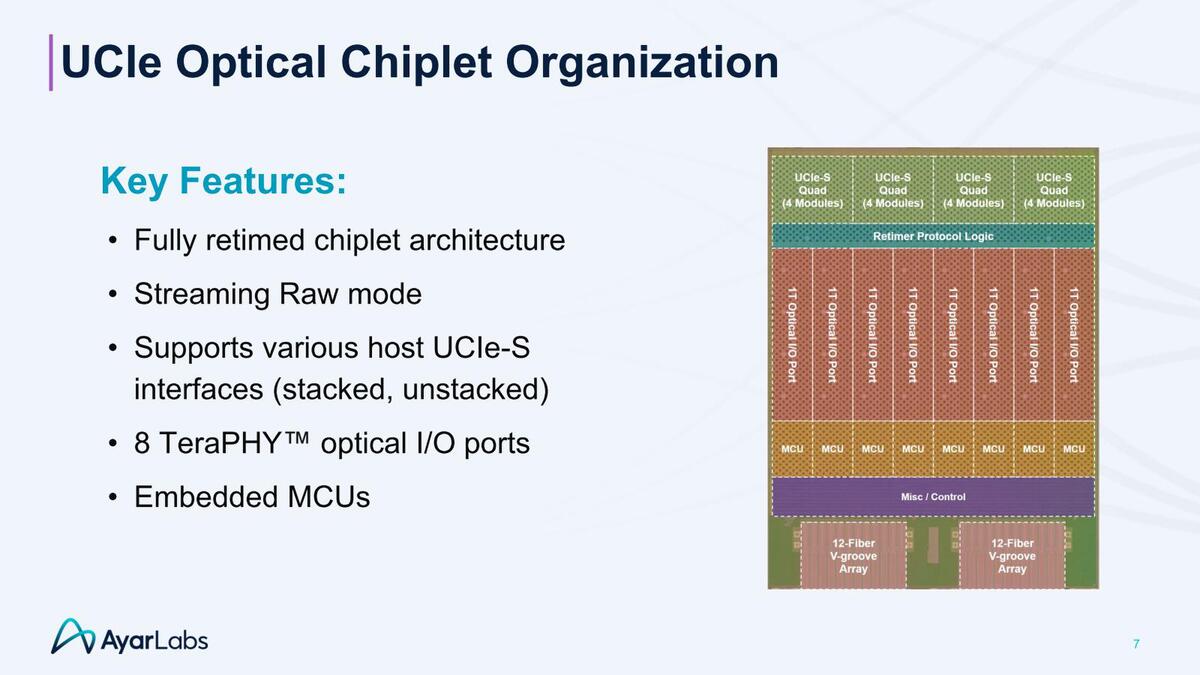

TeraPHYの内部構造の概略図が下の画像である。一番上がUCIe Standard Packageを4組まとめた構造で、これが8対の光ファイバーで送受信される構造になっている。

TeraPHY内部構造の概略図。V-Groove Arrayは12本分の光ファイバーが接続できるようになっているが、送受信の8本とは別にSuperNovaから入力される分が必要なのでこうなっているのだろう

信号の変換をするのが1T Optical I/O Moduleであり、モジュールやフォトダイオードに加えてトランスインピーダンスアンプや簡単なイコライザー、モジュール補正用(MRM:Micro Ring Modulatorベース)のフィードバック回路などが各々に含まれる格好と思われる。

それぞれのOptical I/O Moduleからは送受信用の光信号が一対ずつ出る格好となり、これが最終的に8対の光ファイバーに接続される構造と思われるが、送受信別に一番下のV-Groove Arrayで光ファイバーケーブルに接続されると考えられる。

またリタイマーは128bit分まとめての処理になっているはずだ。全ポートを横断するようにReTimer Protocol Logicが実装されているからだ。

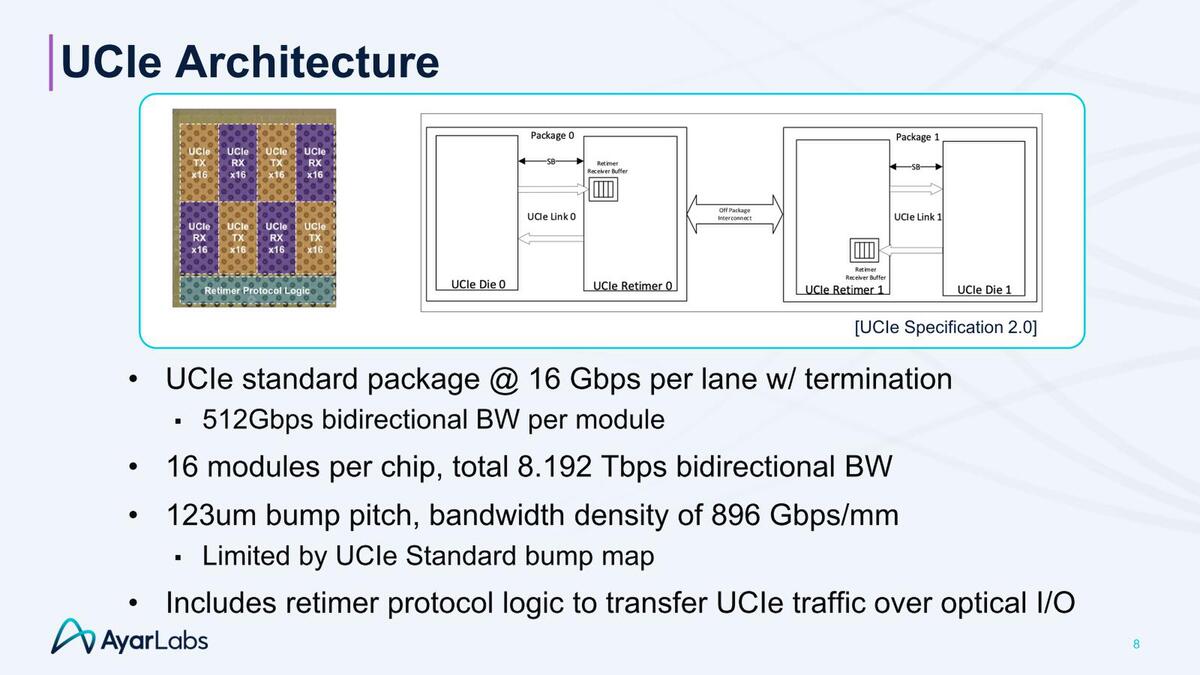

ところで信号速度であるが、電気信号の側から言うと16Gbpsとされる。16bit幅のUCIe Standard Package(なのでBump Pitchは123μmと結構大きめ)を4対まとめた、64bit幅のUCIe I/Fが、上の画像でいうところの"UCIe-S Quad"に相当する。

1つのモジュールあたり、16Gbps×16レーン×4モジュール=1Tbps(片方向)であり、これが4つで片方向あたり4Tbps、双方向で8Tbpsとなる計算だ。

Advanced PackageではなくStandard Packageを使ったのは、チップとの接続にシリコン・インターポーザーの必要性を廃したためだろう。Advanced Packageはシリコン・インターポーザーないし同等の配線密度の有機インターポーザーが必要だからだ。実際123μm程度のBumpであれば、通常のPackageに実装が可能である。

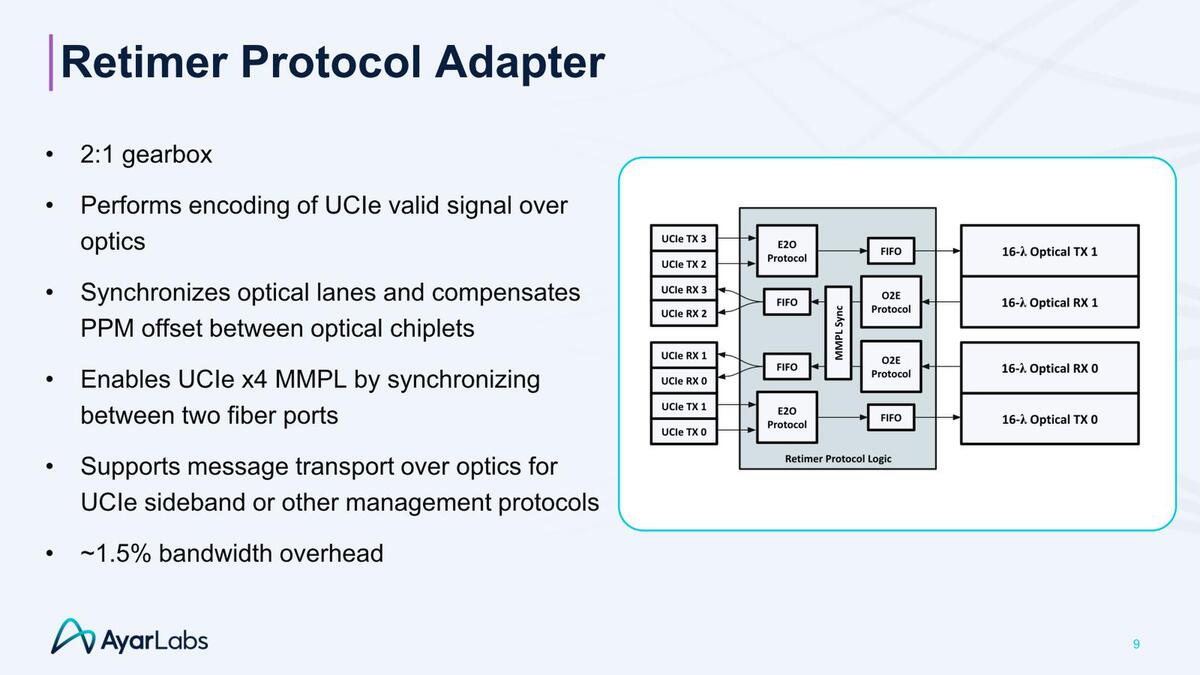

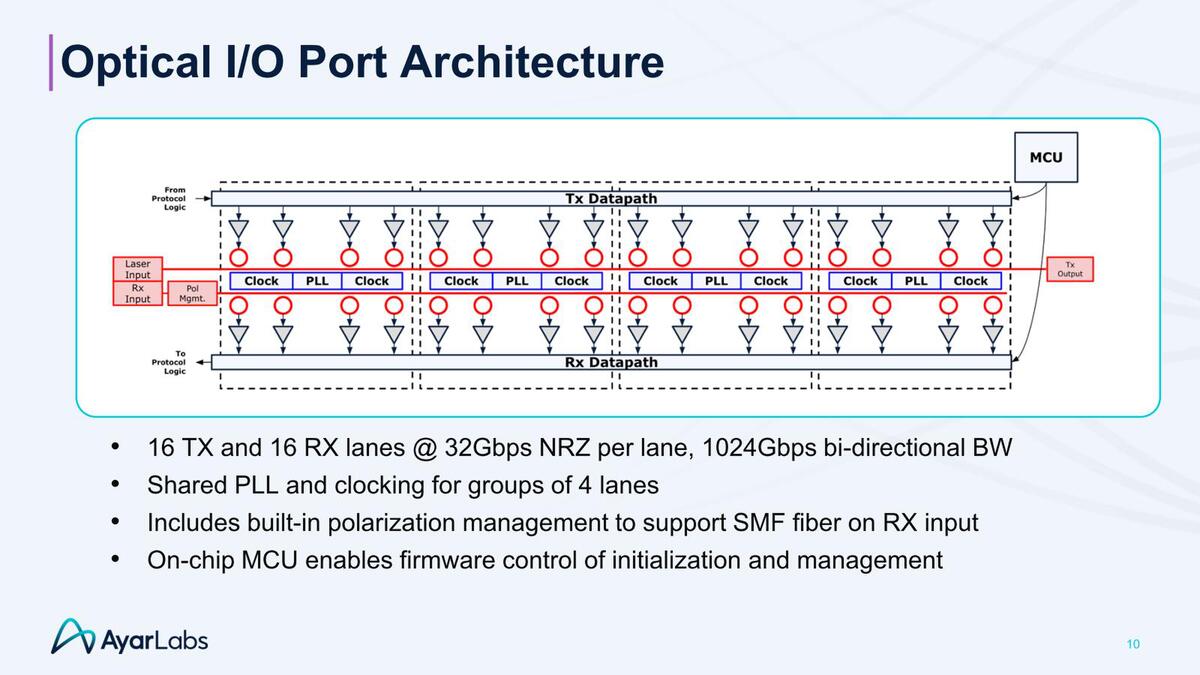

一方光信号であるが、こちらは32GbpsのNRZ(Non-Return-to-Zero:非ゼロ復帰方式)である。なのでそもそも信号速度が一致しないのだが、これをカバーするのがReTimer Protocol Adapterで、ここに2:1のギアボックスが入る。

ギアボックスというのは信号速度を変換するメカニズムのことで、ここで言えばTX0とTX1、TX2とTX3の2bitの信号(それぞれ16Gbps)をまとめて32Gbpsの1bit信号に変換するE2Oプロトコルが2:1のギアボックスに相当する。

逆に受信側は、32Gbps/1bitの信号を16Gbps/2bitの信号に変換する必要があるが、これは光信号を電気信号に変換したあとでFIFO(First-In, First-Out:先入れ先出し)に突っ込み、1:2で変換する格好になっている。

なお、本文にあるMMPLはMulti-Module PHY Logicの略である。今回の場合、4bitの電気信号を2bitの光信号として送り出す(のと、2bitの光信号を4bitの電気信号にして送り出す)必要があり、この4bit分の電気信号のPHYと2bit分の光信号のPHYは各々同期して動く必要がある。これを実装している、という話である。

一方の光信号であるが、信号速度は32GT/秒のNRZで1波長あたり32Gbpsである。前述のとおり16波長のDWDMを構成している関係で、1本の光ファイバーは片方向あたり32×16=512Gbpsの転送速度を持つ。これを8本用意することで、片方向当たり4Tbps、双方向で8Tbpsの帯域となるわけだ。

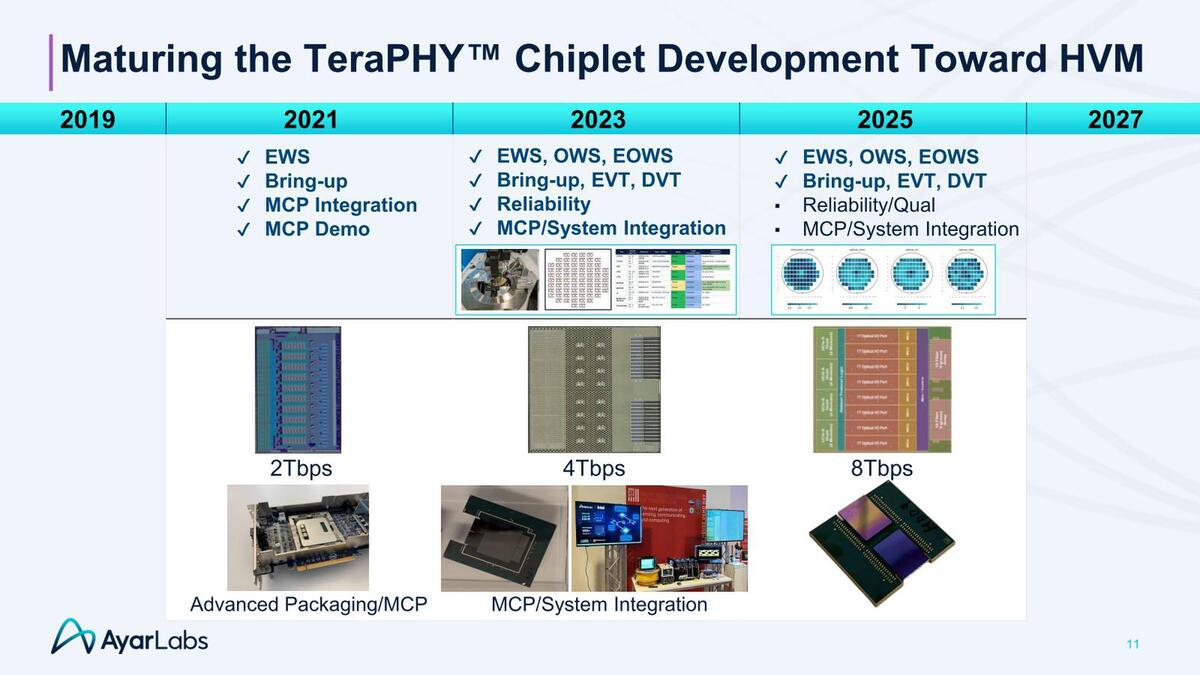

このTeraPHYもいきなり登場したわけではなく、まず2021年には2Tbpsのものが製造されて検証し、2023年には4Tbps、そして今年8Tbpsのものが登場したとする。

上段、太字が完了したテスト項目である。すでに第2世代のTeraPHYはHVM(High Volume Manufacturing:大量量産)に対応できるとしている。第1世代は量産に必要なテストをしていないので、これはあくまでもデモ向けである

ちなみに用語は以下のとおり。

| 用語と意味 | ||||||

|---|---|---|---|---|---|---|

| EWS | Early Wireout。最初のバージョンのテープアウトを完了し、基本機能の検証が終わった | |||||

| OWS | Official Wireout。正式なテープアウト | |||||

| EOWS | Engineering Official Wireout。エンジニアリングサンプルの正式なテープアウト | |||||

| Bring-up | ハードウェア起動。電源が入り、基本テストや機能デバッグに成功し、チップが動作可能であることを確認 | |||||

| EVT | Engineering Validation Test。エンジニアリングサンプル上で包括的な機能テストを実施し、仕様を満たしていることの検証が完了している | |||||

| DVT | Design Validation Test。最終製品に近い仕様での信頼性・互換性その他のテストが完了し、設計の量産適合性を確認 | |||||

| Reliability | 信頼性テスト | |||||

| Qual | Qualification。品質認証 | |||||

| MCP Integration | Multi Chip Packageでの統合の確認 | |||||

| MCP Demo | Multi Chip Package上での相互通信のデモを実施 | |||||

| System Integration | MCP Demoの上位レベルで、システム全体としての統合の確認 | |||||

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります