第841回

Gen1で3倍、Gen2で14倍の帯域幅を実現! Celestial AIのPFLinkがネットワークスイッチを劇的に進化させる

2025年09月15日 12時00分更新

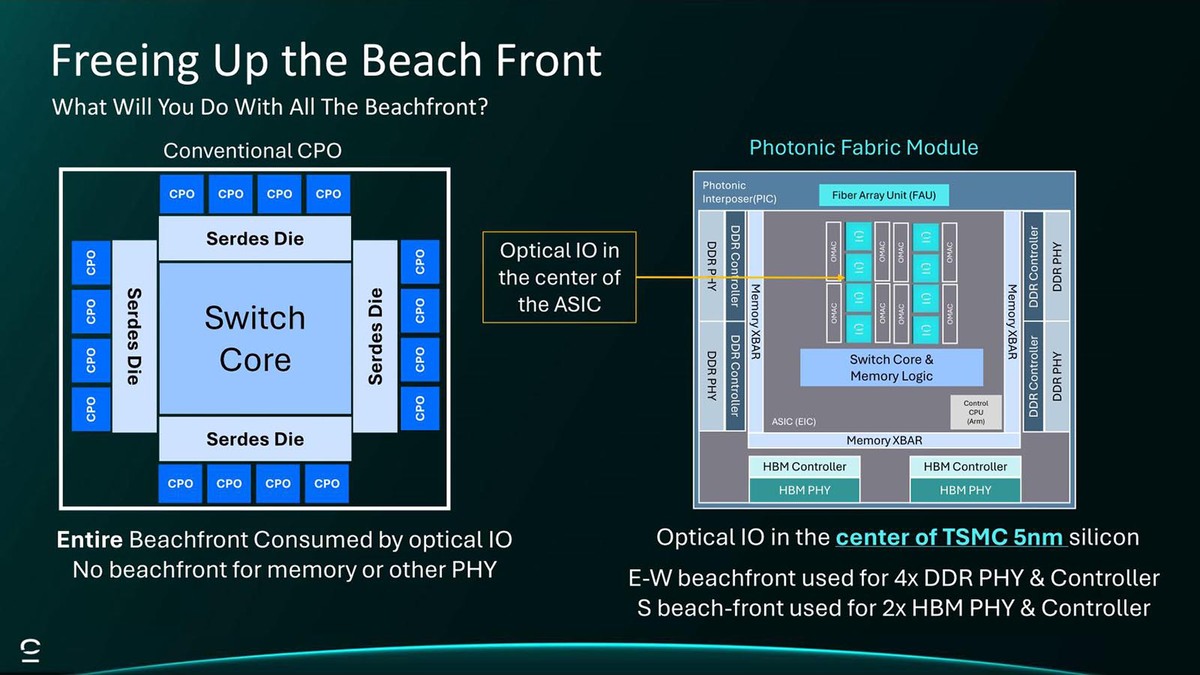

ASICにEICを組み込む必要がある

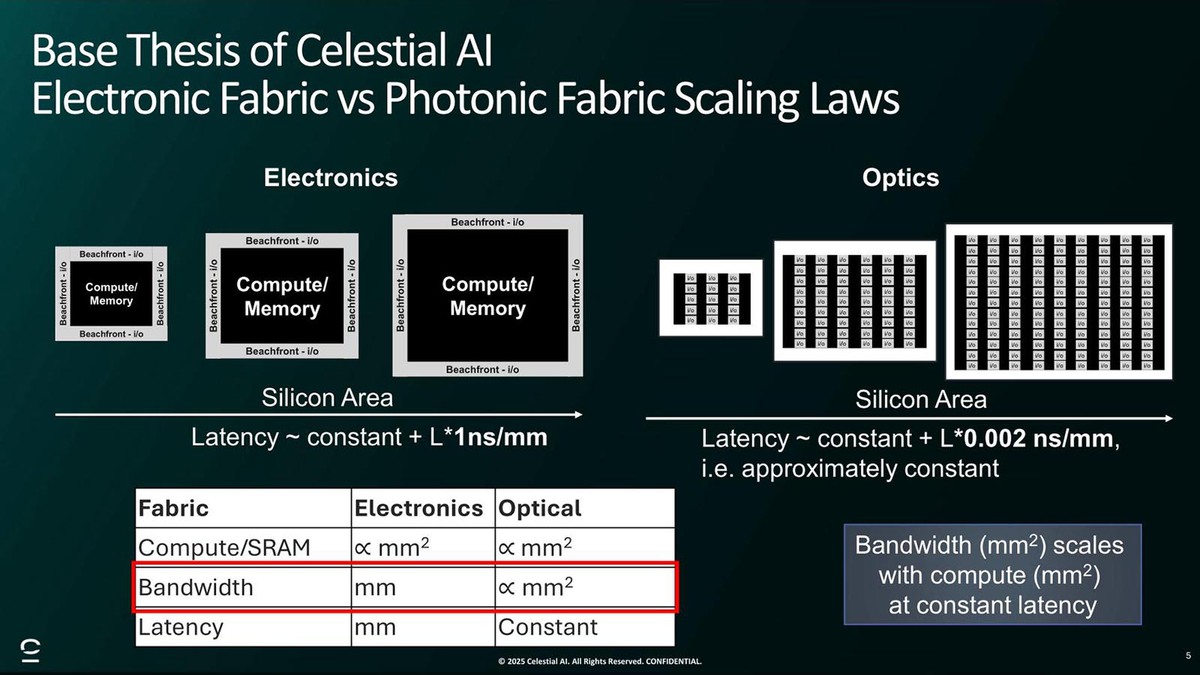

レーン数や帯域はチップの面積に比例する

Celestial AIの実装方法ではユーザーのASICにEICを組み込む必要があるのだが、従来の電気信号と異なるのはチップ周辺に実装する必要がないことで、この結果としてレーン数や帯域はチップの長さではなく面積に比例する、とする。

レーン数や帯域は面積に比例する。これはLightmatterも同じことを言っていた

実際に一辺28mm程度のチップにHBMが6つ接続されるチップの、外部への帯域を従来型のCPO(Chip Package On)と比較した場合、Gen 1で3倍、Gen 2では14倍の帯域が利用できるとしている。

従来型の場合、チップの上辺にUCIeなどのI/Fを集め、その先にEICとPICをワンチップ化したCPOを接続するので、おおむねCPOあたり4Tbps(これはUCIeの配線密度×速度で律速される)に留まるが、Celestial AIの場合はここにFAUのみが位置しており、光信号はXPUの真下で送受信されるのでずっと帯域が増やせる、という発想である

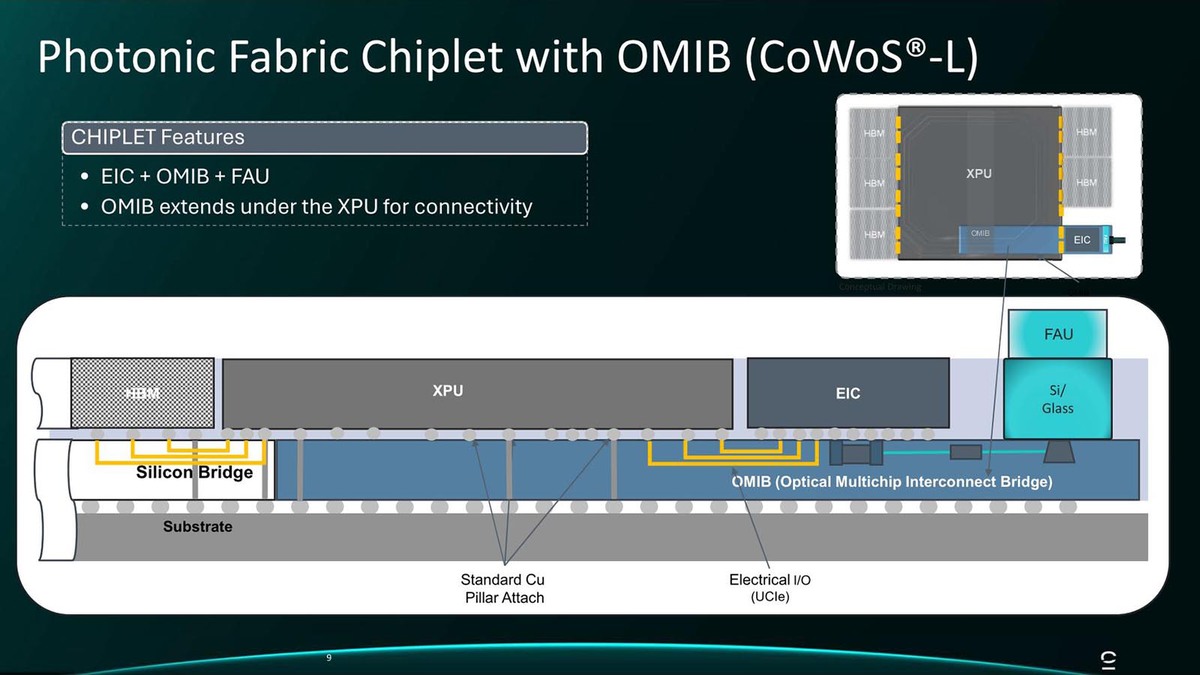

超短距離接続用のPFLinkが「OMIB」

インテルのEMIBのOptical版に相当

ここで突如登場したのがOMIBである(図の右下)。OMIBというのはOptical Multi-chip Interconnect Bridgeの略だそうで、隣接するダイ同士を接続するのであれば、結局そのI/Fはダイの端に位置することになる。

そこでその間をつなぐ簡単なブリッジを用意するという話で、要するにインテルのEMIBのOptical版的な位置付けである(大きさは異なるが)。つまり超短距離接続用のPFLinkがOMIBという扱いのようだ。このOMIBの詳細が下の画像だ。

おもしろいのは、ダイ同士の接続そのものはEC2C(Electrical Chip-to-Chip)で行なうが、そこから外部に引っ張り出す信号はOpticalになっていることだ。つまりこの図では4つのダイが相互接続されている構造だが、OMIBを使うとこの隣に置かれた別のチップ上のダイとも相互接続できるようになるというわけだ。

そのOMIBの断面図が下の画像である。EC2CはやはりUCIeをそのまま使う形で、そこからEICを経てOMIB内部のモジュラーから光信号を出すかたちになる。ベースはCoWoS-Lだそうだが、ここまで大きなインターポーザーをCoWoS-Lで作れるというのは意外だった。

個人的にはOMIBの大きさが結構大きいのが気になる。これはPFLinkのインターポーザーとの干渉もあり得そうで、いっそPFLinkで統合した方が良かったのでは? と思わなくもないが、ダイ同士の接続「のみ」を拡張したい場合に提供される(全体を光化したい場合はPFLinkを使う)ということなのかもしれない

このPFLinkを製品に応用するとどうなるか? ということで、ネットワークスイッチをPFLink化した例が下の画像となる。

左の図はBroadcomのTomahawkを連想させる。スイッチはなべてこんな具合だが

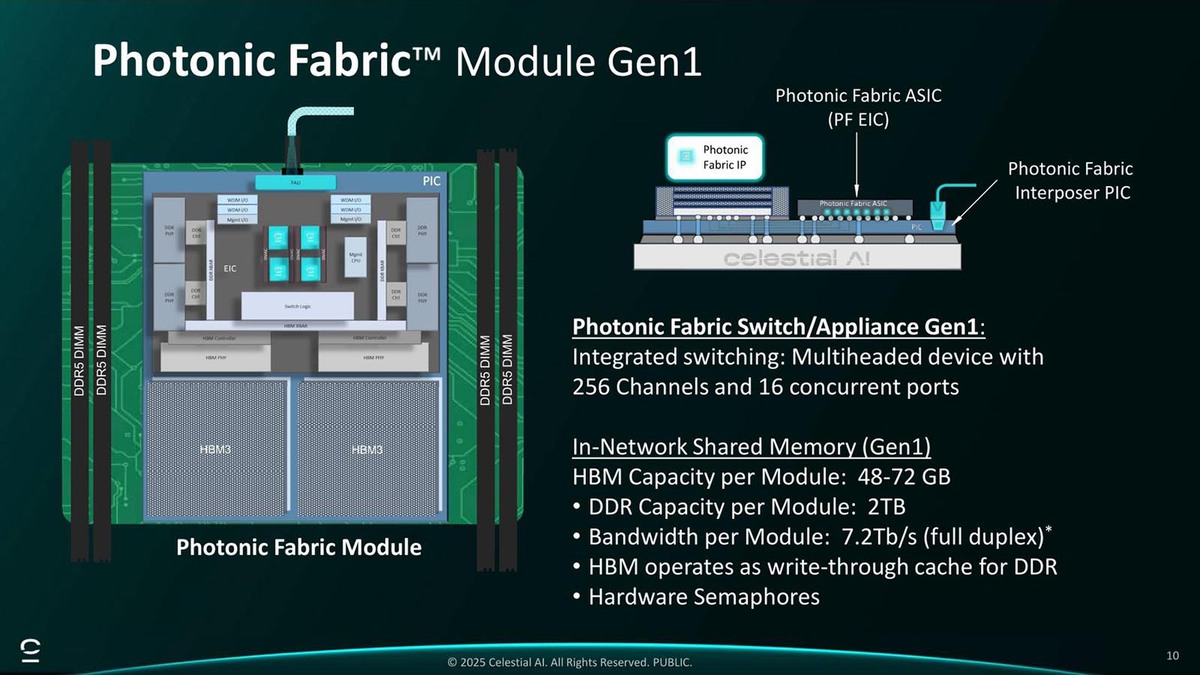

従来なら外部I/Oのためにチップ周辺にCPOを配する必要があるので、左図のようにそのほかのI/Fが一切用意できないことになるが、PFLinkを利用すると右図のように外部接続用にはスイッチASICの真下から光信号を出せるので、ASICの上辺にFAU用のスペースだけを設ければ良く、左右や下辺にはDDRやHBMのI/Fを搭載できる。これにより、ネットワークスイッチが大量のメモリーを利用できるようになる。

48~72GBの高速キャッシュDRAM+2TBのバッファが使えるということは、スイッチで行なえる処理が大幅に増える(複雑なパターンマッチングなども可能になる)ということでもあるし、なんならスイッチ兼キャッシュサーバーとすることもできるようになる

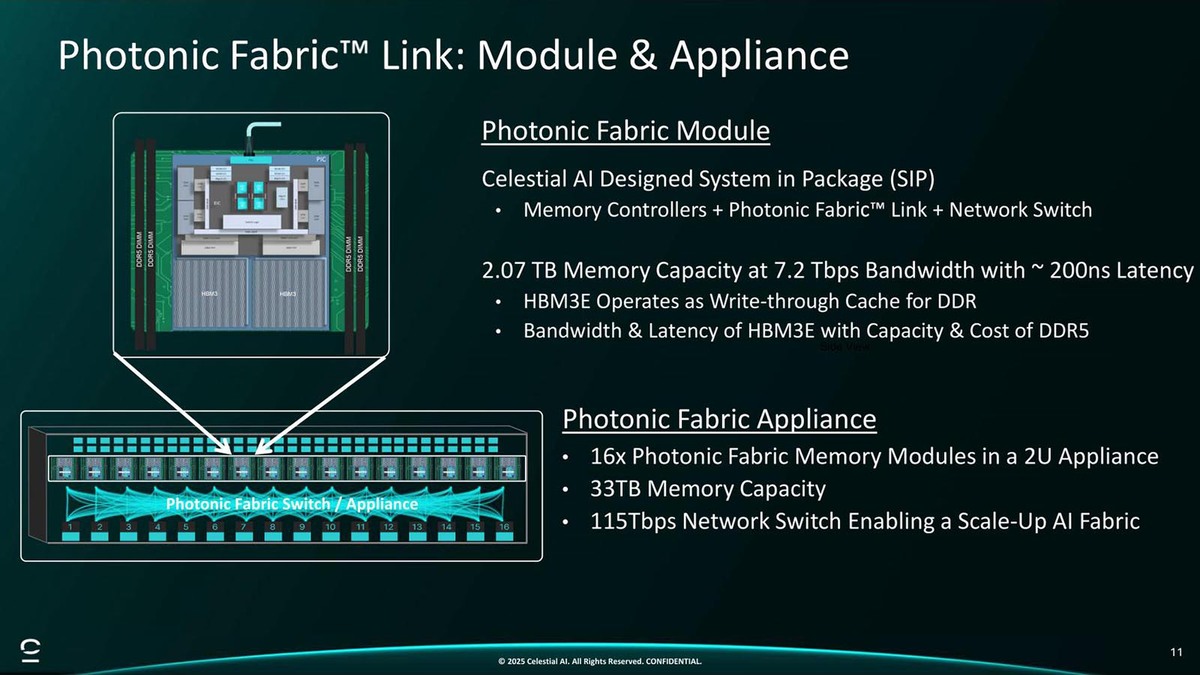

第1世代のPFLinkを使ったケースでは7.2Tbps程度のスイッチング性能なので、これは例えばTomahawk 5(51.2Tbps)に比べるとだいぶ少ないという見方もできるが、これを複数組み合わせることでスケールアップ・ファブリックが構築できるとしている。

このスライドには出ていないが、Mahatme氏の講演の方ではPenguin Solutionsの名前が挙がっていた。115Tbpsのスイッチング性能と33TBのメモリーを持つ製品をまさに今開発中なのかもしれない

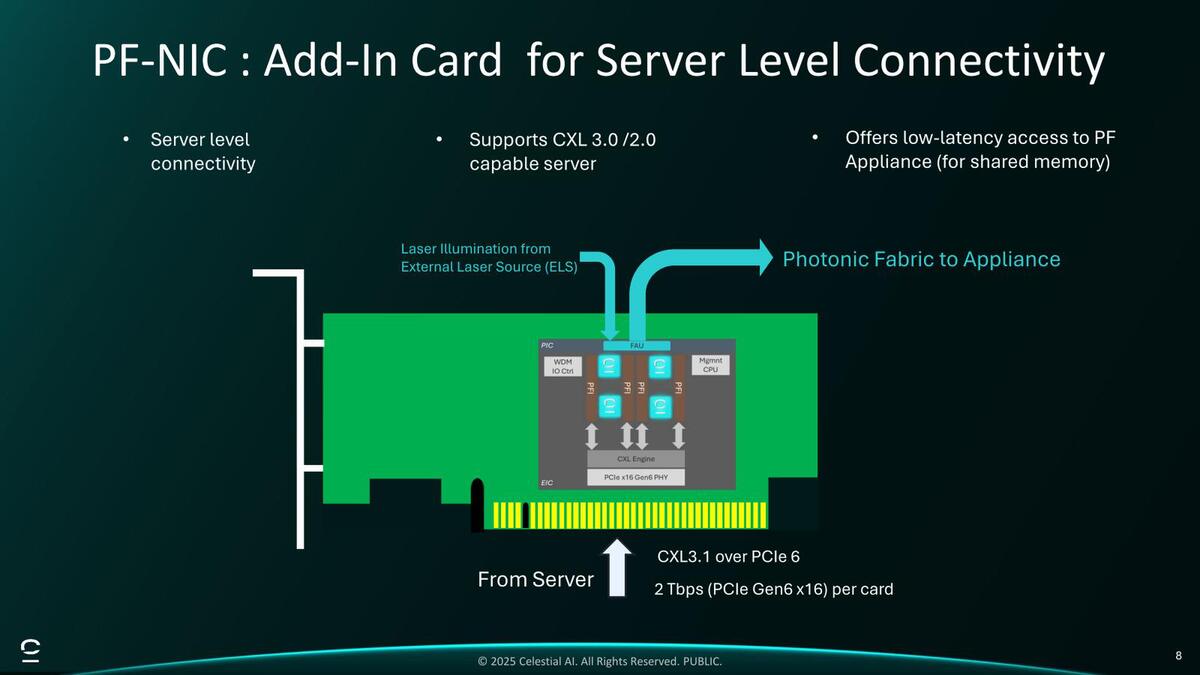

ただファブリックといっても、PFLinkの利用する光信号はイーサネットとは互換性がない(なにしろDSP Lessという時点でもうイーサネットのプロトコルと異なっているのが明白である)のだが、このためにPF-NICというサーバー向けの製品も用意するらしい。

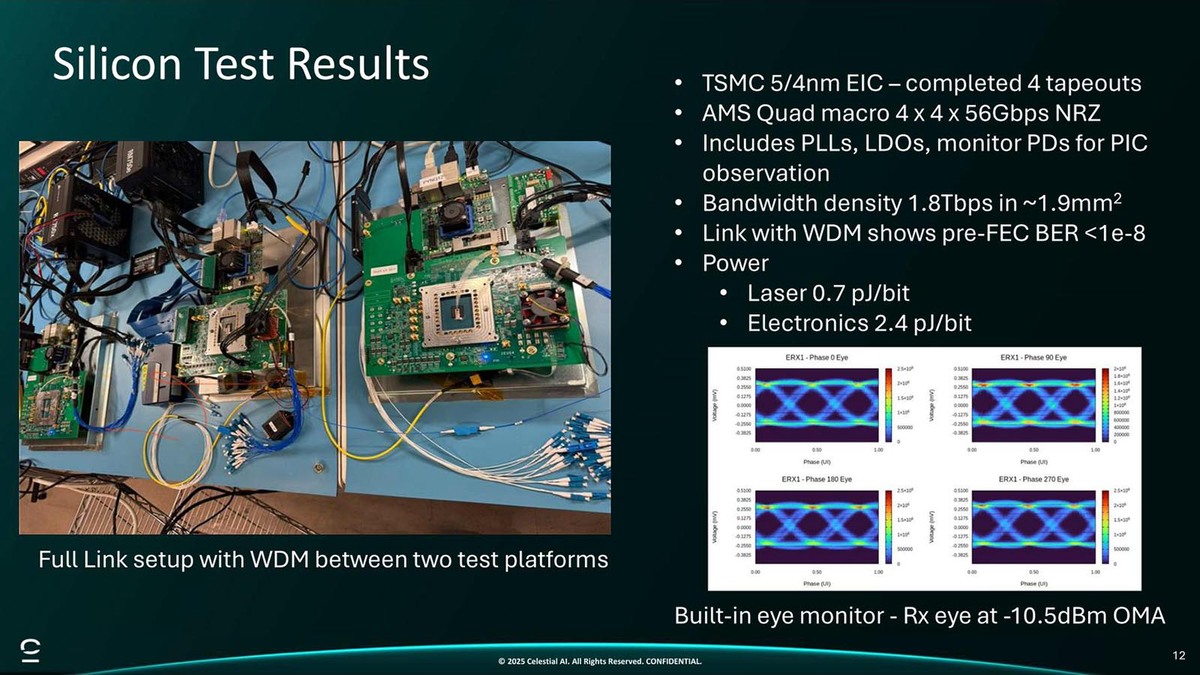

すでにEICに関しては4製品のテープアウトが完了しており、56Gbpsの4波長WDM(つまり光ファイバー1本あたり224Gbps)の送受信が可能であることが実証されているとする。また1.9mm2あたり1.8Tbpsの信号が出せるというのは、信号密度としては悪くない数字である。

XPU向けに採用されるとおもしろくなりそう

というわけで意気揚々であるCelestial AIであるが、いろいろと不明な点は多い。信号速度は現在56GT/秒で、4波長のWDMを利用しているとするが、EAMを使う限りMUX/DEMUXが必要になるし、これ以上の波長を重ねるのも厳しそうに思われる。

かといってこの先さらに高速化するとBERが相当悪化しそうだし、PAM4などを入れるのも同じである。先にGen2ではさらに高速化されるという話が出てきたが、そのGen2がどんな実装になるのか現時点では公表されていない。

またCoWoSを前提にしているが、CoWoSもシリコン・インターポーザーのCoWoS-S(やCoWoS-L)からオーガニック・インターポーザーのCoWoS-Rにシフトしつつある。この主な要因はダイの大型化にともなうパッケージの大径化であるが、CoWoS-RとPFLinkの親和性がどの程度か不明である。そもそも導光路をどうCoWoS内に構築するかの説明が一切ないのだ。

7つ上の画像で、"Compatible:CoWoS & glass panel integration"とか書いてあるあたり、オーガニック・インターポーザーとの親和性はあまり良くない気もする。また、一時期に比べ、ガラス基板への熱が業界全体で冷え込みつつあるのも懸念材料である。

そういう疑問点はいくつかあるのだが、これはこれでおもしろい取り組みであろうかと思う。最初はスイッチ向けだとは思うが、あるいは将来はXPU向けなどにも使われるかもしれない。個人的にはそれこそMVIDIAのNVLinkやAMDのInfinity Fabricのような、特定の1社で閉じている規格にこそ、この仕組みは向いている気がする。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります