第841回

Gen1で3倍、Gen2で14倍の帯域幅を実現! Celestial AIのPFLinkがネットワークスイッチを劇的に進化させる

2025年09月15日 12時00分更新

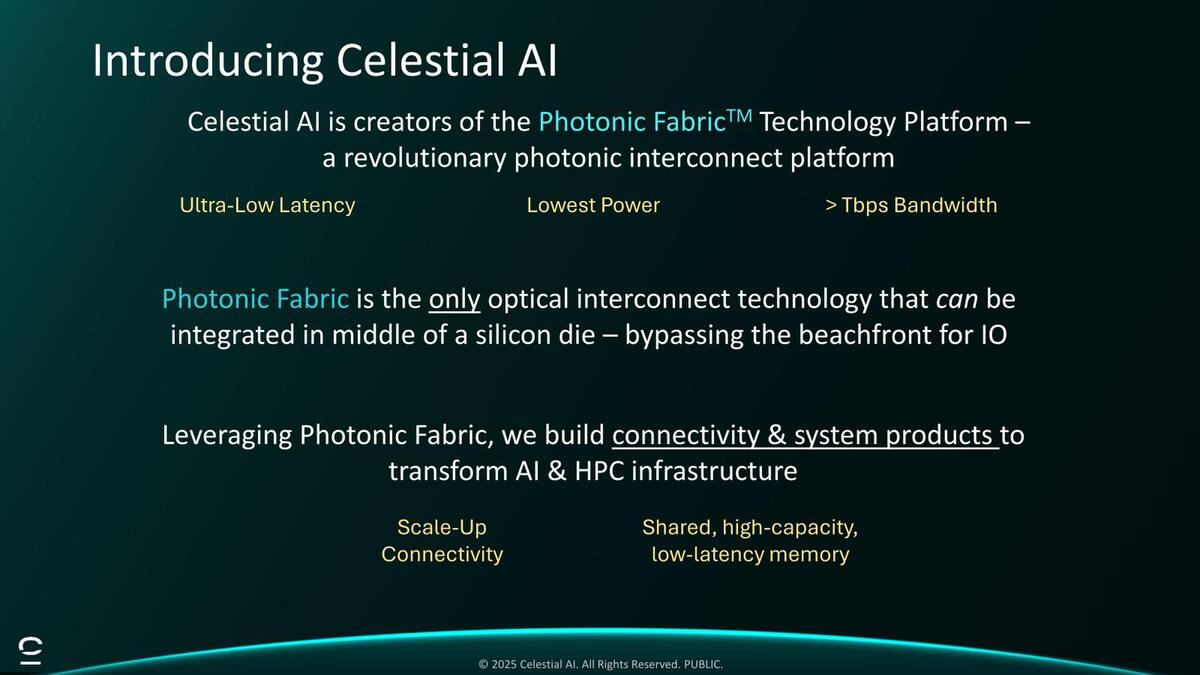

2025年8月21~22日に開催されたHot Interconnects 2025の解説、最後を飾るのはCelestial AIである。Celestial AIという社名であるが、同社は創業当時から光インターコネクトだけを開発している。紛らわしい感じもするが、その光インターコネクトのターゲットがAIプロセッサーやGPUであることを考えれば、間違っているわけでもない。ひょっとするとベンチャーキャピタルなどにはAIの文言を入れた方がウケがいいのかもしれない。

そんなCelestial AI、Hot Interconnectsではダイアモンド・スポンサーになったうえ、15分のスポンサー枠でRavi Mahatme氏(Senior Director of Product Management)が概略を説明するにとどまったが、Hot ChipsではPhilip Winterbottom氏(CTO)が"Celestial AI Photonic Fabric Module - The world’s first SoC with in-die Optical IO"と題した30分の講演を行なっている。そこで、両方の講演の内容をもとに説明していく。

LightmatterのPassageに近い構造だが

Celestial AIのPFLinkはCoWoSがベース

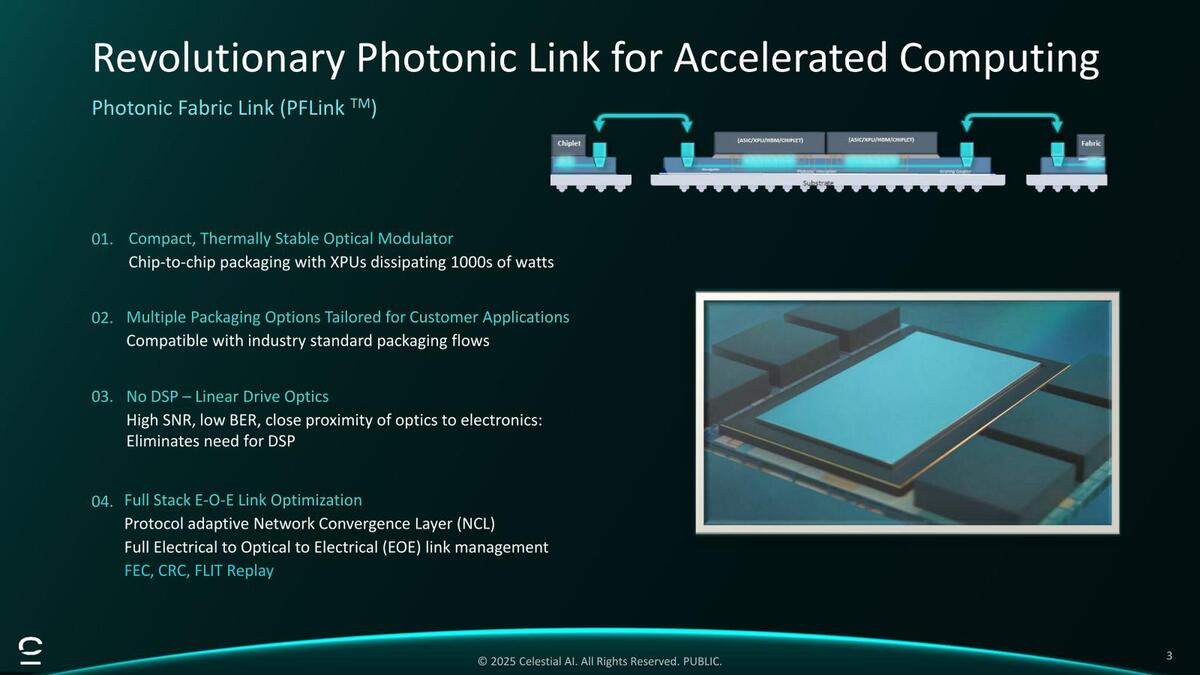

Celestial AIのターゲットは下の画像に示すように、Photonic Fabricの構築である。具体的にはチップ間接続とダイ間接続の両方をOpticalで行なうことを想定している。ちなみにこれはPFLinkという名称になっている。

beachfront(チップの周辺部)ではなく、ダイの中央からOpticalを出せる「唯一の」ソリューションとしているが、LightmatterのPassageがまさしくダイの中央からOpticalを出せるので、すでに唯一ではなくなっている

ここで消費電力数千WクラスのXPUと組み合わせても安定動作するというのはなかなか勇ましい数字ではあるが、これは後でモジュラーのところでもう一度触れる。またNo DSPがあるが、これも後述する。

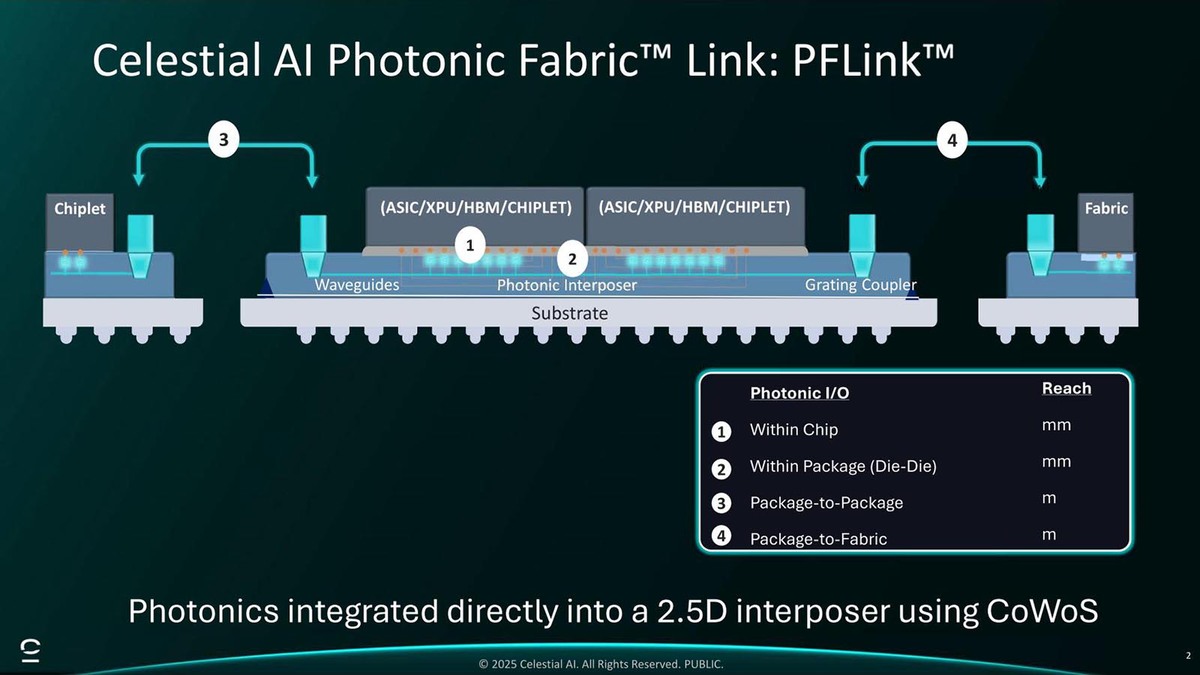

断面図をもう少し大きく示したのが下の画像である。TSMCのCoWoSをベースに、そのCoWoSの中にPICを組み込んで光信号の送受信を可能にする、という仕組みだ。なんというか、ものすごくLightmatterのPassageに近い構造であるが、これをCoWoSをベースにしているという点が大きく異なる。

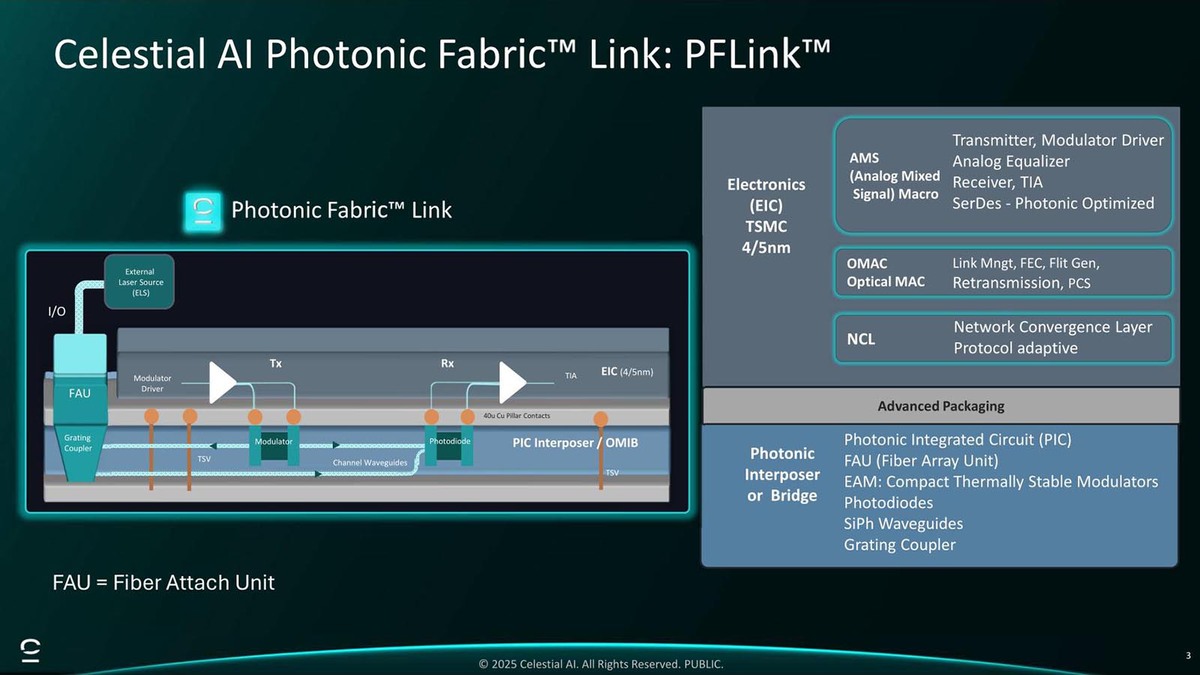

そのCoWoSをベースにした部分の、さらに拡大図が下の画像だ。インターポーザーの中にモジュラー/フォトダイオードを埋め込む形だ。またそのインターポーザー内に導光路も構築し、これを利用してダイ間の接続あるいはチップ間接続などを構築する形となる。

ただしインターポーザー内に埋め込むのはモジュラーとフォトダイオード、導光路とグレーチング・カプラー(FAUを接続するためのコネクター構造)などに限られるので、EICに関してはそのインターポーザーの上に載るダイの側に集積する構造を取ることになる。

ターゲットはTSMCの4/5nmということだが、これはとりあえずで、今後は3/2nmや逆に7/6nmへ対応を増やしていくことになるかと思われる。3/2nmはXPU本体向けに、7/6nmはI/Oチップレット向けにそれぞれ使われるようになるだろう。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります