第840回

Avicena Techが最新MicroLED光チップレット技術を公開! 2027年製品化に向けた新たな光インターコネクト戦略

2025年09月08日 12時00分更新

2027年中に製品化、2030年までに光インターコネクトを可能にする

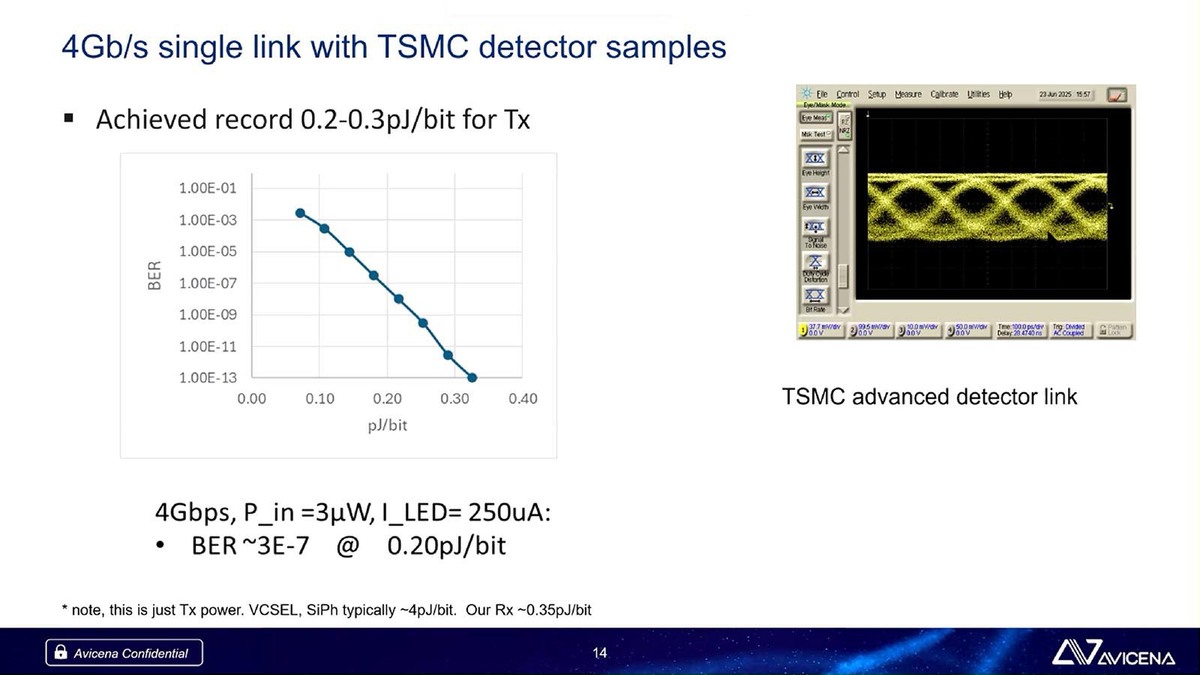

では受信側は?ということで、4GbpsでのリンクをTSMCの16nmプロセスで製造したDetector(受光器)で構成した場合の受信側の特性が下の画像だ。

さすがにEye Patternは3つ上の画像と比べてもバラつきが大きくなってはいるが、PAM4変調ではともかくNRZであれば十分なEye Heightがとれている

BERは受信光の強度というか、Detectorに利用する電力で変わってくるが、0.2pJ/bitのあたりで3E-7程度のBERを確保できている。実際にはこれだと積極的なエラー訂正を追加する必要があるので、もう少し電力を増やして0.25pJ/bitあたりにするのが現実的だろう(この場合、BERはほぼ1E-10程度まで改善される)。

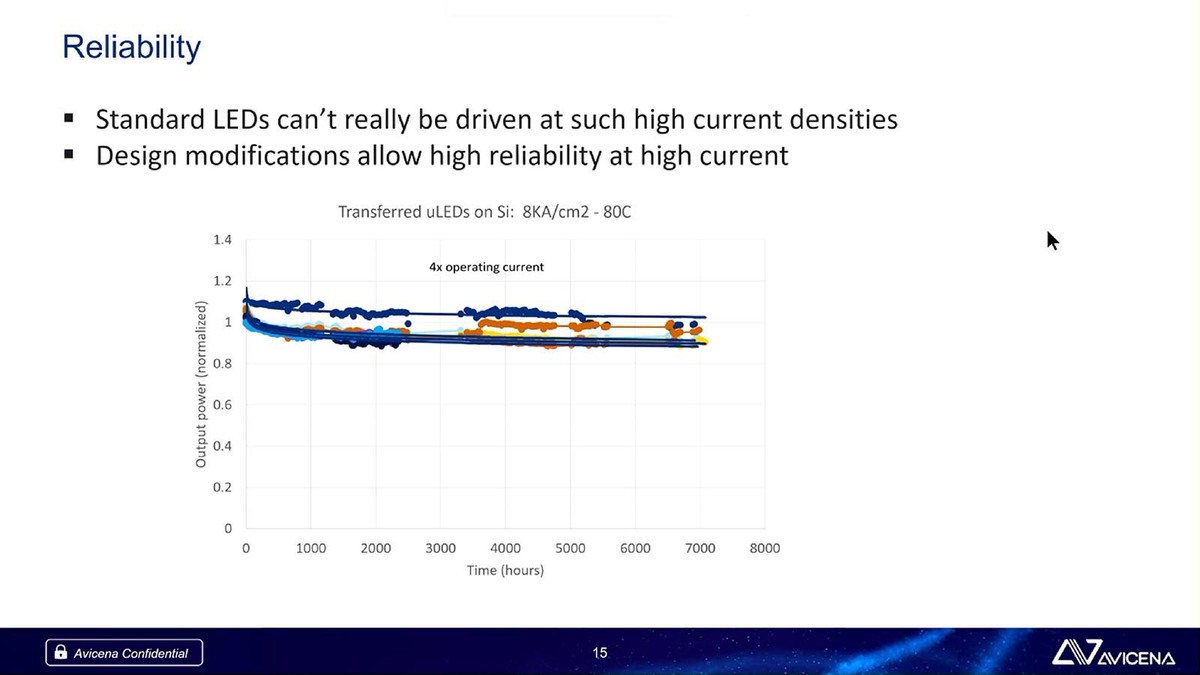

気になるのは信頼性だが、電流を8KA/cm2・80度の環境で7000時間あまり稼働させた状態でもほとんど光出力に問題ない、とされている。

少なくとも評価に利用するには十分な耐久性はとりあえずある。ただここにもあるように通常のMicroLEDの構造そのものでは、ここまでの耐久性がないので、なにかしら変更を加えたようだ。

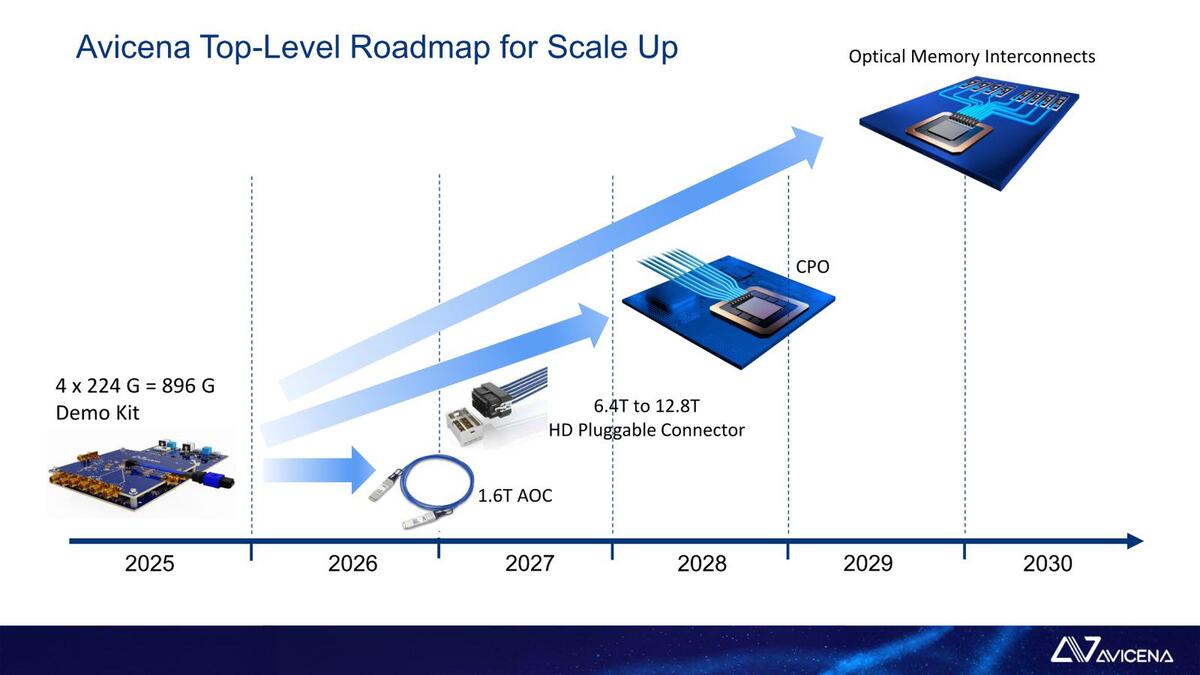

さて現在はデモキットが用意されているだけであるが、2026年末にはAOC(Active Optical Cable)向け、次いで2027年中にPluggable Connectorの形で製品化し、2028年にはCPO、2030年までにOptical Memory Interconnectを可能にする、というロードマップが示されている。

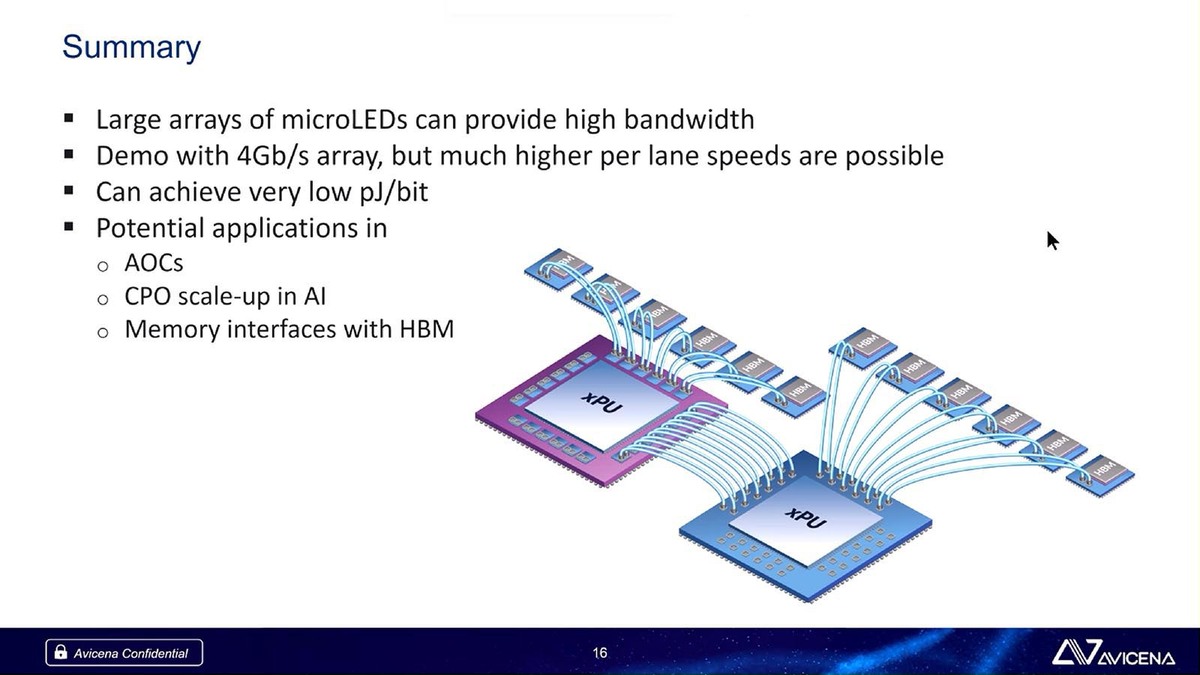

そのOptical Memory Interconnectとはなにか? というのが下の画像。現実的か? と問われると微妙(シリコン・インターポーザー経由でも同等の効率が実現可能で、しかもレイテンシーが少なそう)ではあるが、速度というよりもメモリー搭載量を増やしたいが、電気配線ではパッケージサイズや配線の取り回しの問題でこれ以上増やしきれないというケースには救いになりそうではある。

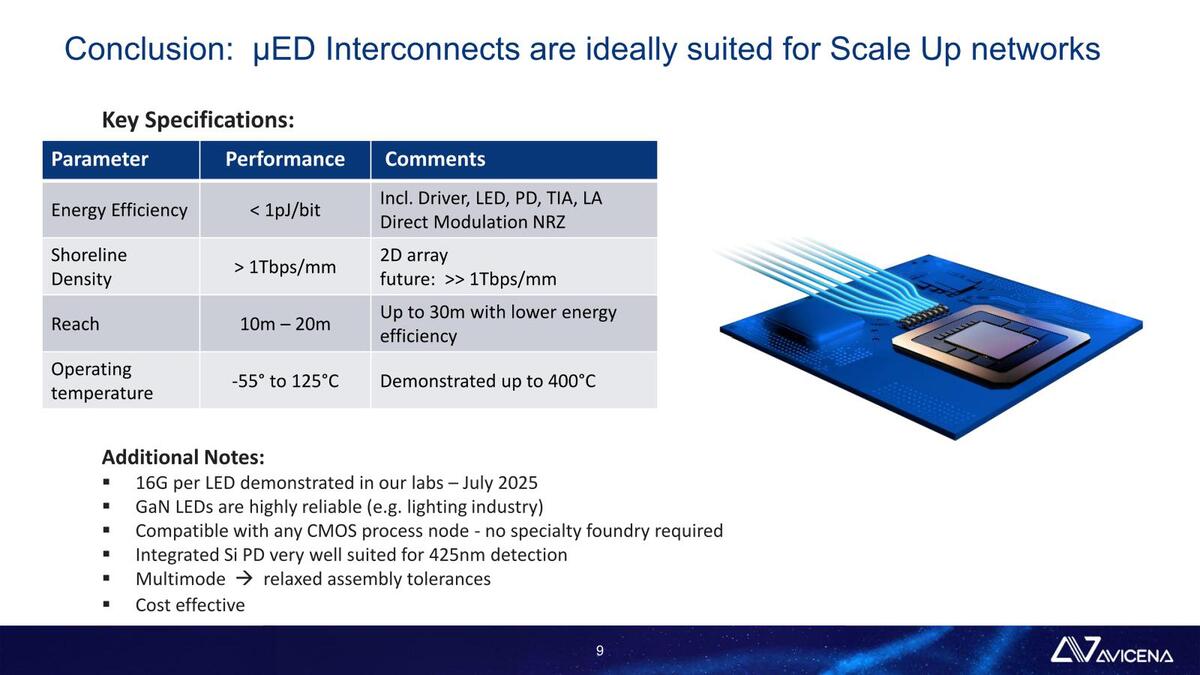

最終的なサマリーが下の画像だ。冒頭のページの画像にある要件を完全に満たしているとしており、これを利用してスケールアップ向けの光インターコネクトが実現できるというのが同社のメッセージである。

2つ上の画像のロードマップに従えば、2027年には実際にチップに組み込むためのソリューションが提供可能になる予定である。まずはそこまでに試してみたいという顧客を見つけることと、あとはそこまで会社が継続できることが現在の課題という感じであろう。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります