今回はLightmatter社のインターコネクトについてだ。Lightmatterは連載676回で光ベースのAIアクセラレーターであるEnviseを開発しているメーカーとして紹介しており、この際にそのEnviseを複数接続するためのバックプレーンとしてPassageの話も合わせて簡単に説明した。

Lightmatterのウェブサイトを見ると、製品はM1000とL200であり、Enviseは? というと(URLこそproductsページの下だが)Researchの下に移動している。そのEnvise用のプログラミング環境であるIDIOMも同様の扱いだ。

そんなLightmatterであるが、Hot InterconnectsではCEOであるNicholas Harris博士による基調講演とTaylor Groves博士(Principal Solution Architect)らによる"Accelerating Frontier MoE Training with 3D Integrated Optics"という発表に加え、Hot Chips 2025でも Darius Bunandar博士(Chief Scientist)による"Passage M1000: 3D photonic interposer for AI"という発表をしている。

Hot Interconnectsに関して言えば同社はダイヤモンド・スポンサーにもなっており、とにかくPassageをまず商品として売りたいという物すごく強い意志(というか、強い圧)を感じたのは同社のスポンサー筋の圧力? と思ったりするが、そういう事情はともかくとして3つも講演が行なわれたので、これをまとめてPassage M1000について説明したい。

プロセッサーではなくインターコネクトがボトルネックになる

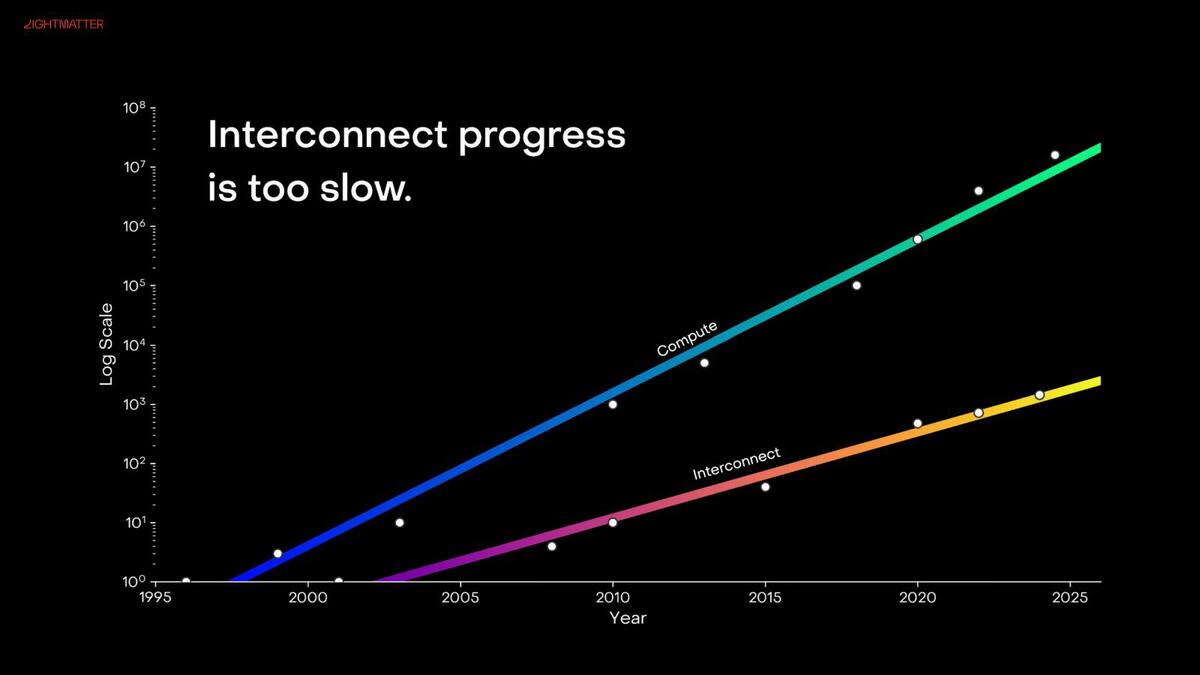

まずHarris CEOによる概略から。AIの進展にともない、計算能力は順調に増加しているが、インターコネクトがこれに追い付いていないとする。

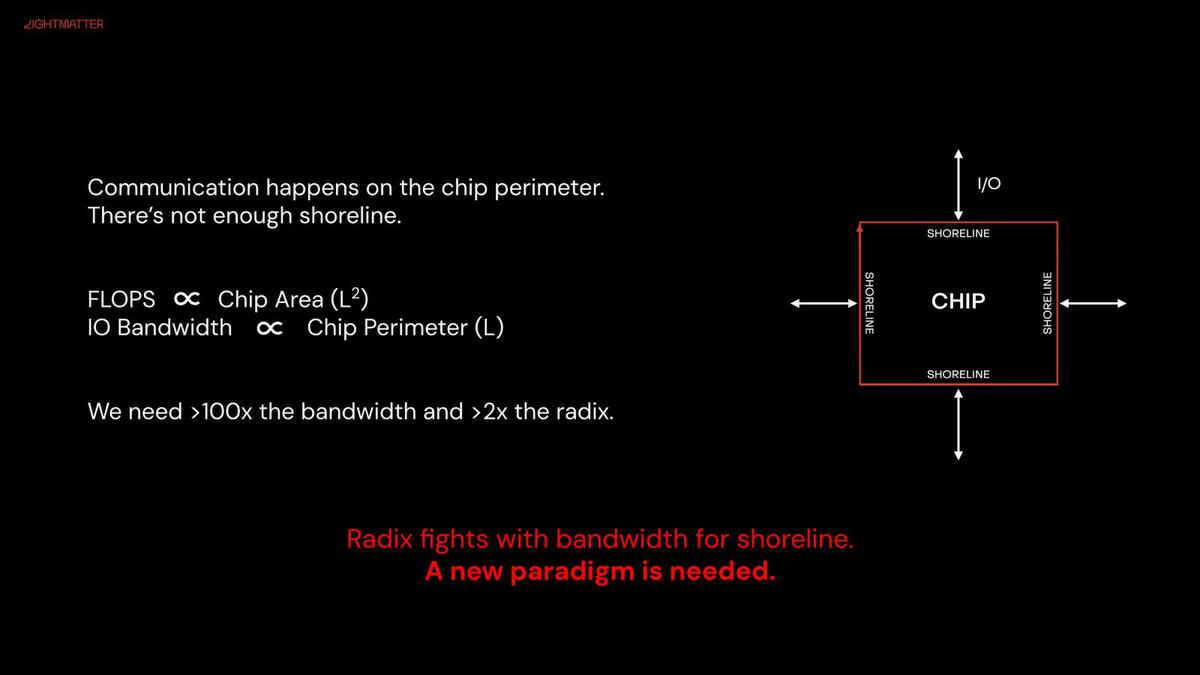

ただこれは構造的な問題でもある。構造的、というのは仮に光で通信しても、CPO的な実装だと帯域はやはりチップ周辺の長さに比例することに変わりはないからだ。

I/Oはチップの周辺に配されるから、I/Oの数はチップ周囲の長さに比例する。一方で計算能力はチップの面積に比例するから、どうやっても足りなくなる。ここでいうLはチップの長さ(縦でも横でもよいが)であり、現時点でも100倍くらいのギャップがある

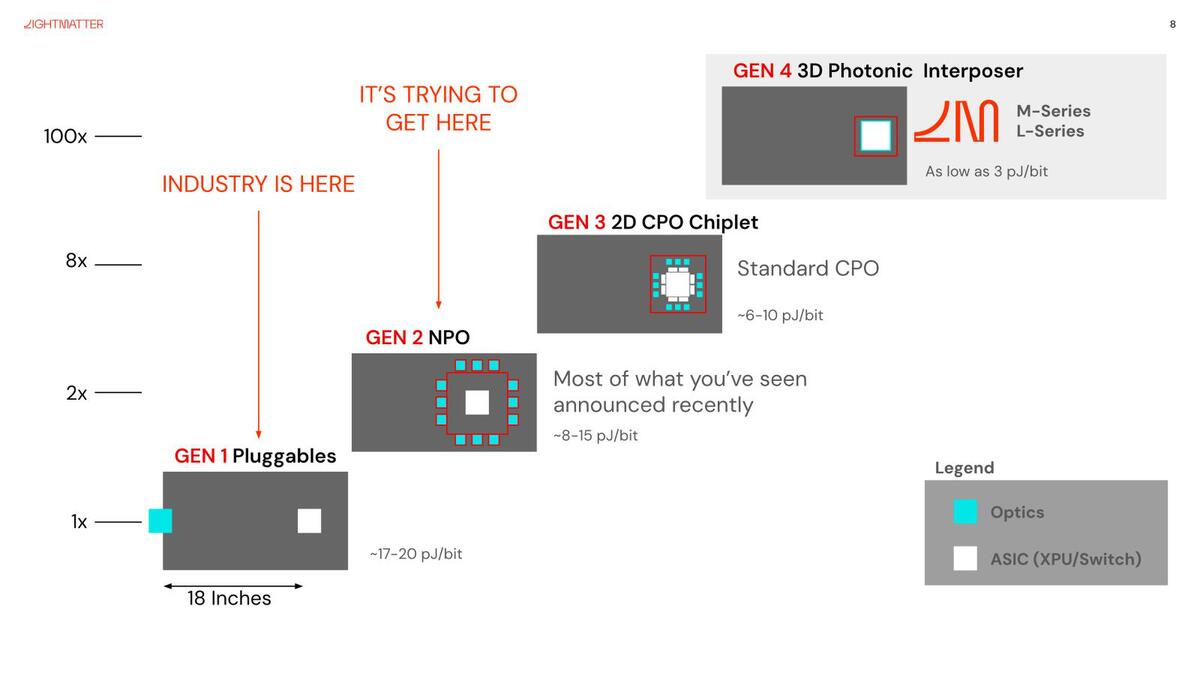

冒頭のグラフのとおり、インターコネクトの性能を100倍にできれば、ギャップはいくぶんなりとも小さくなる(この話は後述)。そのための方法がフォトニクスであるというのはLightmatterの生い立ちを考えれば明白なのだが、このための方法が4世代あり、同社はすでに第3・4世代のソリューションを用意しているというのが今回のメッセージである。

世代ごとに実装の方法が異なり、その性能差は消費電力の差という形で示されている。現在のデータセンターの課題は莫大な消費電力であり、通信に関しても「性能を落とさずに」消費電力を下げることが至上命題である。17~20pJ/bitから3pJ/bitまで下げられれば、その効果は非常に大きいわけだ。

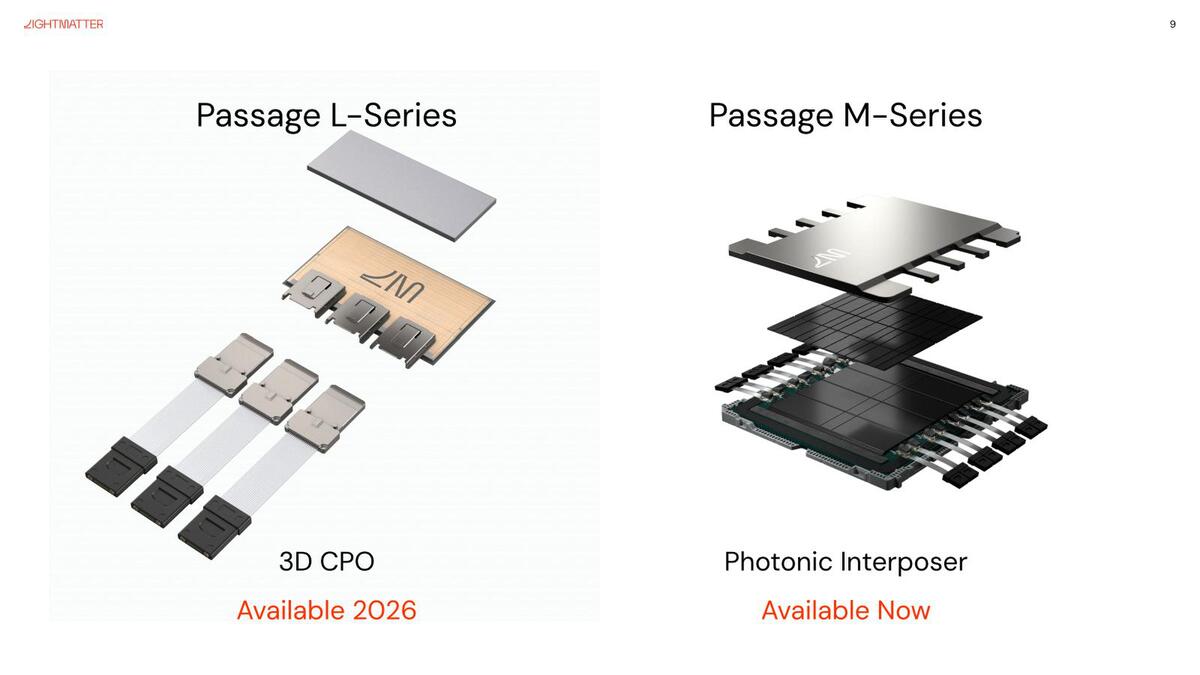

ではどのうようにそれを実現したのかだが、先に書いた第3世代がPassage L-Series、第4世代がPassage M-Seriesであり、今回はPassage M-Seriesとして最初に製品化されるPassage M-1000についての説明があった。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります