A14はNanosheet、A10はForksheetを採用か?

今回の発表はまだ研究段階のものではあるのだが、A14の次か、遅くてもその次くらいを見据えた、わりと現実的なものである。TSMCは2028年にA14プロセスの量産を開始予定となっているが、これはNanosheetないしScaled nanosheetの構成であり、Forksheetはその先だろう。

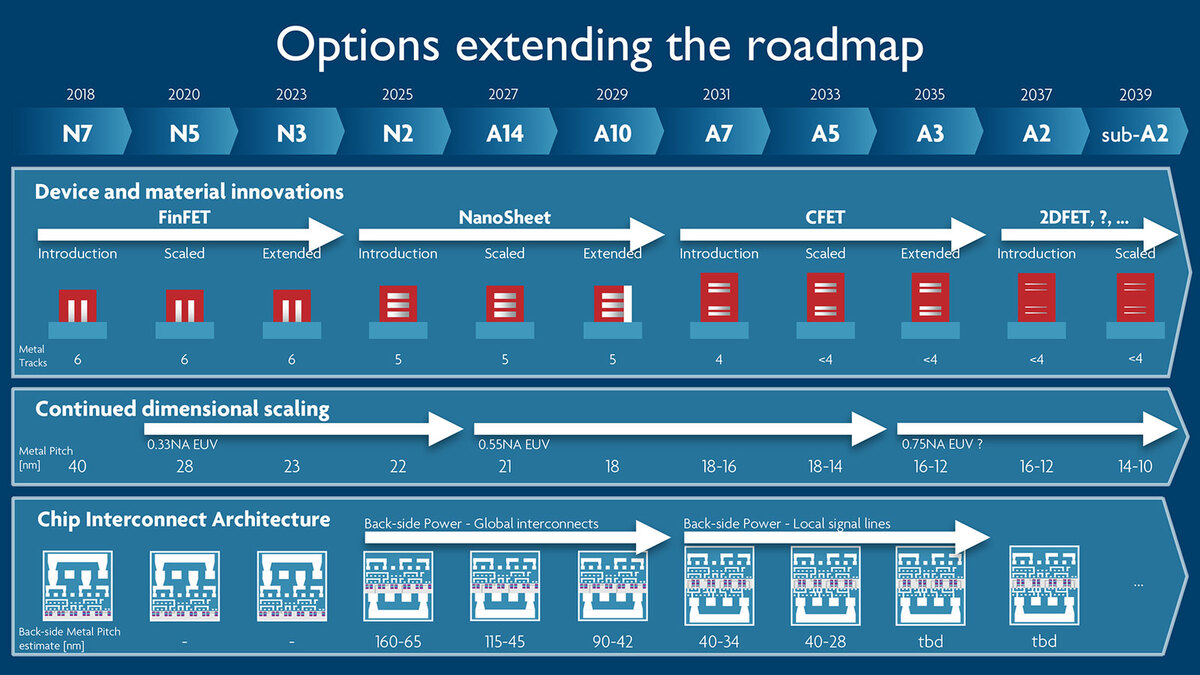

このロードマップ、2024年11月にimecが出した"Accelerating beyond-2nm innovation across the ecosystem"によれば、A14に続くA10までがGAAで、その先のA7がCFETになるとしている。A10がScaled Forksheetである可能性は低くないだろう。

冒頭でIBMがCFETに関する論文を発表した話に触れたが、そのIBMが提案しているのはCFETをForksheetベースで構築するというものである。

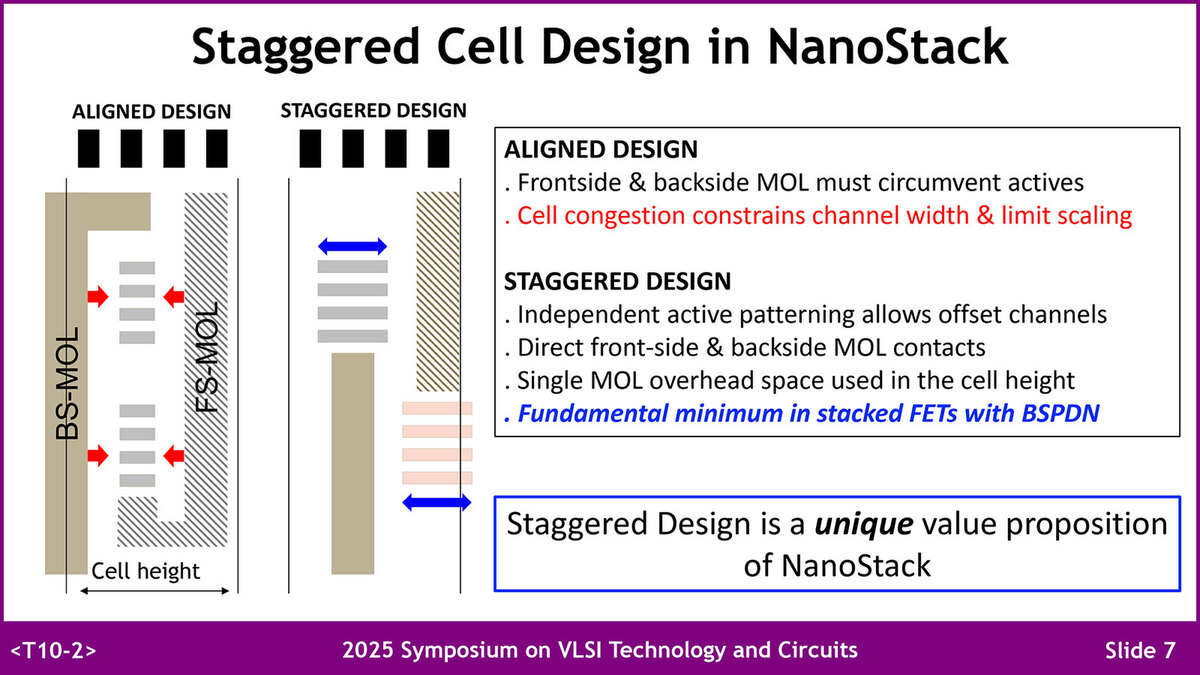

左のAligned DesignはNFETとPFETをそのまま積層するものだが、右のStaggered Designは言ってみればForksheetを構築後に、中間部で切って上下にずらしたような構造である。利点はBSPDNの構築が容易なことである

こちらもまだ研究段階のものだし、IBMはそもそも量産設備を持たない(この研究結果がRapidusの将来のプロセスに使われるかどうかも怪しい)ので、あくまでも研究レベルの話ではあるが、TSMC的には(IBMのようなことをするかどうかはともかく)Forksheetにそれなりの可能性を見出しているらしい。さて実際にはどうなるだろうか?

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります