連載833回でVLSIシンポジウムにおけるインテルの招待講演を取り上げた。こちらの内容は10年先のトランジスタの話であるが、同じくTSMCの招待講演がTFS(Technology Focus Session)で行なわれた。

TFS 2-1の"Assessment on Nanosheet Transistor Variants Beyond 2nm Node"というもので、内容的にはGAA(Gate All Around)とCFET(Complementary FET)の中間というか、CFETの基礎となる構造を論じたもので、IBMがやはり今回のVLSI シンポジウムで似た論文(T10-2 "NanoStack Transistor Architecture for CMOS 7A Node and Beyond")を出している。今回はこのTSMCの話を紹介しよう。

NanosheetはFinFETより幅を狭くしやすい

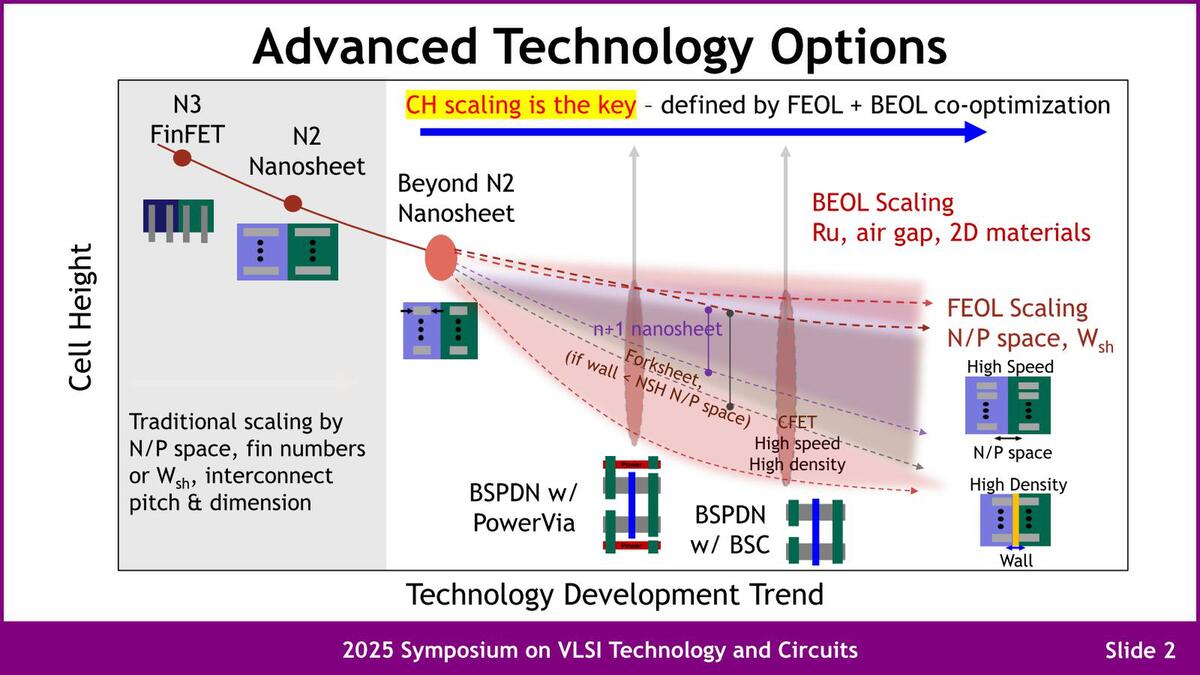

GAA(TSMCはNanosheetと称しているが、RibbonFETと同じもので、要するにシート状に積層するGAAの構造だ)の先にはCFETが待ち構えているわけではあるが、一足飛びにCFETに行くわけではなく、当面はNanosheetのまま微細化を進めることになる。

ここで微細化の鍵となるのがCH(Cell Height)であり、これをいかに微細化するかがNanosheet全体の微細化につながる。

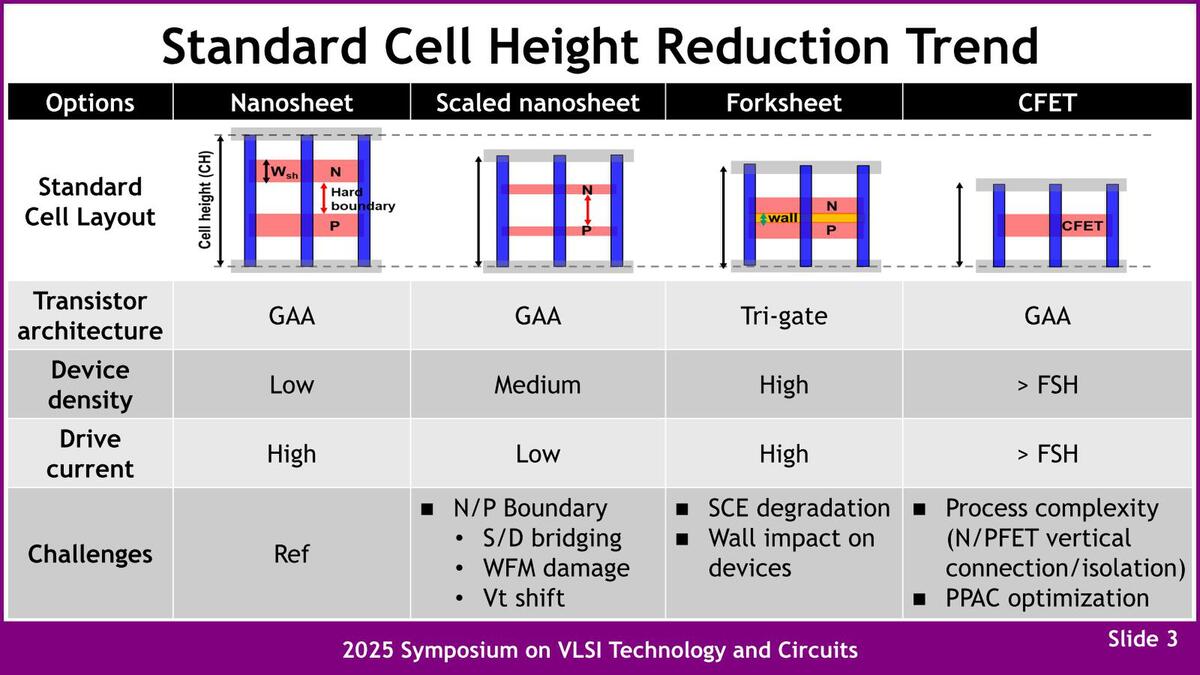

もう少し細かく見たGAAの今後の展開が下の画像だ。一番左が現在N2で実現されているプロセスである。次は、Sheetの幅を狭くし(Scaled nanosheet)、ついでNMOSとPMOSを完全にくっつける(ただし間に誘電壁:Wallを挟む)Forksheetを経て、最終的にはNMOSとPMOSを積み重ねるCFETに至る、というわけだ。

表の一番下はそれそれを実現するための前世代からの課題をまとめたものだ。ちなみにForksheetはGAAでなくTri-Gateに戻る。というのはこの世代では一部がGateの代わりにWallで入るので、構造的にはFinFETと同じく3方向をGateで囲う形になるからだ。

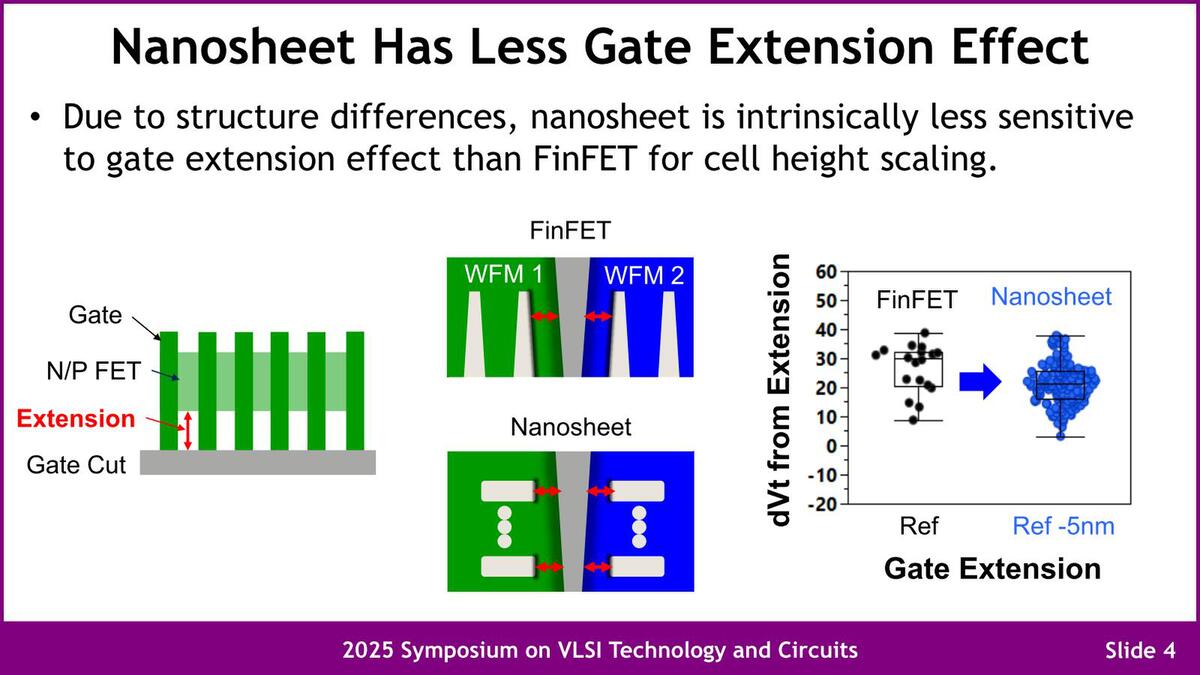

そんなNanosheetであるが、FinFETと比べた場合にGate Extension(下の画像の左および中央図で赤い矢印の部分)を縮小しても、動作電圧Vtのずれが少ないことがメリットとして挙げられる。

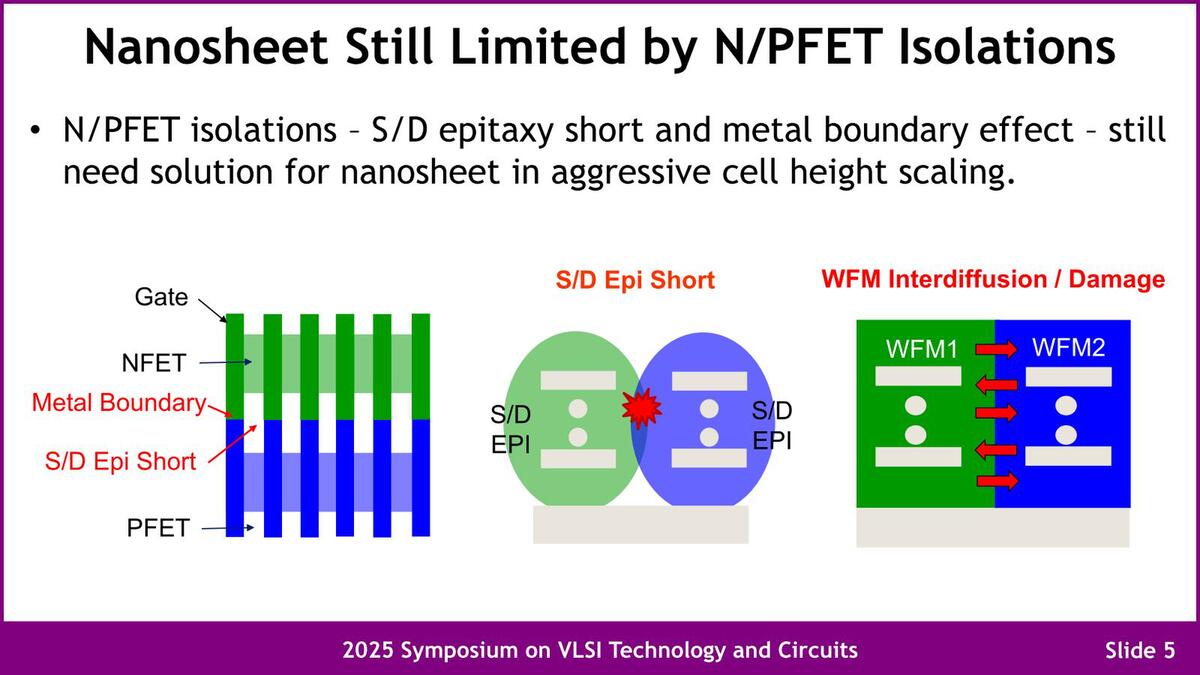

右のグラフは、FinFETと比較した場合にNanosheetは5nmほど距離を詰めても、Vtのずれが同程度であることを示している。その一方で当然問題もある。1つはSource/Drainの端子部が隣接することによる短絡(Short)、もう1つはWFM(Work Function Metal(仕事関数金属)の相互作用や破壊である。

前者は絶縁失敗ということだし、後者はPFETとNFETの動作がお互いに影響を受けてしまうし、仕事関数金属の破壊にもつながる。これをどうにかしないと、まともに利用できないことになる。

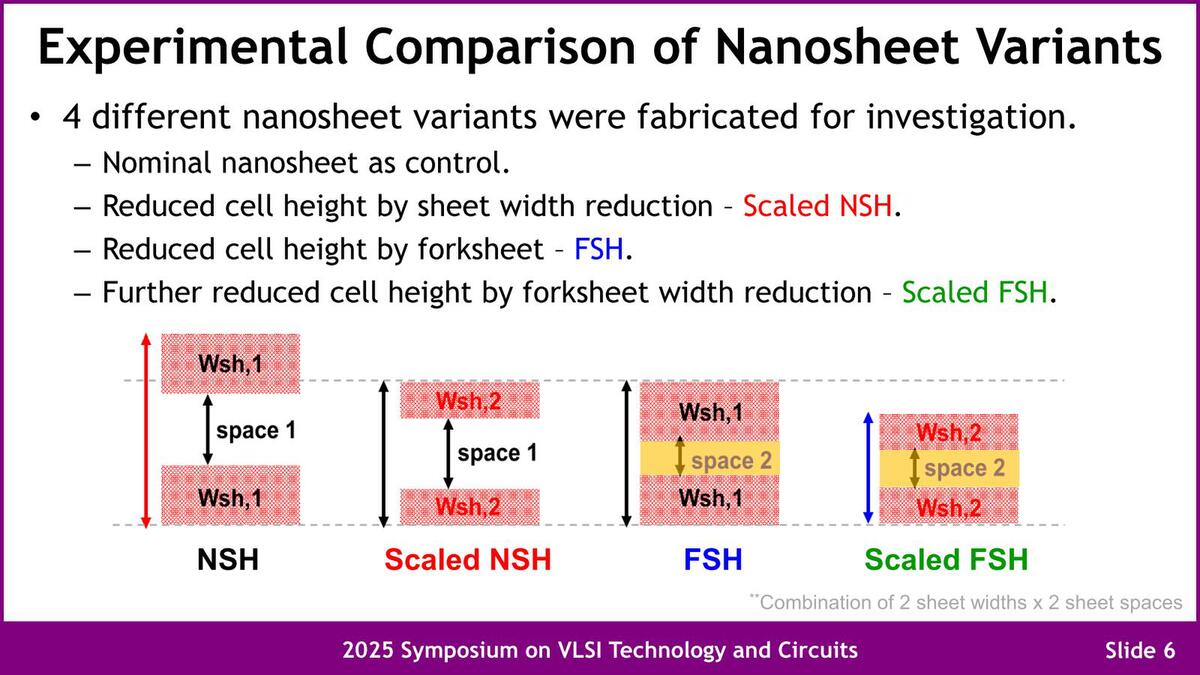

今回の論文は、ベースとなるN2(NSH:Nano SHeet)に対して幅を狭めたScaled NSHと、Forksheet構造(FSH)、幅を狭めたForksheet構造の4つを比較して特性がどう変わるかを調べたというものである。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります