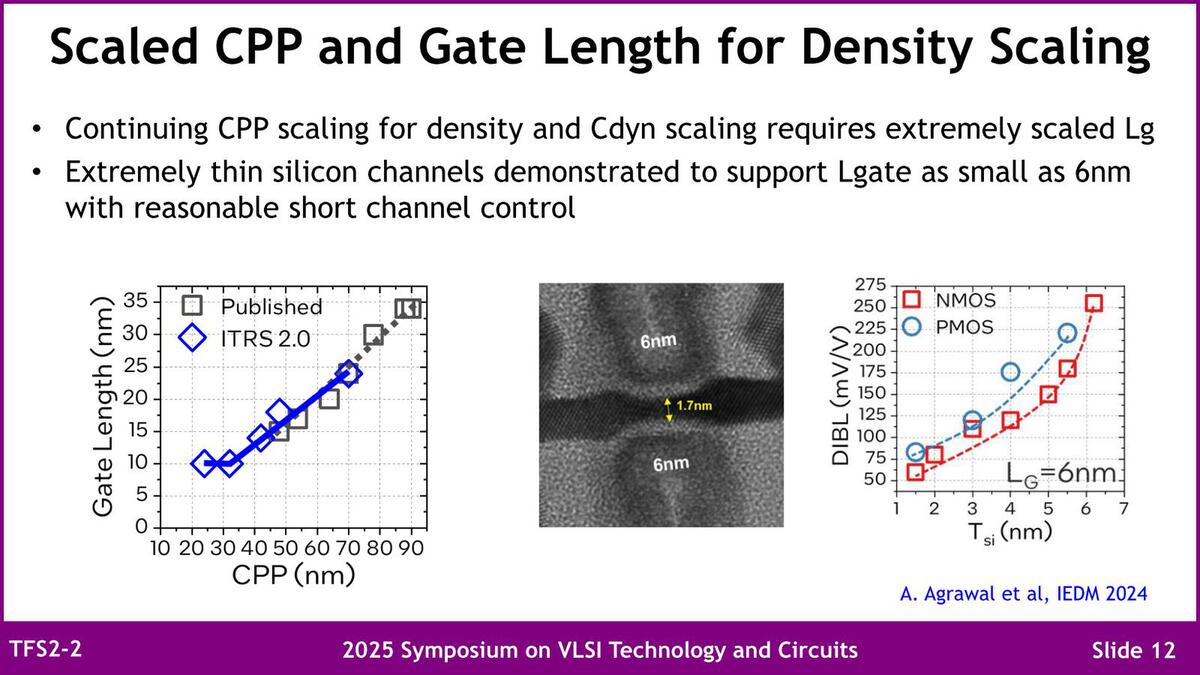

ゲート長を6nmまで縮めることで省電力化と小型化が可能

素材の話はおいておくとして、今後の展開としてCPPの縮小とCdynの低減のためには、さらにゲート長を縮める必要がある、としている。

この話も連載806回で説明したことの繰り返しになるが、ゲート長(Finの厚み)の限界は3nm程度で、実際問題としてNMOSでは4nmあたりまで薄くすると性能が飽和する上、4nm未満では急速に抵抗値が増える。PMOSは6nmで抵抗値が増えるということで、ゲート長6nmあたりが1つの目安となるという話だった。

今回のスライドもこれを受けたものになっており、今後は6ゲート長6nmを目指すとしており、その際にはCPPをさらに小さくすることが可能で、これはCdynの低減にもつながるというわけだ。

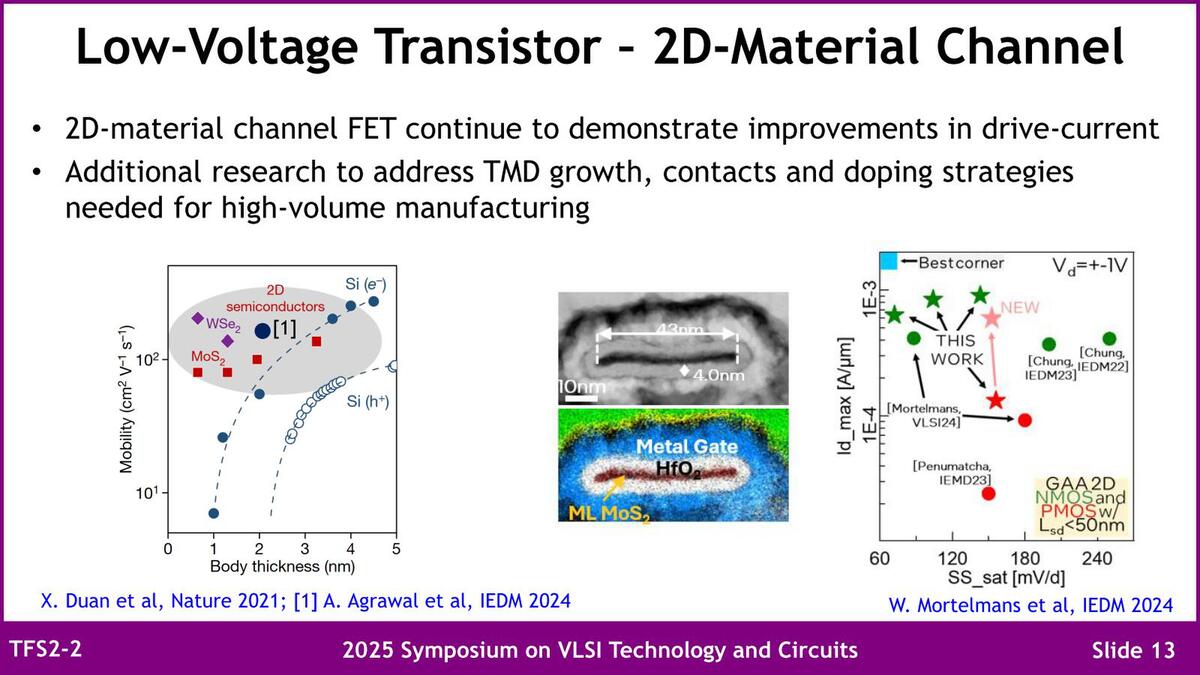

Ge以外でも、酸化ハフニウム(HfO2)でFinの外側を覆う構造はすでに連載808回で説明したとおりであり、これについても簡単に言及された。もっともここであまり新しい話はなく、また量産の手法を確立する必要がある、つまりまだ確立できていないとしている。

連載808回の最後でも触れたが、現状はまだ基礎研究のレベルで、量産に持ち込める状況にはなっていない

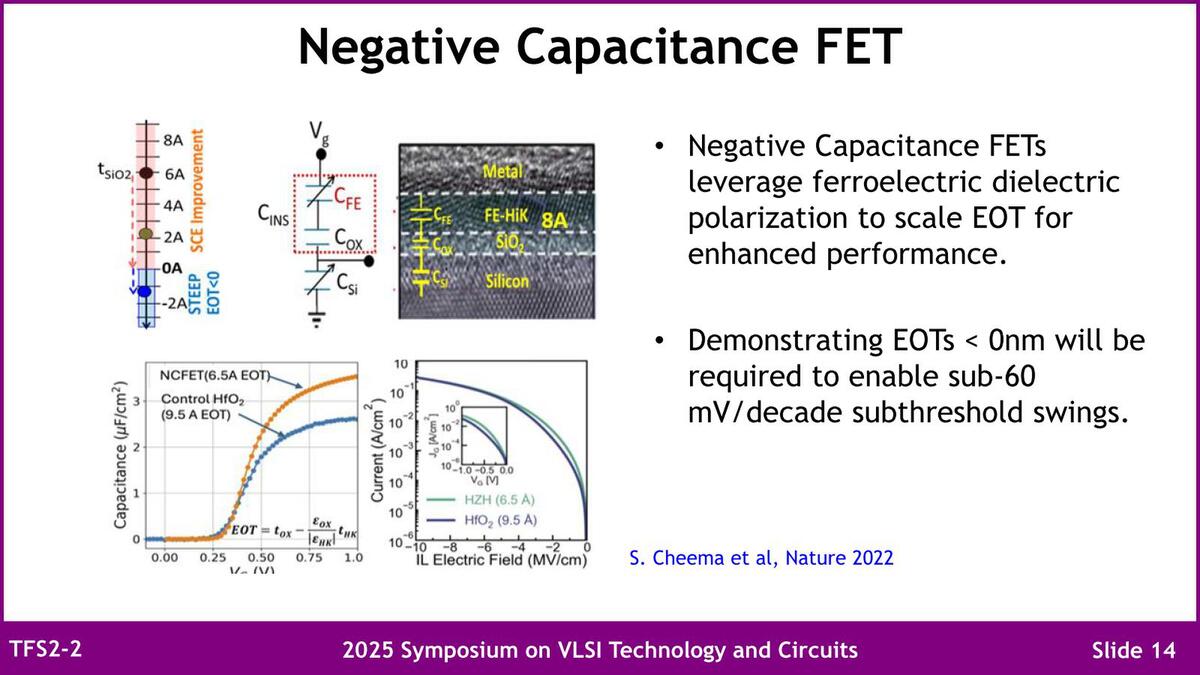

NC-FET、FEFET、MESOを研究開発中

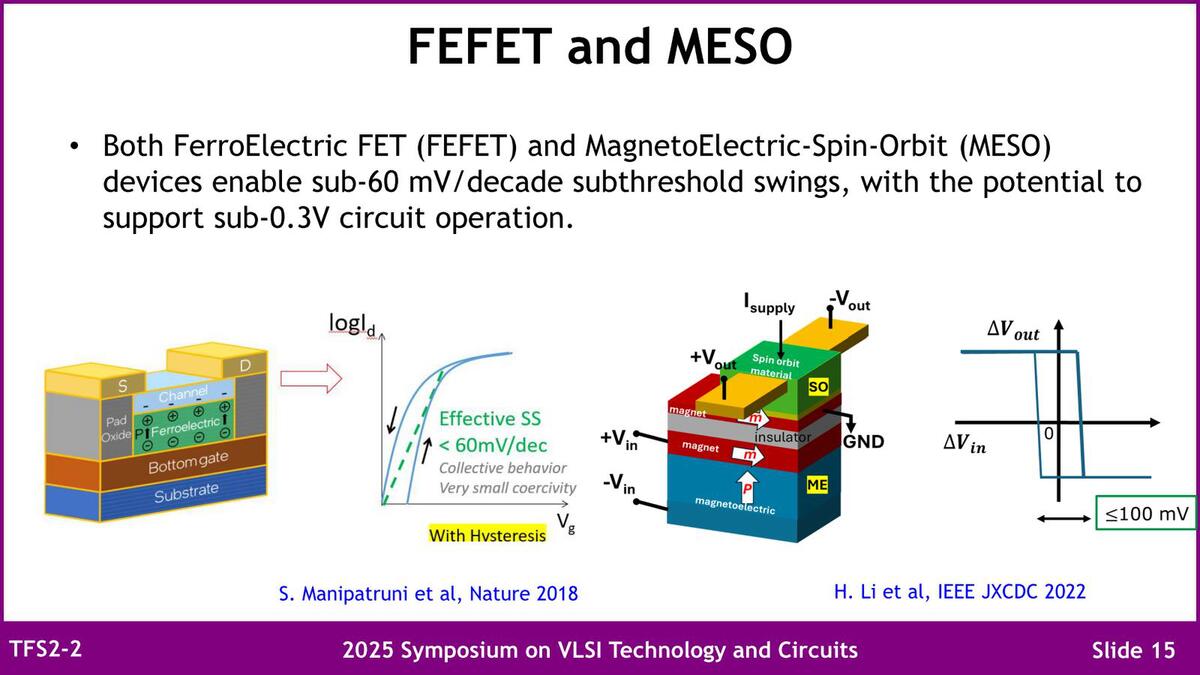

同様にNC-FET(Negative Capacitance FET)やFEFET(Ferroelectric FET)とMESOについても説明された。このうちNC-FETとFEFETについては、連載803回の最後でも触れている。

連載251回で紹介したが、トランジスタにはスレッショルド電圧と呼ばれるしきい値がある。ではそのスレッショルド電圧を下回ると一切電流が流れなくなるのか? というとそういうわけでもなく、実は電流はわずかに流れている。このしきい値以下の領域では、60mV/dedaceという理論限界がある。連載251回でも説明したが、要するにこの領域では電圧が60mV増えるごとに、流れる電流が10倍になるという意味である。

これを例えば50mV/decadeや40mV/decadeにできれば、それだけスレッショルド電圧が下げられる=より低電圧動作が可能になるので、構造や材料などを工夫してこの60mV/decadeの壁に挑戦しているわけで、NC-FETとFEFETはどちらもこれに向けた研究である。

MESOはやや毛色が違っており、磁気電気効果を利用してデバイス内部の磁化を変化させることでOn/Offを実現する仕組みだ。この変化は、スピン軌道結合成分によって電荷に変換されて出力されることになる。こちらが注目されているのは、トランジスタに比べて圧倒的に必要となるエネルギーが少なく、インテルによれば0.1Vで動作するトランジスタが可能になるとしている。

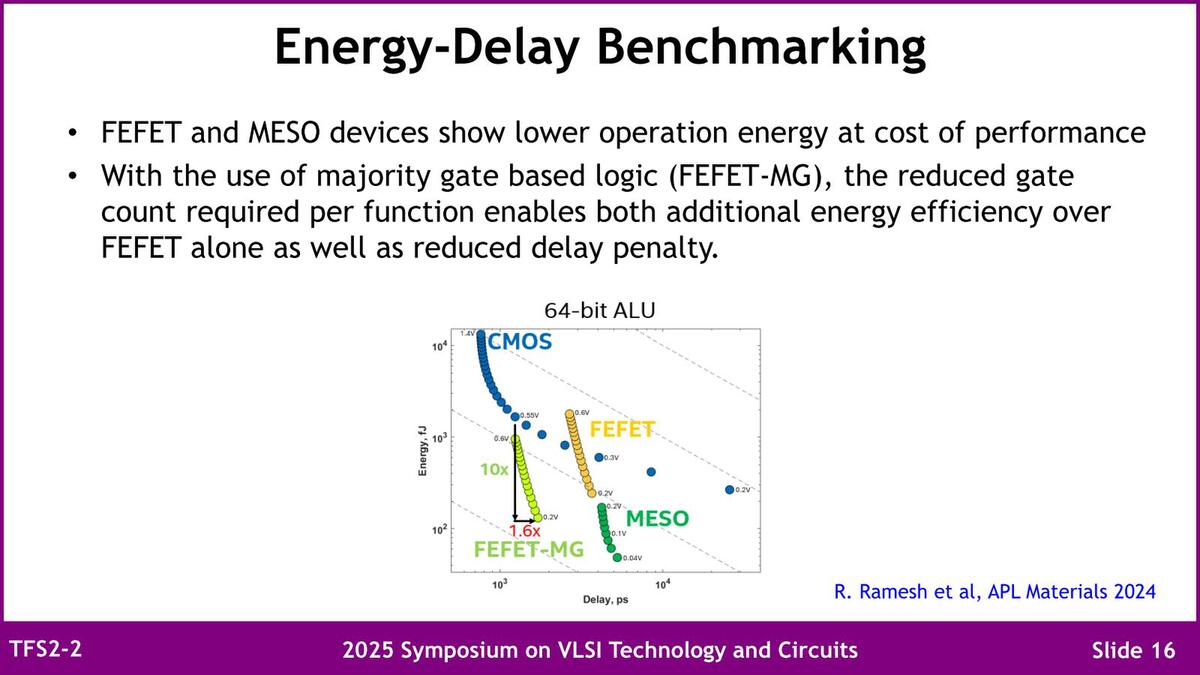

実際、FEFETとMESOで64bit ALUを実現するのに必要な電力をシミュレーションした結果が下の画像で、省電力や小型化にはかなり有利であるとしつつ、ただそれがいつ実現するかについての説明は一切なかった。

総じて言えば2024年のIEDMの発表とほとんど変わるところがなかったのが今回の発表である。もうGAAの世代に入りかかっており、その次のCFETに関してはある程度見えてきているものの、その次に関してはまだ模索中、という状況に変化はないわけだ。したがってインテルとしては、今後もFoundryビジネスに参入し続ける意思があるのであれば、ここに向けてさらに研究開発を進めていく必要があるわけだが、果たして今のインテルにその体力がまだ残されているのか、が次の疑問である。

インテルは現在5000人規模のリストラを本国で進めていると報道されており、ここにはオレゴンでプロセスの研究開発に関わる人員も含まれるらしい。少し心配である。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります