PMOSとNMOSを垂直に積層するCFET構造で

インテルはRibbonFETを積み重ねる

トランジスタの小型化の先にあるのが一体化である。CMOSを構成するのに、NMOSとPMOSの2種類のFETを組み合わせるという話は連載236回で説明したが、つまり1個のインバーターを構成するためには2つのFETをこれまでだと横に並べていた。連載831回のスライドでも、上下に2つのFETが並んでいるのがわかるだろう。

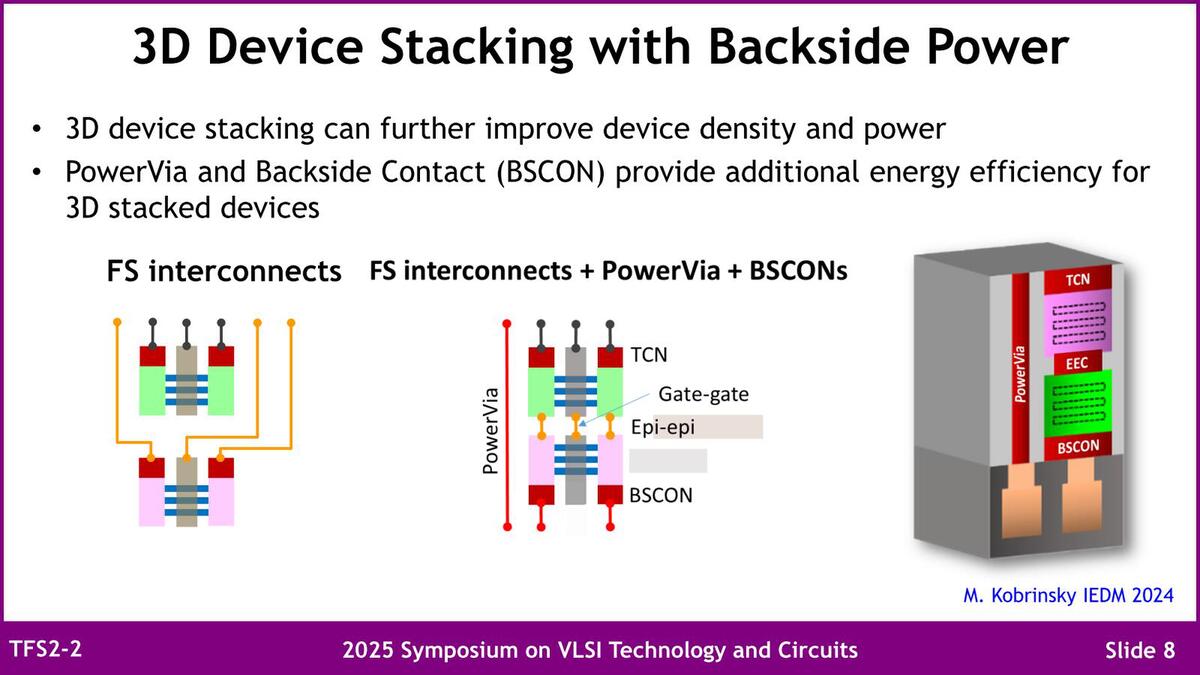

これはFETを上から見た構成だが、どうせNMOSとPMOSの2つのFETが連携して動くのであれば、これを3次元的に積んでしまえば面積が半分で済む、というのが次にくる進化と考えられている。

ただこの際に、下側のFETについては従来通りBSPDNとして基板の裏側から給電するとして、上に積む方はどうするのか? というのが問題になる。これについてインテルでは、PowerVIAの配線を基板の裏面からVIAで伸ばし、上側のトランジスタのさらに上まで延長して接続する形になる。この結果、FETの上にはTCN(Top CoNtact)、下にはBSCON(BackSide CONtact)がそれぞれつながり、FETの出力は2つの間("Epi-epi"とある部分)から取り出すという、なかなかに複雑な構造となる。一番右がこの模式図である。

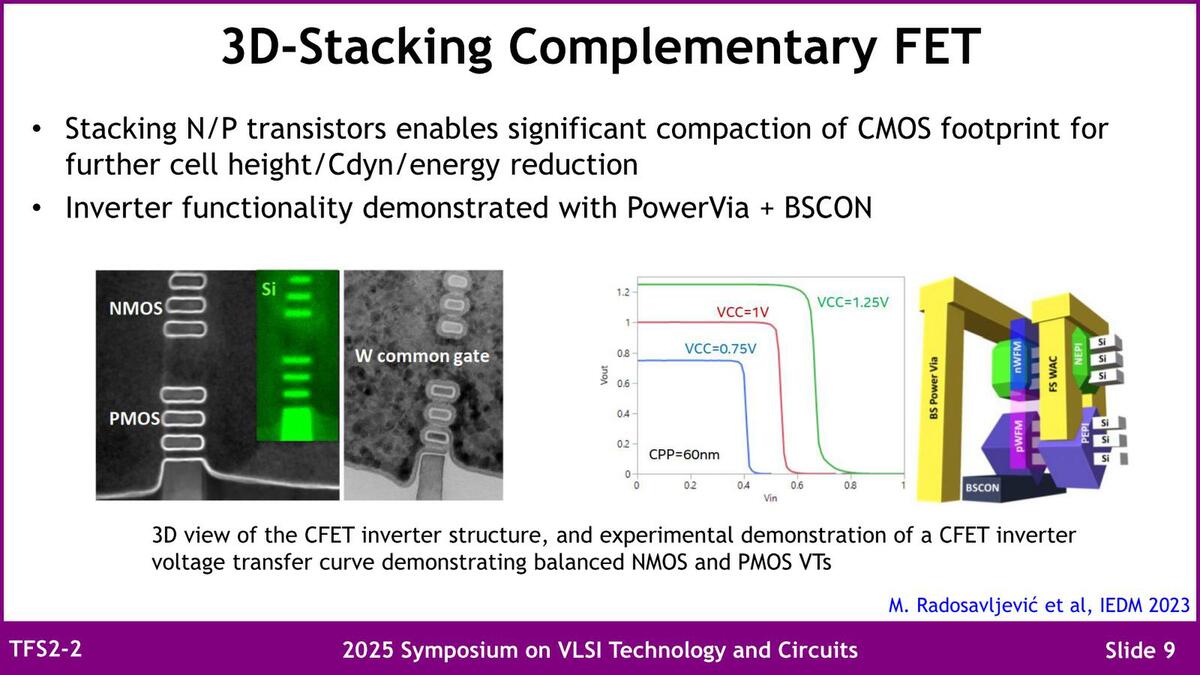

この構造を俗にCFET(Complementary FET)と呼び、昔から議論はされていた。ただ以前はRibbonFETを組み合わせる構造ではなかった。例えば2017年のARM Techconのレポートの中でCFETが示されたスライドを見るとだいぶ構造が違うのだが、IEDM 2024レポートのスライドでは、RibbonFETを積み重ねる構造が初めて示された。この構造の詳細が下の画像である。

単純に積み重ねると2倍の密度になりそうなものだが、実際はPoweVIAの配線などが新たに付け加わった結果として、密度は1.5倍ほどになるとする。それでも密度50%増しというのは大きな進化なのであるが。

ちなみにこの世代はまだRibbonがSiベースで構築される形になっており、それでもきちんと性能が出ることは示されている。グラフを見る限り、Vccを0.75Vまで下げると0.4V程度のしきい値で動作することが確認されている。

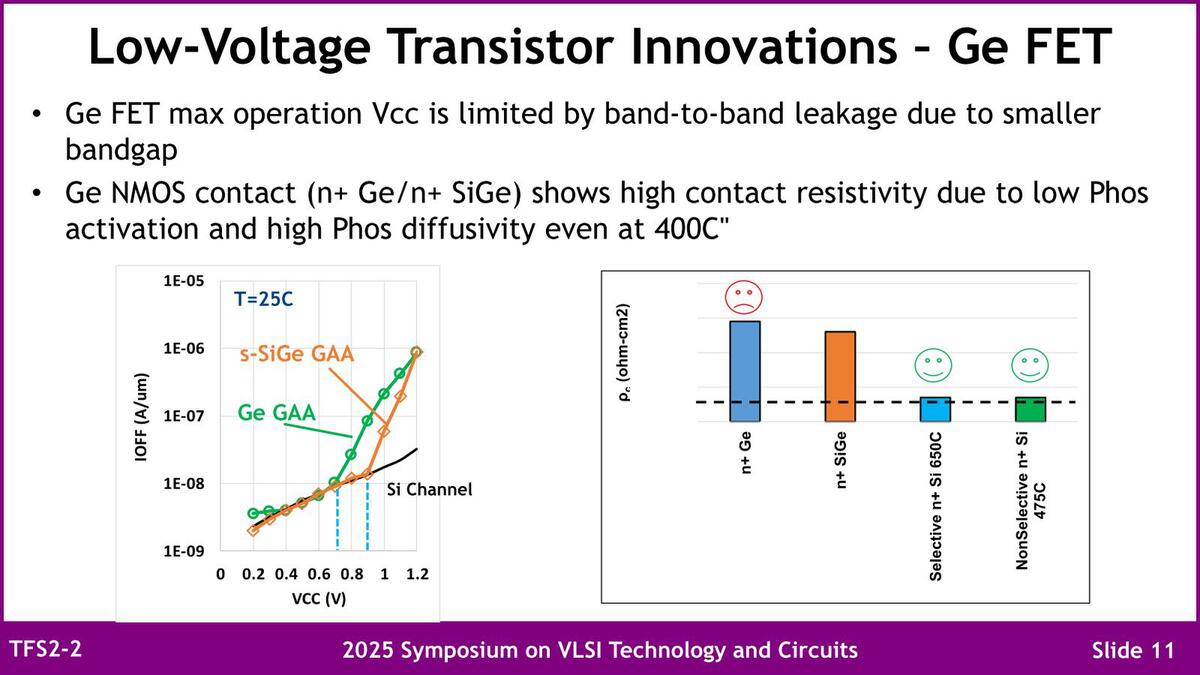

ただ連載803回でも触れたように、電圧を下げるとそれだけ性能が遅くなる。連載803回ではSteep Slope Transistorの可能性についての言及があったが、今回はGe FETを全面に押し出している。

このGeの優位性についてはIEDMでも触れられていたが、今回もこれを繰り返した格好だ。IEDMの方にも記載があるが、Geを利用したNanoRibbonは、CV特性が非常に優れており、これを利用してRibbonFETを製造すればPMOSの側はかなり優れた特性を持つものと期待できる。

もっともPMOSだけあっても仕方がないわけで、NMOSの方も同程度の改善がないといけないのだが、それについては言及がないあたりは懸念事項である。あと連載803回でも指摘したが、Si基板の上にGeを構築した場合、まだかなり欠陥が多い。実際にはHigh-K材料でGeのRibbon(上のスライドだとNanoRibbon)を覆う形になっているが、これの構築がどの程度量産レベルで可能か、はまだ未知数ではある。

ちなみにこのGe FET、電圧を上げると急速に特性が劣化する。NMOSはコンタクト部分が高抵抗になることも問題として挙げられており、このあたりをどう改善するかも1つの課題となっているとする。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります