第832回

Intel 18AでSRAMは進化したか? Synopsysが挑む最適化技術とWrite Assistの新アプローチ

2025年07月14日 12時00分更新

VLSIシンポジウムで、インテルは大量のIntel 18A絡みの発表を行なった。1つ目が前回説明したT1-1 "Intel 18A Platform Technology Featuring RibbonFET (GAA) and PowerVia for Advanced High-Performance Computing"であるが、他にも4件の論文が出されている。

それぞれSRAM、PAM-4ベースのSerDes、eFuse(一度のみ書き込み可能なメモリー)、温度センサーに関するもので、実際にIntel 18Aを使ってASICなどを作ろうとした場合には欠かせないコンポーネントばかりである。別にこれだけあれば大丈夫というわけではない(他にもいろいろ必要なものはある)が、こうしたものを積極的にアピールすることで、ユーザーを増やしたかったというインテル・ファウンダリーの意図が透けて見える感じは否めない。

それにもかかわらず前回の最後で書いたように、Intel 18Aの外部顧客獲得を諦めたといった話が出てきているのは少し皮肉ではあるが、まだインテルの公式発表ではない。インテルは7月24日に第2四半期の決算発表をすると予告しており、ここでなんらかの発表があるのではないか、と思われる。

Intel 18AはSynopsysの高密度SRAMセルを採用する

今回はこの4つの中から、C4-4 "A 37.8Mb/mm2 SRAM in Intel 18A Technology Featuring a Resistive Supply-Line Write Scheme and Write-Assist with Parallel Boost Injection"の内容を解説していこう。おもしろいのはこの発表、インテルではなくSynopsysによるものである。

Synopsysは当然ながら主要なファウンダリー上で利用できるFoundation IP(基本的なIP)を提供しており、ここにはSRAMも含まれる。つまりSynopsysのEDAツールを使ってIntel 18A上でASICを作ろう、という顧客に対してSynopsysから提供されるSRAMコンパイラで構築されるSRAMの構造を紹介するものとなる。

前回の表ではIntel 18AのSRAM密度はHCCで29.035Mbit/mm2、HDCで31.8Mbit/mm2と紹介したが、Synopsysはこれを37.8Mbit/mm2まで高めており、TSMC N2の38.1Mbit/mm2に迫るものとなっている。

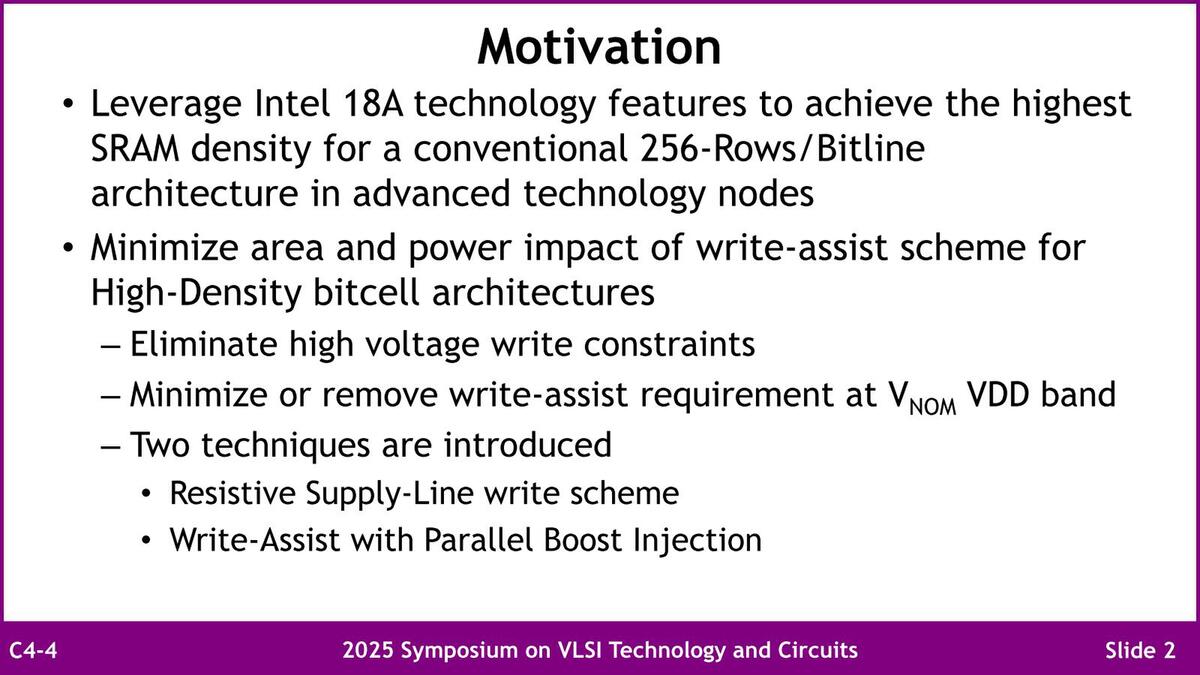

そんなSynopsysのSRAMであるが、目的は高密度SRAMセルを構築することであり、このためにインテルと同様にNBL(Negative Bit Line)を含むWrite assistのメカニズムを実装したとする。

Write assistを実装。高密度にするだけなら、例えばBitlineあたりのRow数を増やせば、それだけBit線の数を減らして密度を上げられるが、これは不都合なことが多い。あくまでも256-Row/Bitlineのまま、SRAMの構成を工夫して密度を上げたとしている

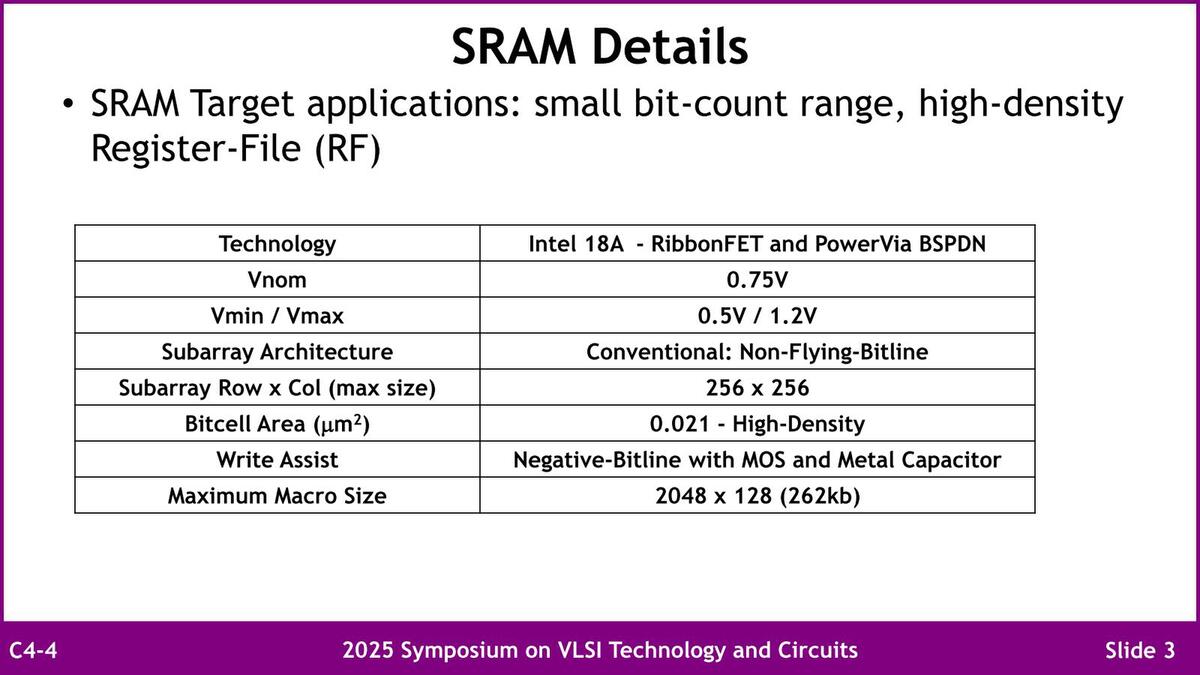

具体的なパラメーターが下の画像となっている。このBit cell Areaの0.021μm2というのは、Intel 18AのHDCと同じである。ただSRAMの密度そのものに差があるのは、実際には間に配線が挟まるからで、その配線をどう設けるか(あるいはNBLのWrite Assist周りをどう構成するか)といった、SRAMセル以外の部分の面積に差があり、これがSRAM Macro Cellを構築した際の密度の差につながる形になる。

逆に言えばSRAMセルそのものの面積は、同じトランジスタを使って同じFlipFlopを構成している限り違いは出ないわけで、そこで違いが出るというのは、例えば速度や信頼性を犠牲にしてFlipFlopの構成そのものを変えたり、あるいは入出力の同時アクセスを制限する/拡張したりしないと差は生まれない。

今回の場合、インテルもSynopsysも6T SRAMの構成で、ここに差はみられない。高密度向けなのでトランジスタの構成もそれに合わせて高速型ではなく高密度/低消費電力型となっているからだ。

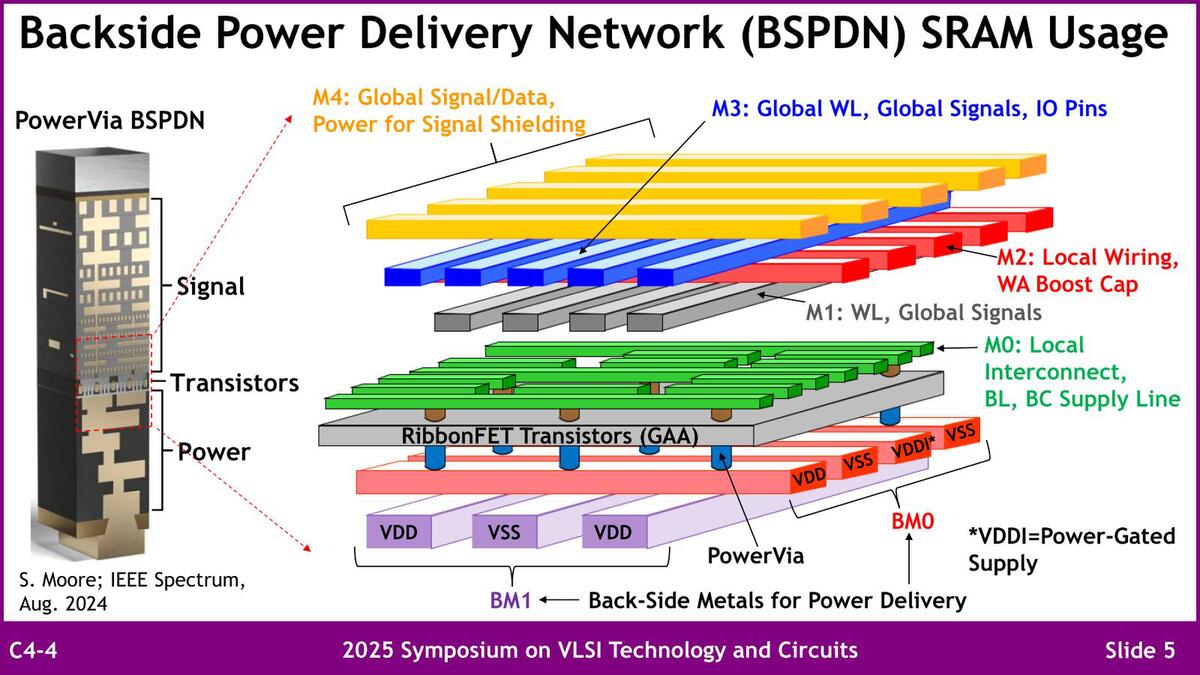

SRAMでなく一般的なロジック回路の場合もほぼ共通だが、M0がBit Line、M1がWord Lineに割り当てられていることに注目。またWrite Assist Boost用のキャパシタにM2を使うそうだ

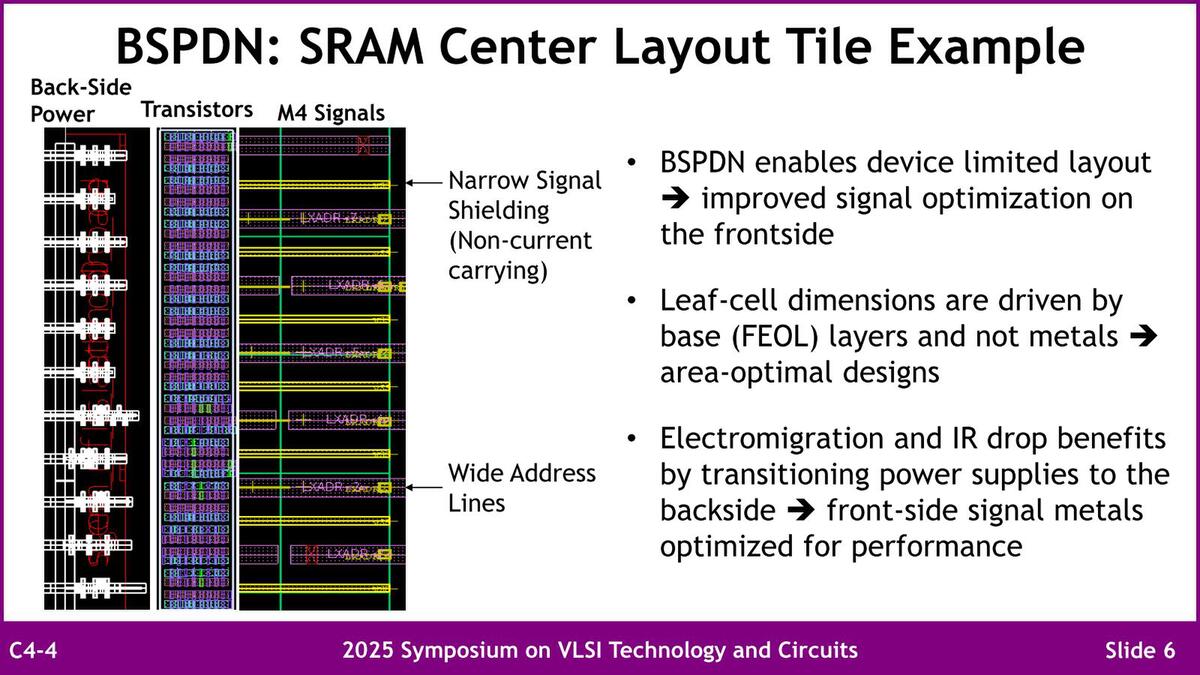

その配線であるが、下の画像がIntel 18AにおけるSRAMに関係しそうな配線層(とトランジスタ層)一覧である。ここでIntel 18Aで採用されたPowerVIA、つまりBSPDNのお陰で、これまでよりもレイアウトに自由度が増えたとする。

エレクトロマイグレーションは、金属配線を流れる電流によって金属原子が移動する現象のことで、配線が断線したりショートしたりする可能性がある。この画像は、電力供給が裏面になるので配線の寸法をずっと太くでき、エレクトロマイグレーションの影響を受けにくくなるという話である

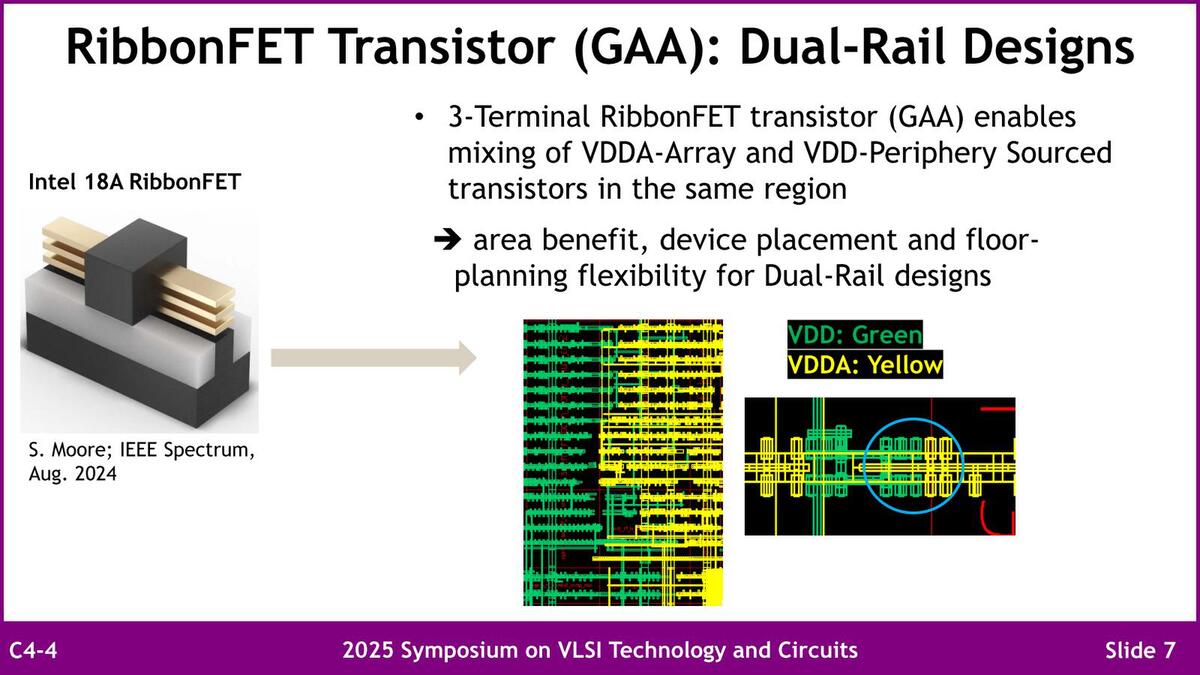

具体的には配線層から電源ラインが消えたので、配線の最適化の度合いを上げられたこと、SRAMのセルはトランジスタ層だけで決定でき、配線層の影響を受けないので設計が用意になること、それとBSPDNの利用でエレクトロマイグレーションやIRドロップ(電圧降下)の影響を受けにくく、性能を上げやすいことをメリットとして挙げた。またRibbonFETについても、コア部と周辺回路部を同じ領域に設置できるので、それだけエリアサイズを詰められるのもメリットとしている。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります