第823回

Intel 18AはIntel 3と比較して性能/消費電力比が15%向上 インテル CPUロードマップ

2025年05月12日 12時00分更新

主要なプロセスに関する現状を説明

複雑なチップレットを構築できることを実機で証明する

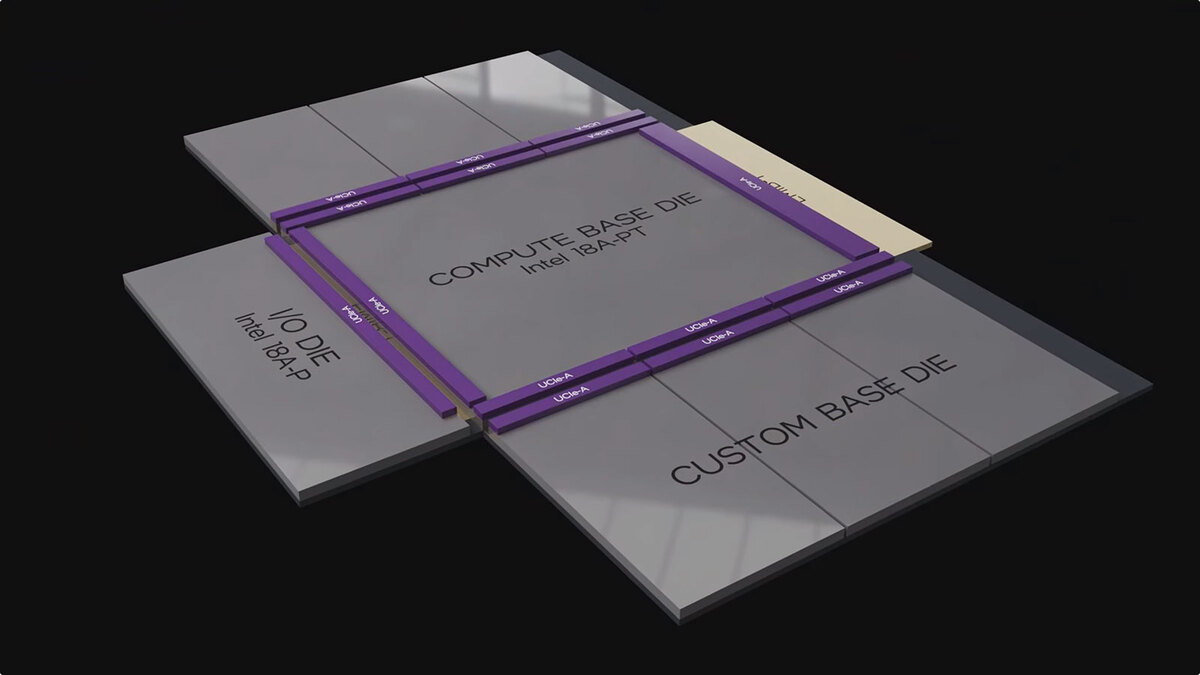

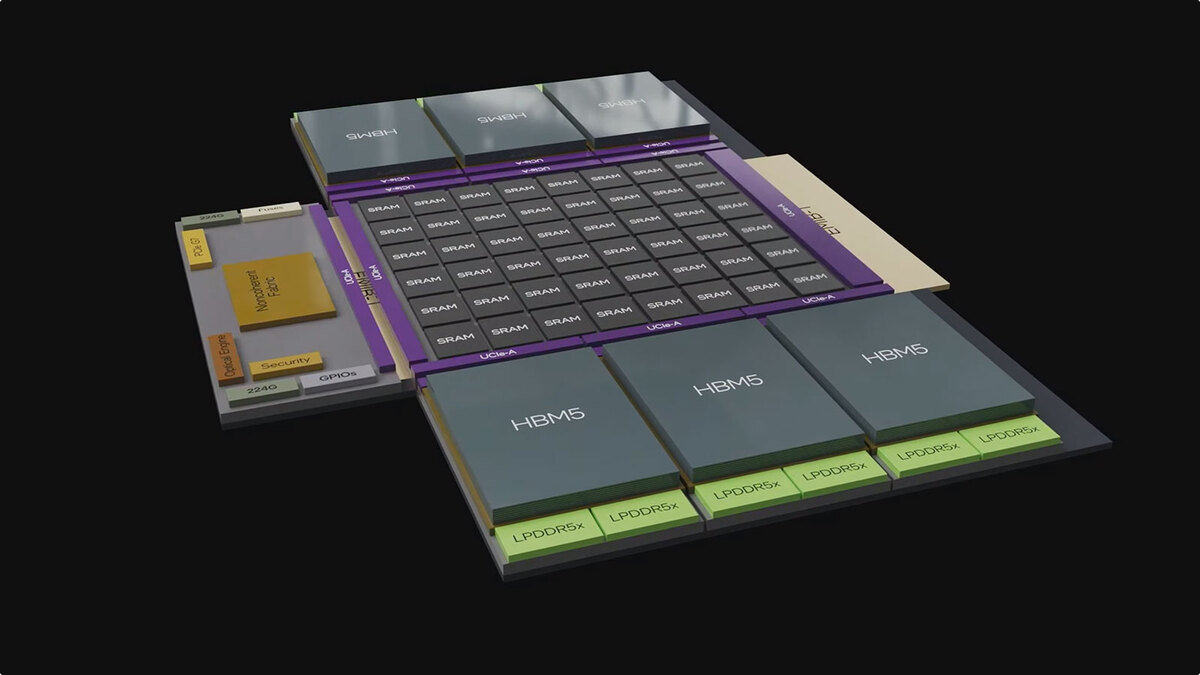

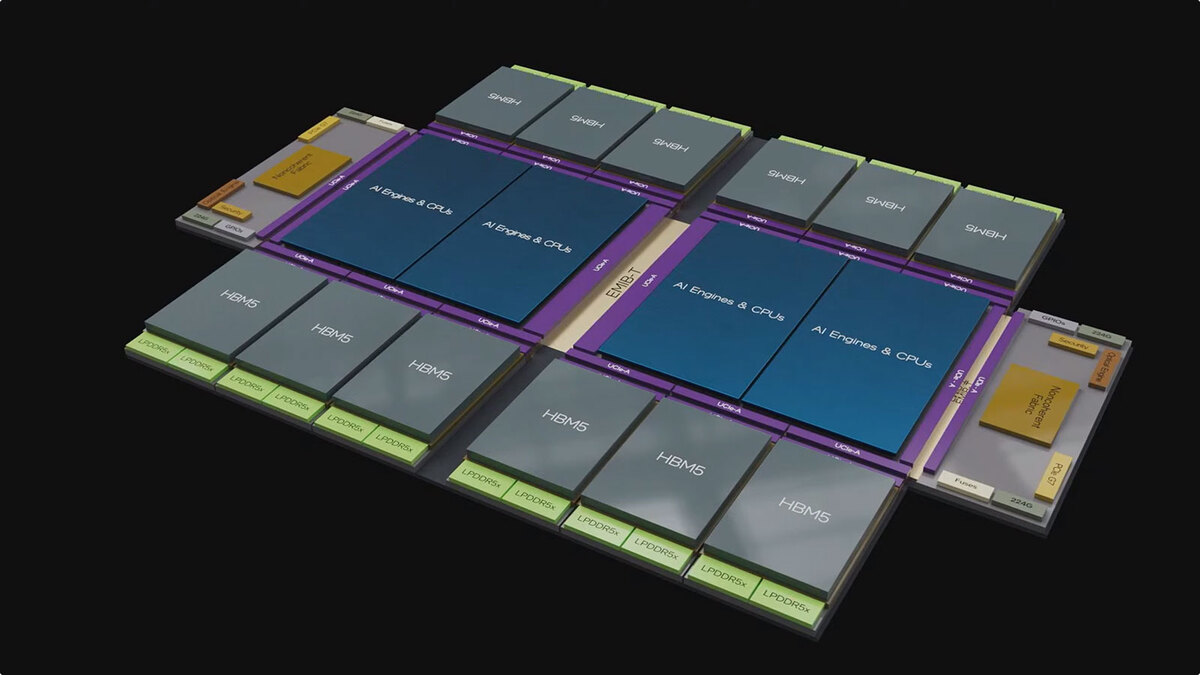

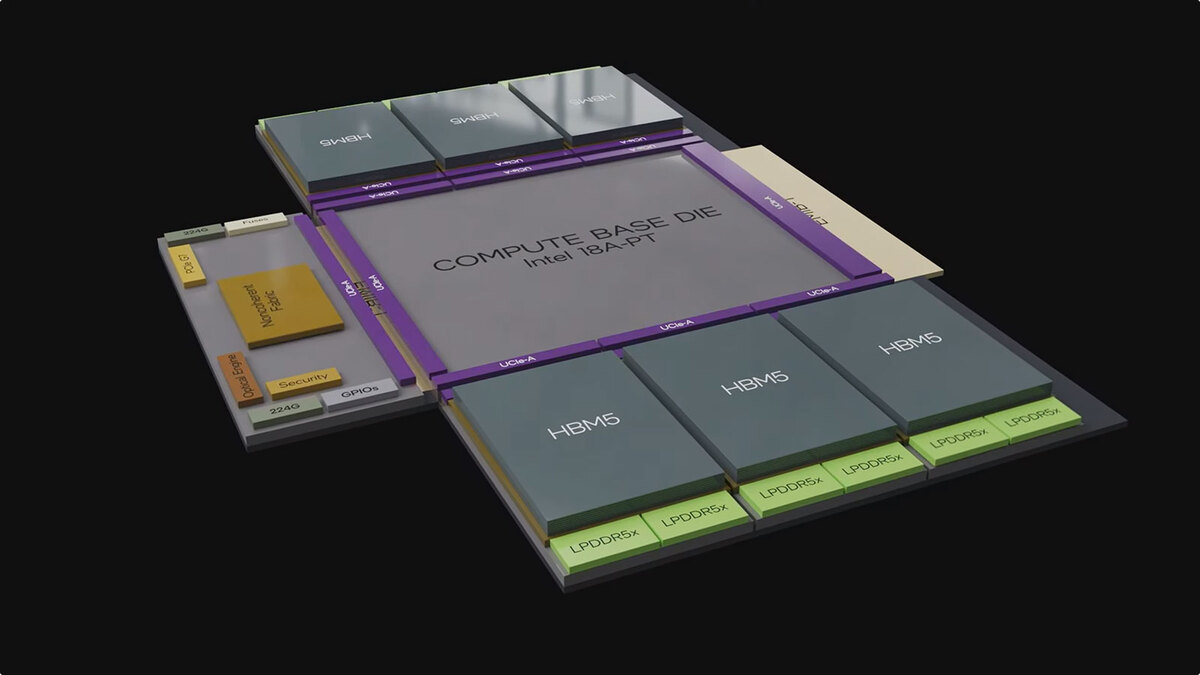

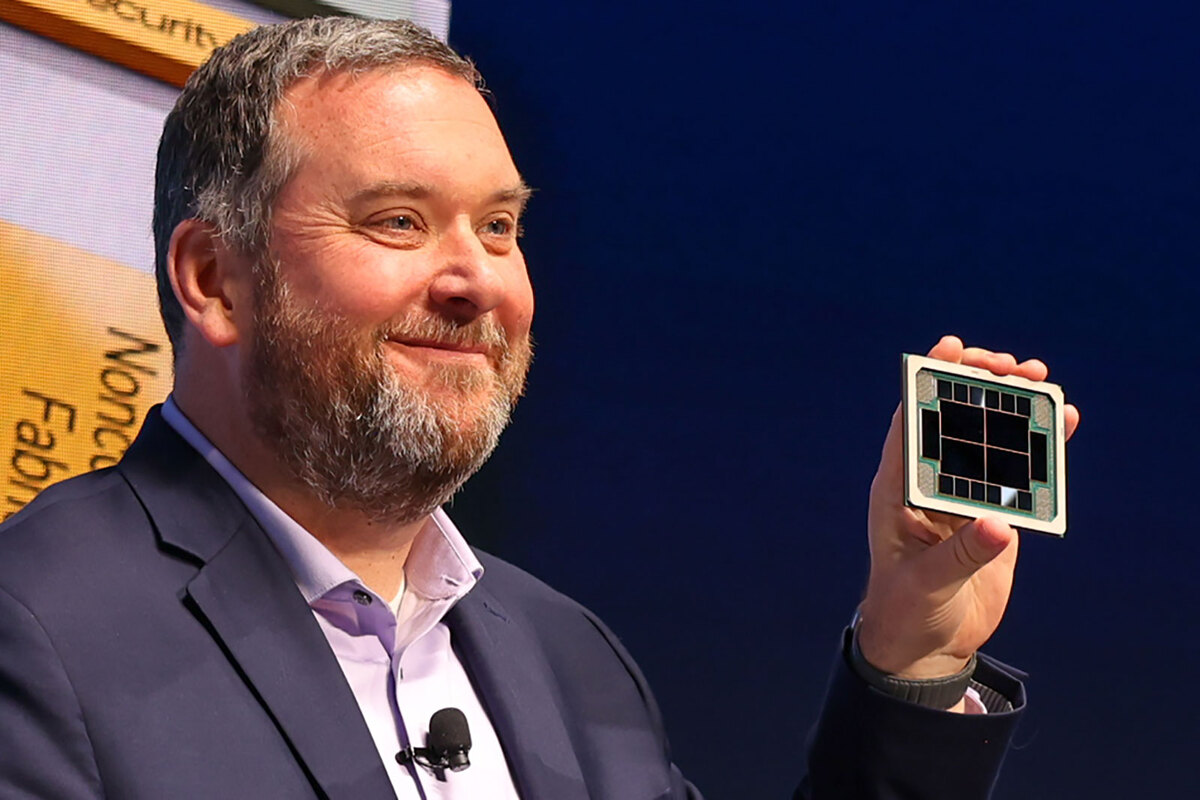

イベントの最後にKevin O'Buckley氏(SVP&GM, Foundry Service)がもう少し細かい話を示したのだが、まず最初に氏が示したのは、現在のIntel Foundryでけっこう複雑なチップレットがすでに構築できることで、実際にサンプルも示された。

Custom Base Dieの上にはLPDDR5xのI/FやHBM5が乗るらしいのだが、そんなのをUCIe-Aで接続して大丈夫か? という素朴な疑問がある。左に突き出してるのはI/O Dieで、なにげにOptical Engineも載っているのがわかる。PCIeはGen7になっているあたり、要するにそういう時期の製品を想定しているということだ

Kevin O'Buckley氏が示したサンプル。遠目には「Ponte Vecchio?」かと思ったがよく見ると異なっている。もっともこれはまだメカニカルサンプルに近いと思われる(そもそもHBM5も存在しない)

先に2027年あたりに3D Photonicsが出てくるという画像があったが、現実にはこういうチップレットの中にコンポーネントとしてEIC/PICを組み合わせたCPOのチップレットが搭載される形になると思われ、登場時期はおそらく2029~2030年頃だろう(その頃にならないとPCIe Gen7のコントローラーが出てこないためだ)と思われる。

そのBuckley氏から、主要なプロセスに関する現状の説明があった。

| 主要なプロセスの現状 | ||||||

|---|---|---|---|---|---|---|

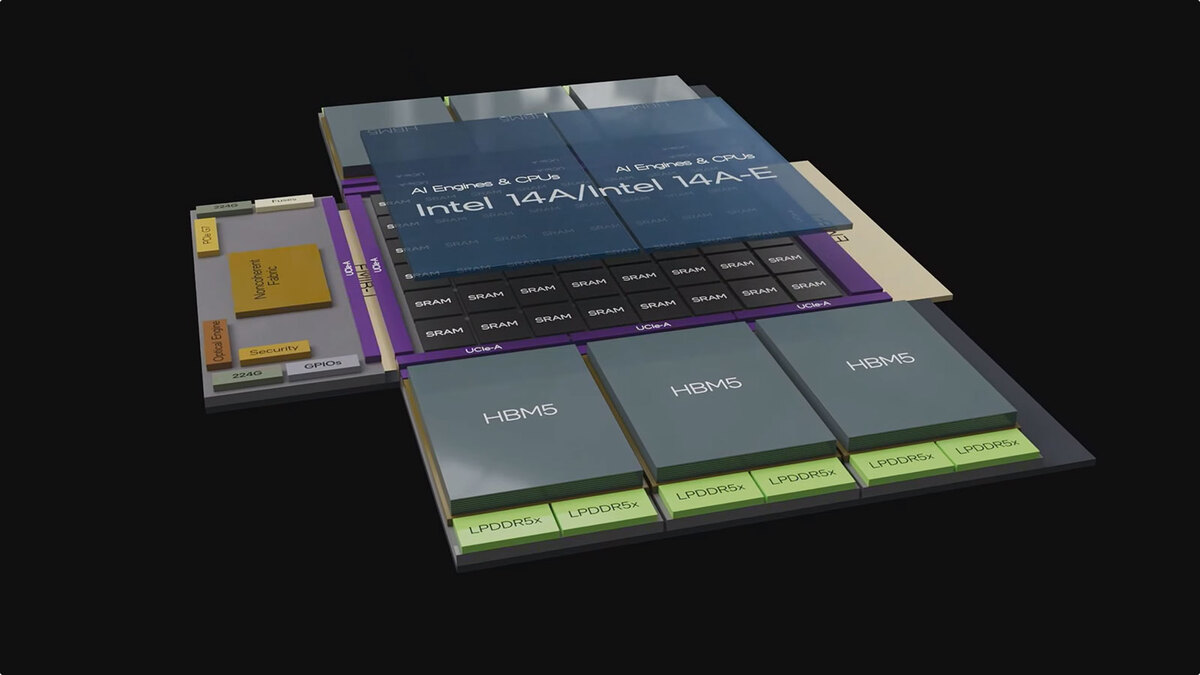

| Intel 18A | リスク生産中。すでにIP及びEDAツールの対応は完了。 | |||||

| Intel 18A-P | 現在工場内で試作した製品の稼働テスト中。IPおよびEDAツールは対応中。 | |||||

| Intel 18A-PT | 現状はまだEDAツール類の対応待ち。基本はIntel 18A-PにTSVの対応を入れただけ。 | |||||

| Intel 14A | 初期版のPDK(0.3くらい?)は特定顧客に提供開始。EDAツールやIPは現在初期対応が行なわれている。 | |||||

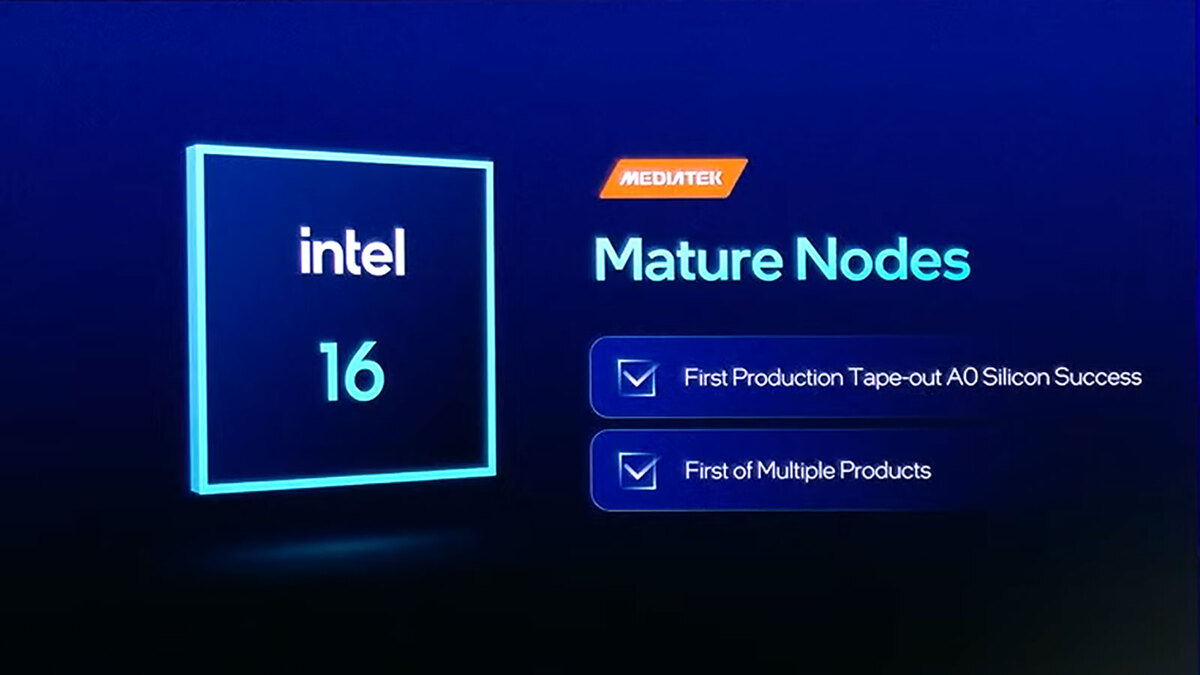

| Intel 16 | 自動車向けプロセスであるが、MediaTekが公式に採用したことを発表。 | |||||

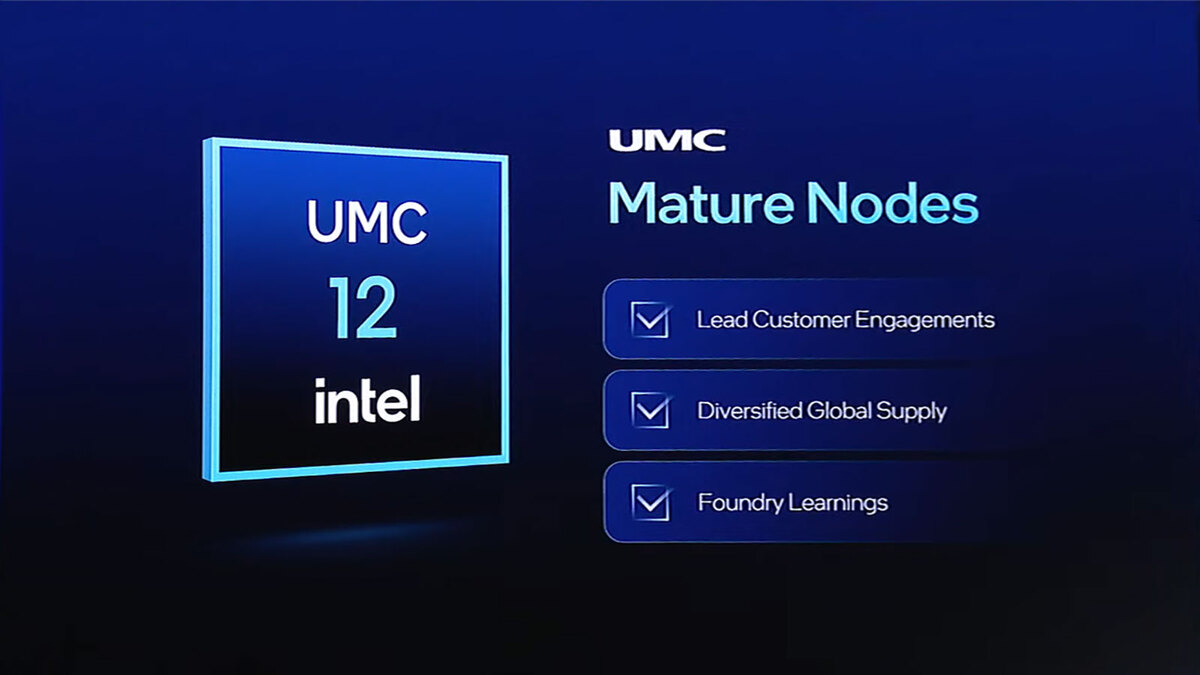

| UMC/Intel 12 | とりあえず一部の顧客の関心を惹くことには成功した模様。 | |||||

Intel 18A-PT。これはFoveros Direct 3Dで積層するチップレット向けという話だが、TSVを入れるとなると当然そのTSVの周囲は配線をよける必要があるので、IPはともかくEDAツール側の対応が必須となる

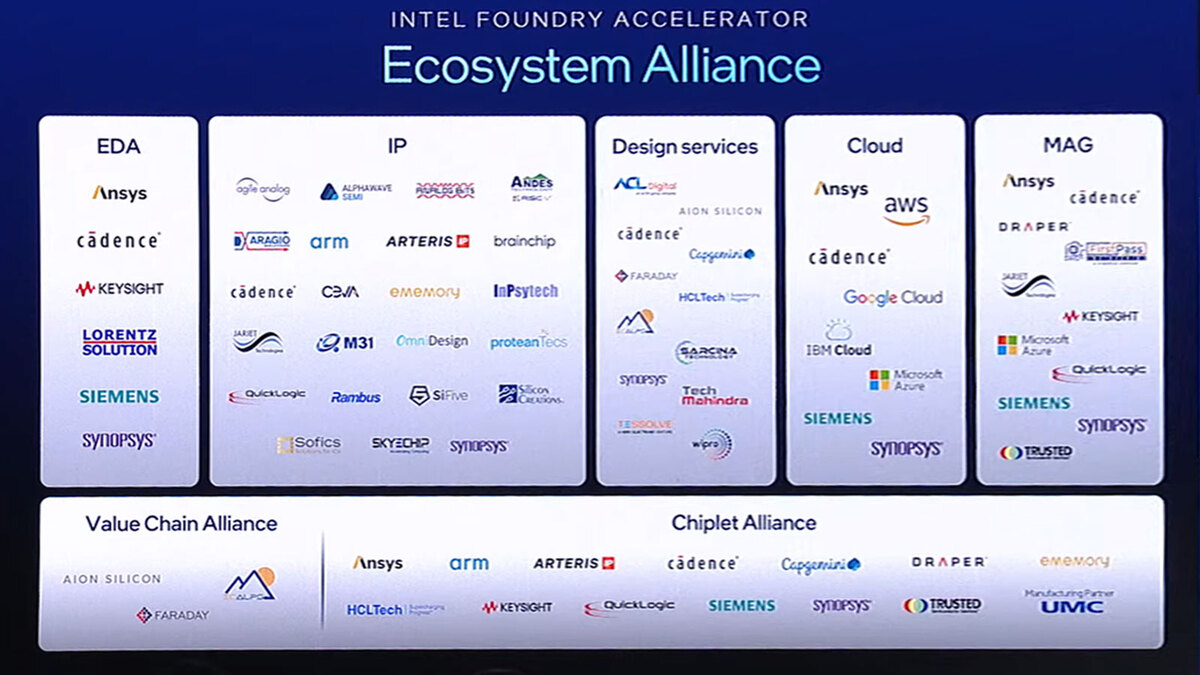

また、すでに堅固なEcosystem Allianceが構築されていることや、連邦政府のさまざまなプログラムによる支援を受けていることもアピールした。

連邦政府のさまざまなプログラムによる支援を受けているという。これがIntel Foundryのユーザーになにか関係あるかと言えば直接的には皆無なのだが、軍のプログラムに入っているというのは、それだけで経営の安定性の担保みたいな部分があるだけに、安心材料にはなるだろう

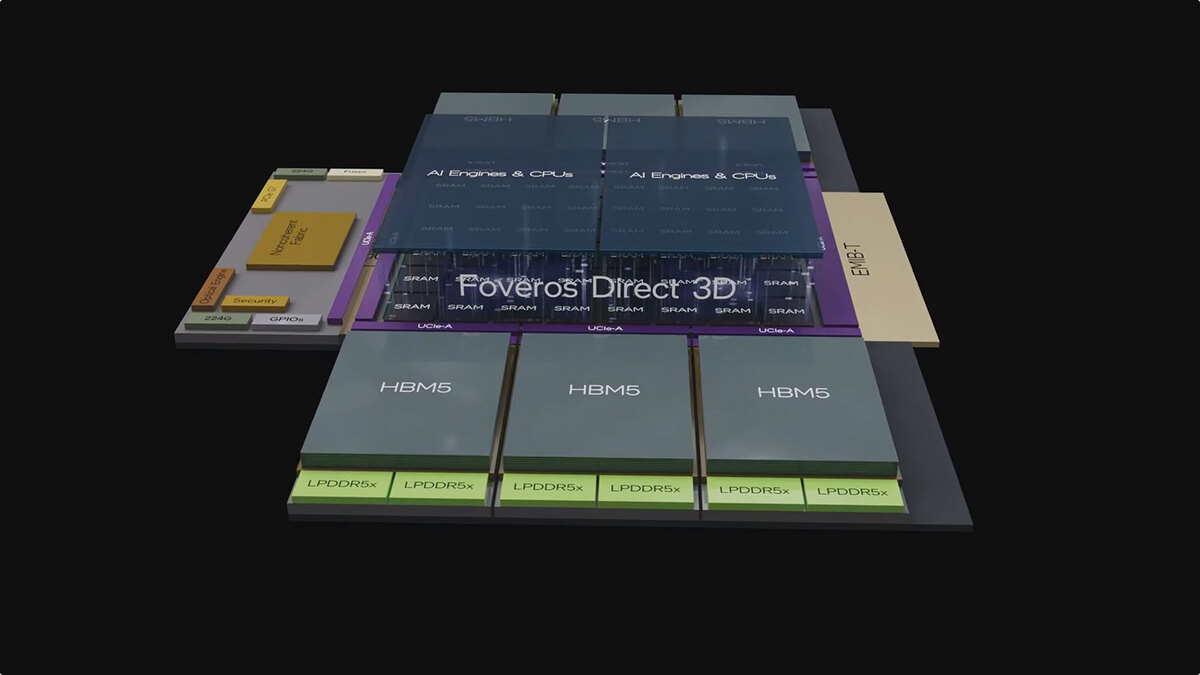

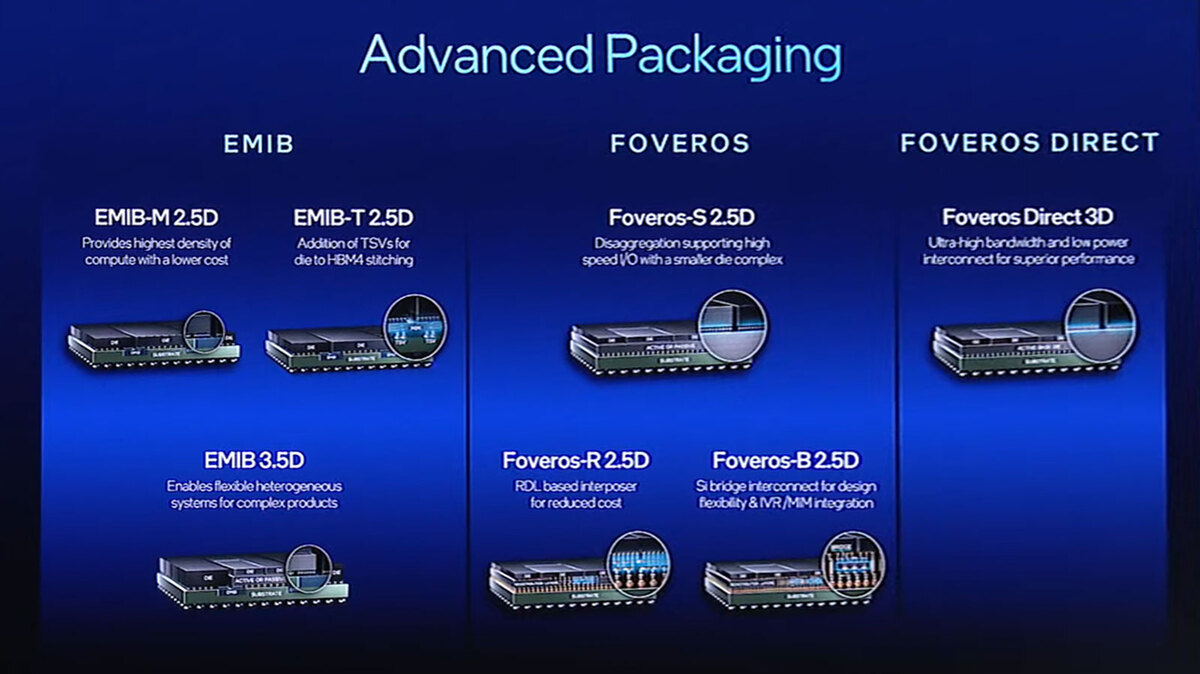

それと先にEMIBのバージョンがいろいろ増えた話に触れたが、その詳細が下の画像である。EMIB 3.5Dはいきなり登場したので、詳細はさっぱり不明である。

| EMIBの種類 | ||||||

|---|---|---|---|---|---|---|

| EMIB-M 2.5D | 従来のものそのまま | |||||

| EMIB-T 2.5D | HBM4実装用にTSVを追加したもの | |||||

| EMIB 3.5D | ? | |||||

| Foveros-S | 従来のFoveros | |||||

| Foveros-R | シリコンベースの代わりに有機パッケージを利用したRDL(Re-Distribution Layer:再配線層)を組み合わせた低価格向け | |||||

| Foveros-B | シリコンブリッジを組み合わせたFoveros。EMIBとなにが違うのか不明。ひょっとするとAMDの2.5D EFB(Elevated Fanout Bridge)というかASEのFOCoS-Bridgeに近いものかもしれない | |||||

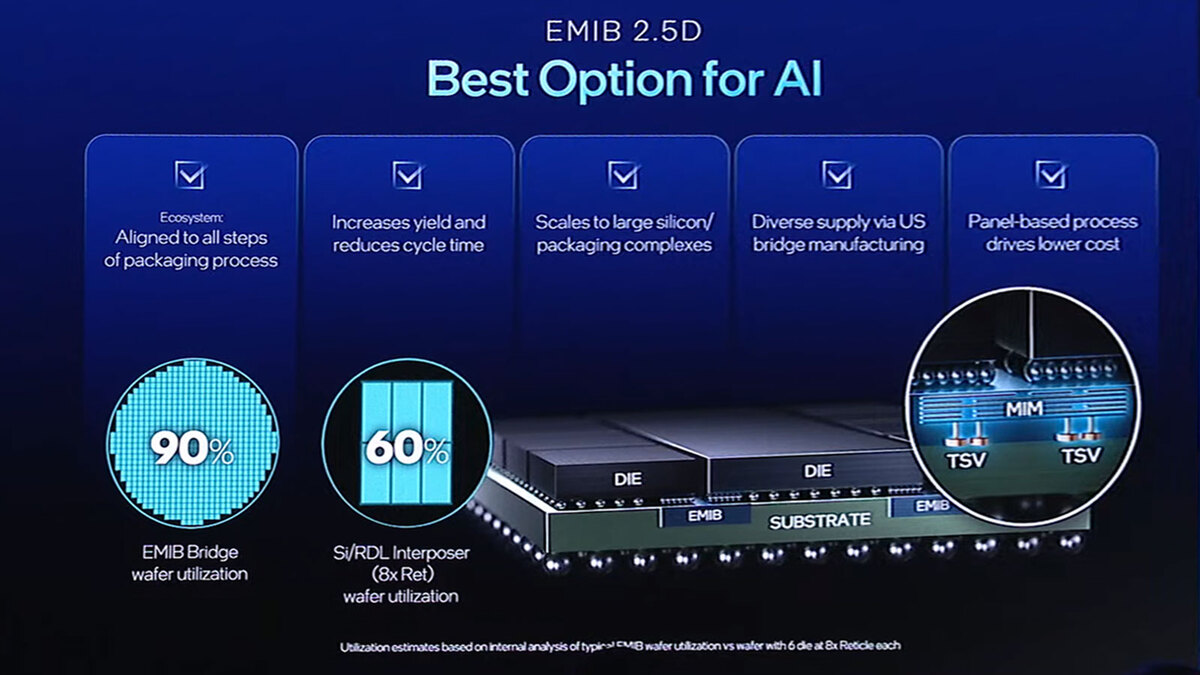

最後に、おもしろいと思ったのはEMIBがAIプロセッサーには最適という話で、要するにシリコン・インターポーザーでダイ全体をカバーすると、ものすごく大きくなってしまうので歩留まりも悪いしコストも高くつく。EMIBなら小さなブリッジの組み合わせなので歩留まりは高いしコストも安くなるというものだ。

EMIBは小さなブリッジの組み合わせなので、AIプロセッサーに最適だという。ちなみに最近有機パッケージベースのRDLは300mm径の円形ではなく、600×600mmの正方形の基板から切り出す方向でOSAT各社は動いており、こちらで低コスト化が期待できそうという話になっている

実際にはインテルのEMIBは、以前はEMIB Bridgeをパッケージに埋め込むコストが非常に高いと言われていた時代もあったのだが、もう今では相対的に安いという時代になってきているのかもしれない。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります