第823回

Intel 18AはIntel 3と比較して性能/消費電力比が15%向上 インテル CPUロードマップ

2025年05月12日 12時00分更新

Intel 18AはIntel 3と比較して

性能/消費電力比を15%向上

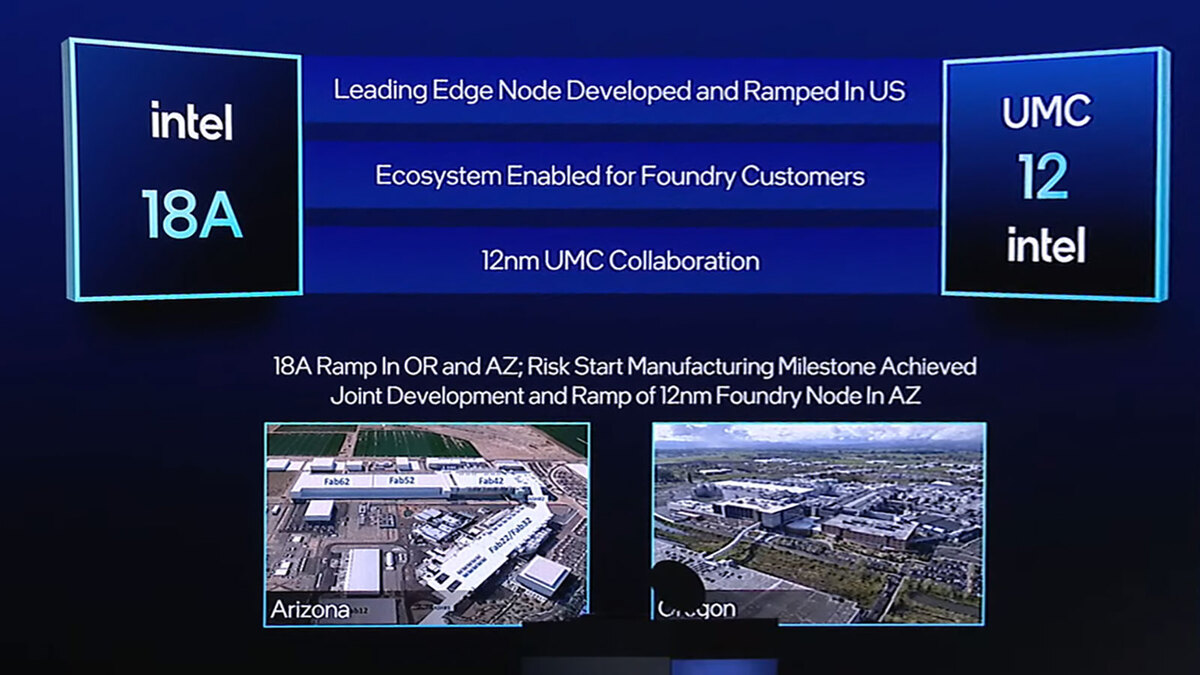

次にIntel 18AとIntel/UMC 12である。Intel 18Aはアリゾナとオレゴンで、Intel/UMC 12はアリゾナでの製造とされる。アリゾナの方はFab 52/62がこれに充てられ、一方オレゴンはまず先行開発と少量の量産がD1Xで行なわれ、それが一段落したらIntel 14Aに移行するものと思われる。

というのはオハイオに関しては"Pause"までは行かないまでも建設がスローピッチになっており、当初は2025年に稼働開始だったのがその後2027年になり、今では2030年ないし2031年に稼働という話になっているからで、これはIntel 14Aの生産開始に到底間に合わない。おそらくだが、Fab 52がIntel 18A、Fab 62がIntel 14Aといった格好になるはずだ。

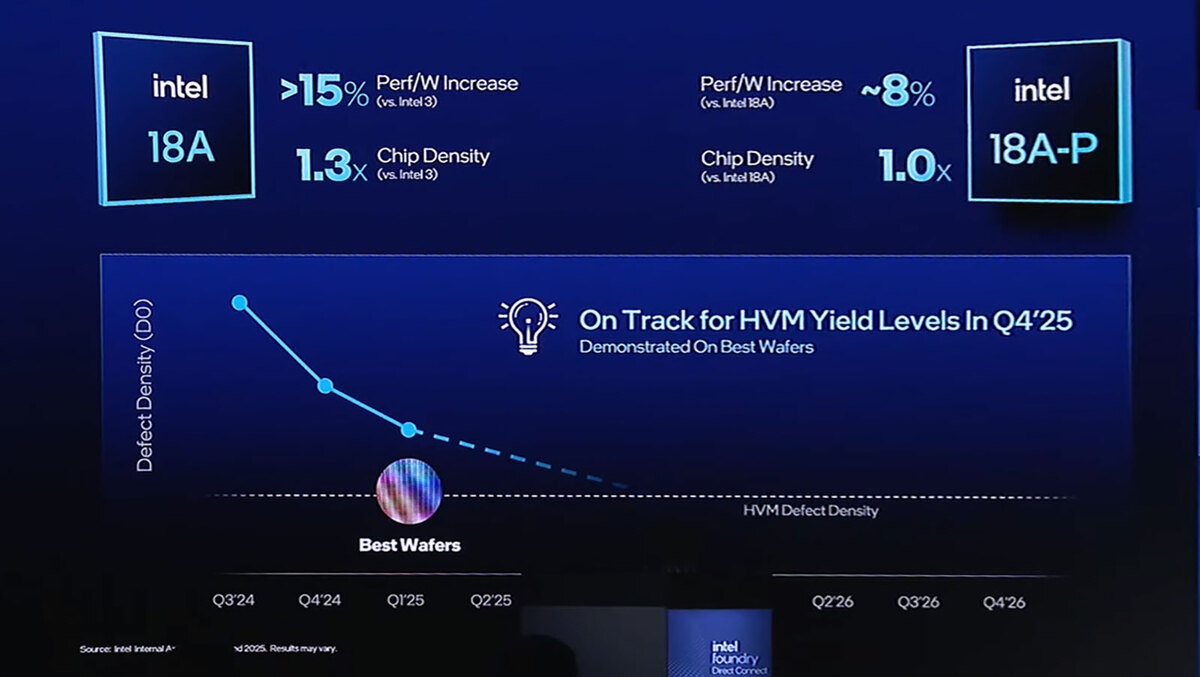

そのIntel 18Aの現在の状況を示したのが下の画像である。欠陥密度(Defect Density:DD)は順調に下がっており、このままいけば2025年第4四半期の量産開始時には十分DDは量産に耐える低さが期待できる、としている。

またIntel 18AはIntel 3と比較して性能/消費電力比を15%、ロジック密度を30%向上できるとしており、これに続くIntel 18A-Pはロジック密度は同等だが性能/消費電力比をIntel 18A比で最大8%程度改善できるとしている。Intel 3比で言うなら40%の性能/消費電力比改善となるわけだ。

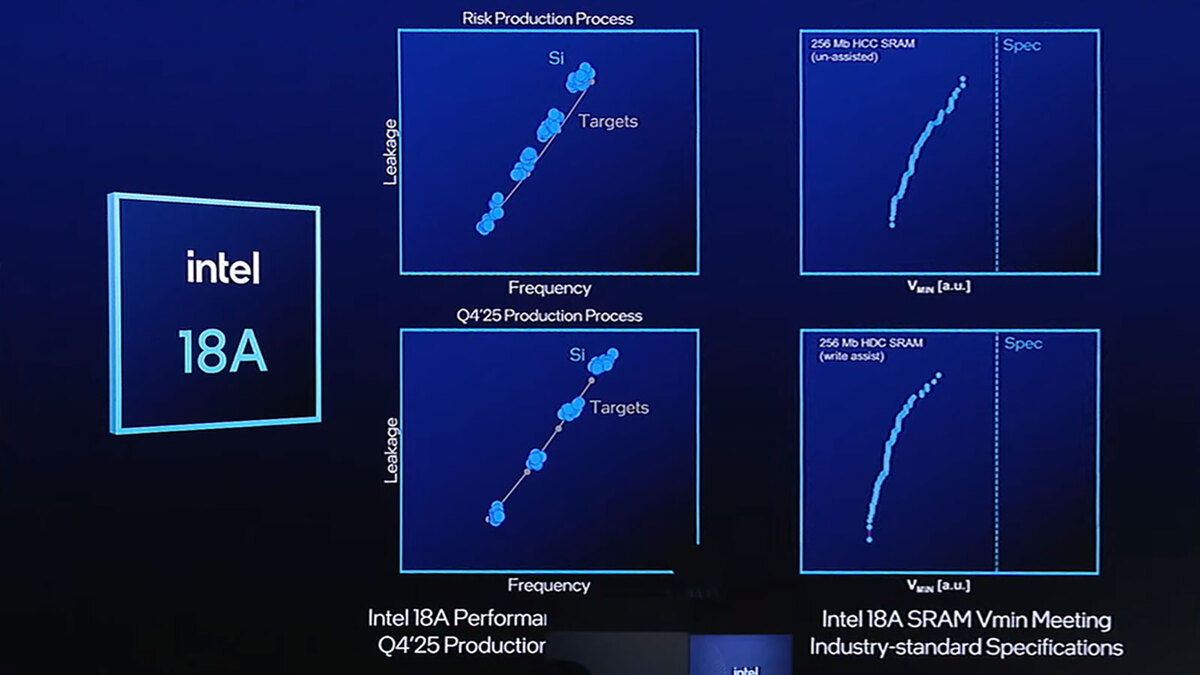

そのIntel 18Aの性能周りが下の画像だ。左の2つが動作周波数とリーク電流の関係で、動作周波数は現状で目標の90~95%程度に達しており、今後も改善していくとのこと。またSRAMについて高速型(HC:High Current)と高密度型(HD:High Density)のVmin(最小動作電圧)を示したのが右側の2つのグラフで、どちらも良い結果を示しているとしている。

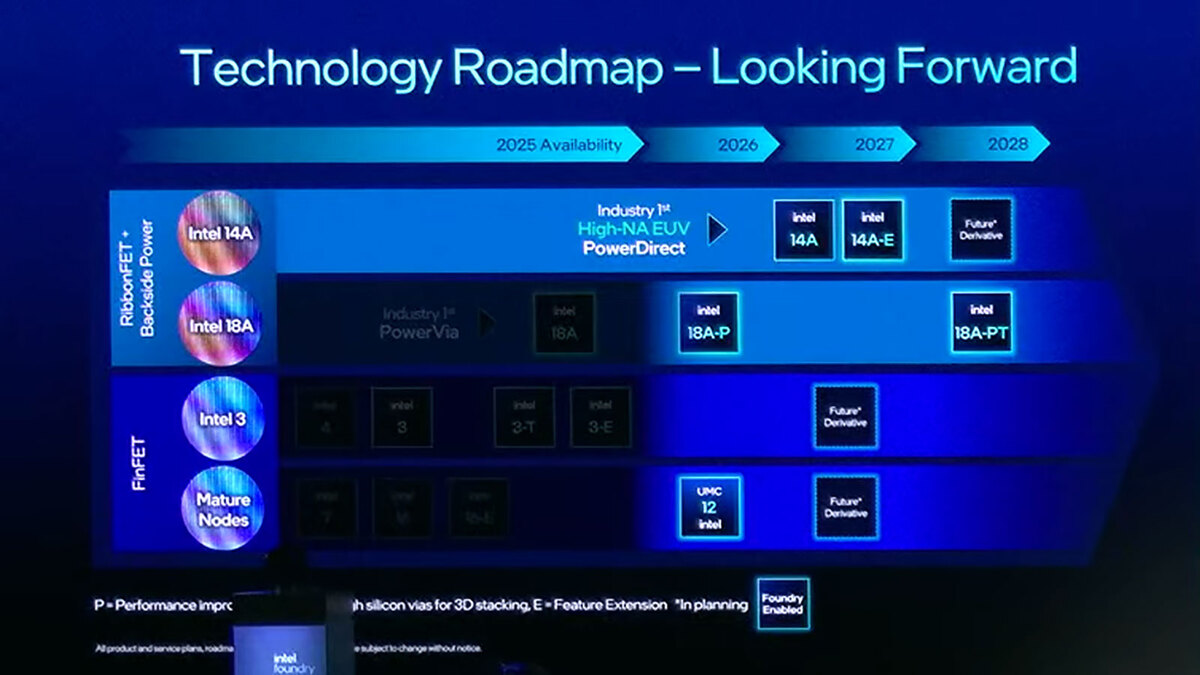

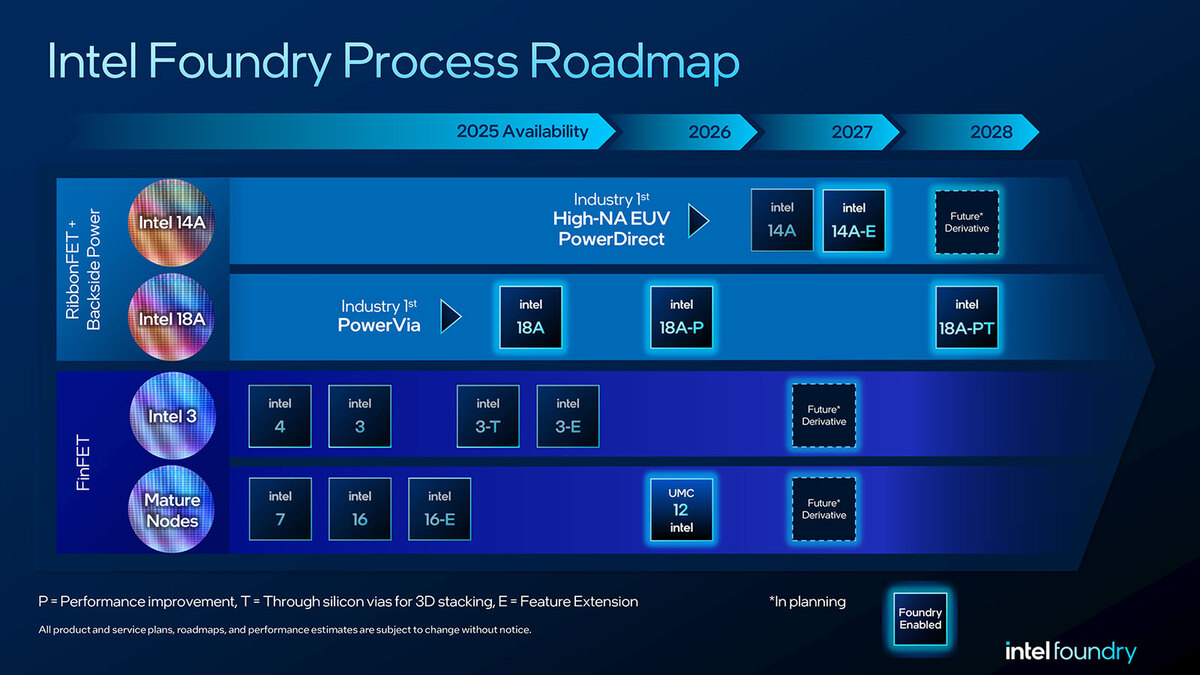

続いてが今後のプロセスの話。下の画像が今後のロードマップとして公開されたもの。前述のプロセスノードとまとめたのがその下の画像となる。

これと昨年3月のロードマップを見比べると、以下のようになる。

- Intel 3-PTがどこかに消えた。

- Intel 18A-PTが出現した。

- Intel 14-E、Intel 3-E、およびIntel/UMC 12の3つについて派生型が予告された。

このうちIntel 3-PTは昨年の段階では作ることが決定していたのが、今回はFuture Derivative(将来の派生型)に一歩後退したと考えるのが正しそうだ。要するに顧客の見込みが薄そうなので、現時点では一旦白紙に戻したという感じだろうか。

逆にIntel 18A-Pは積極的にチップレットのコンポーネントとして提供すべく、TSVを利用できるIntel 18A-PTを追加したというあたりか。UMC/Intel 12に関しては後述するが、まだそこまで詳細は決まっておらず、一応将来のオプションとして提供することを示しておいた、というあたりだろうか?

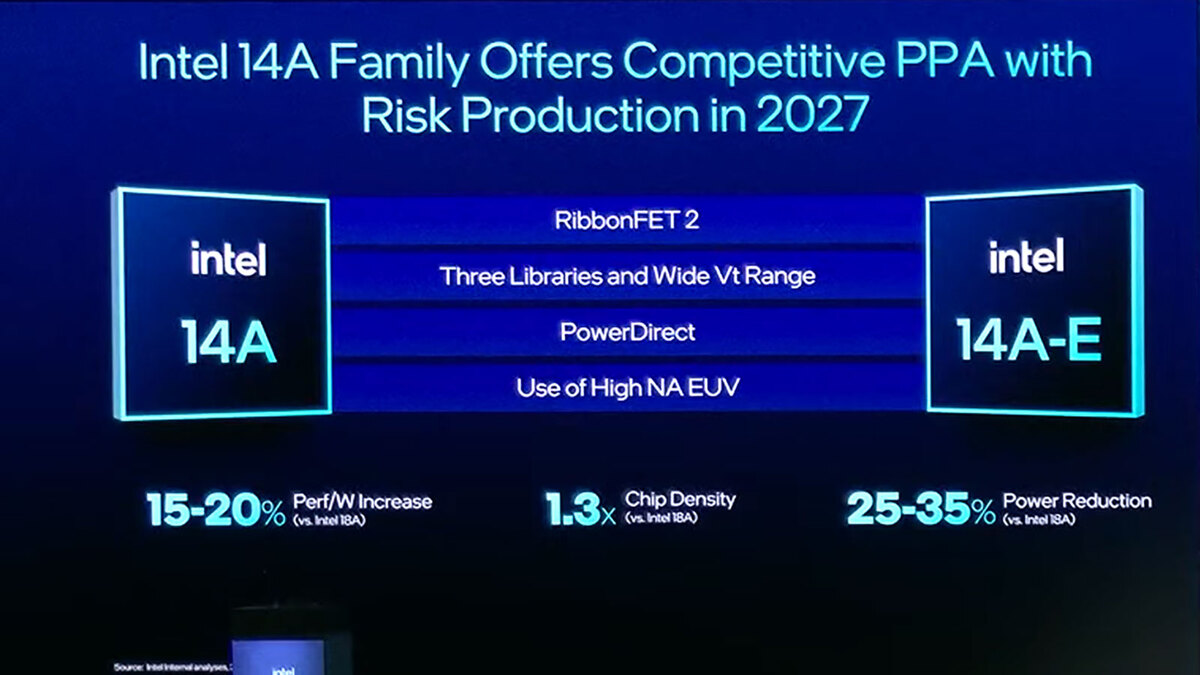

そのIntel 14AとIntel 14A-Eの想定スペックが示された。Intel 18A比で性能/消費電力比が15~20%、ロジック密度が30%向上し、消費電力削減に全振りすると25~35%の削減になる、としている。

このIntel 14Aでインテルは業界に先駆けてHigh N/A EUVを導入するわけだが、さて? ちなみにトランジスタ自体もRibbonFET 2になるとしているが、これはプロセスノードが一段進むから当然ではある

また今回は詳細が示されなかったが、第2世代のBS-PDNとしてPowerDirectを搭載。また3種類のライブラリーと広範なVtをサポートすることも示された。この3種類のライブラリー、要するにTSMCがN3で導入したFinFlexや、そのN2で後継であるNanoFlexと同種のものと思われる。

なおインテルはこれにTurbo Cellという名称を付けている。考え方はFinFlex/NanoFlexと同じで、クリティカルパスには高速動作のCellを、速度よりもロジック密度が重要なところ(例えば2次/3次キャッシュなど)には低速ながら高密度なCellを、それ以外の所は中間的なCellを利用することで、性能を確保しながら低消費電力性や省サイズ性を確保できるようにする、というものだろう。

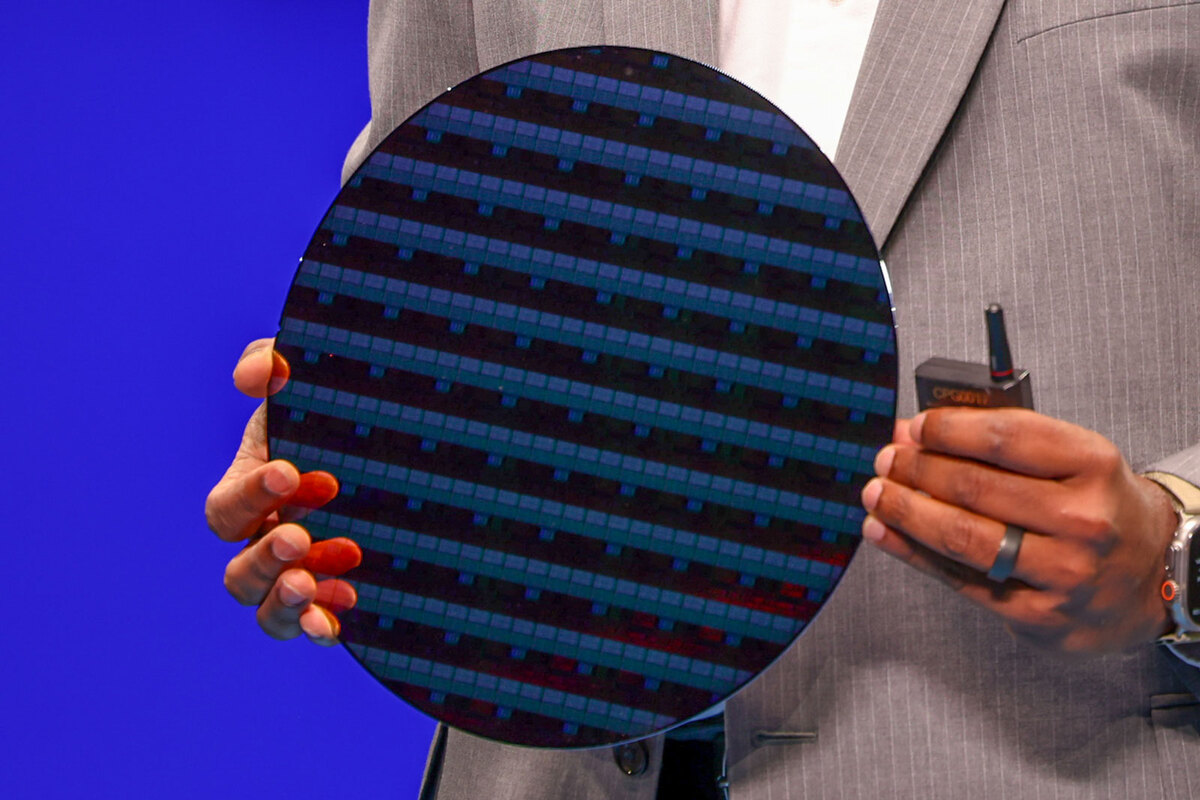

ちなみに実際にIntel 14Aで製造したウェハのサンプルも示された。まだ現在は基本的なライブラリーレベルでのテスト用チップの製造で、具体的な製品ではないとは思われるが、一応TWINSCAN EXE:5000を稼働状況に持ち込んでいることは確認できたことになる。

2023年の12月末にASMLがTWINSCAN EXE:5000をインテルに向けて発送することを発表し、2024年1月早々にそれを受け取ったことが発表されていたが、そこから1年ほどで設置・調整・テストを経て実際にウェハーを製造できる段階にきているわけで、まずは順調と言っていいだろう。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります