ビットエラーレートを少なくすると消費電力が増える問題

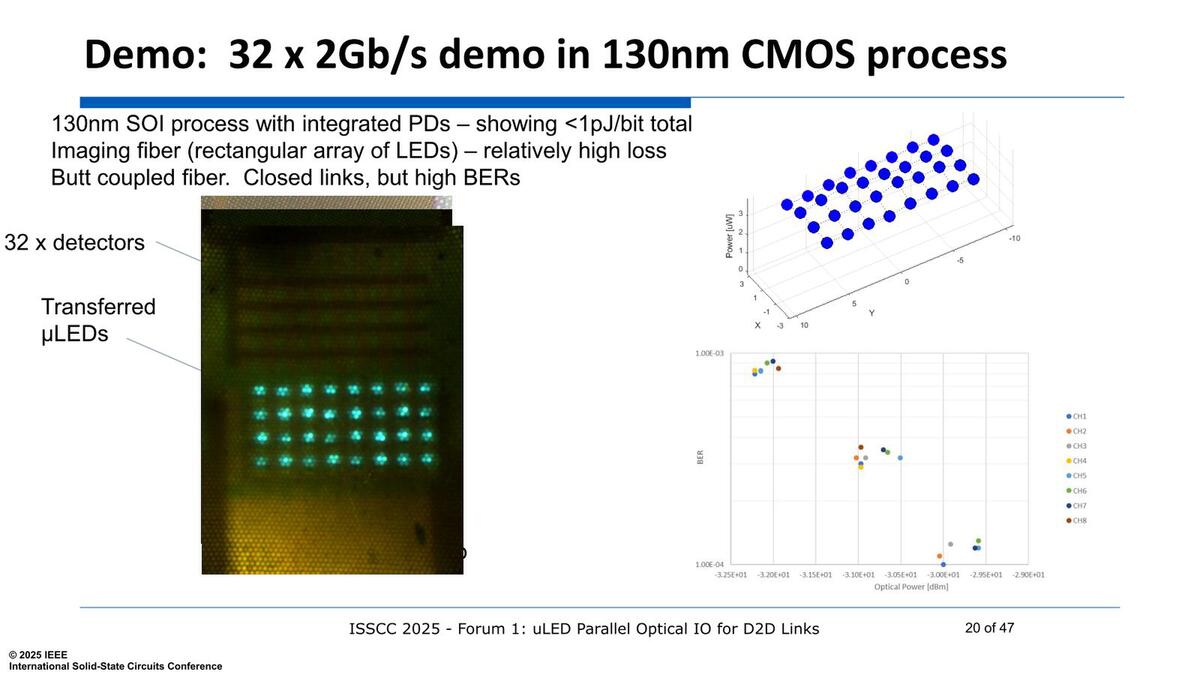

現時点ではまだ消費電力とBERがバーターになっていることが、下の画像の右下のグラフからも見て取れる。BERが10E-3と無茶苦茶多くても許容できるのであれば、消費電力は0.2pJ/bitを下回るほどに小さい。逆にBERを10E-11程度まで確保しようとすると、ほぼ0.8pJ/bit程度まで消費電力が増えてしまう格好だ。

このあたりは発光素子の構成にも関係しており、下の画像では2種類の寸法のものを比較している。やや消費電力が多いのはサファイア基板上に構築した寸法8μmのもの、低いのはシリコン基板上に構築した寸法15μmのもので、寸法を大きくすると比較的BERが下げやすい傾向が見て取れる。

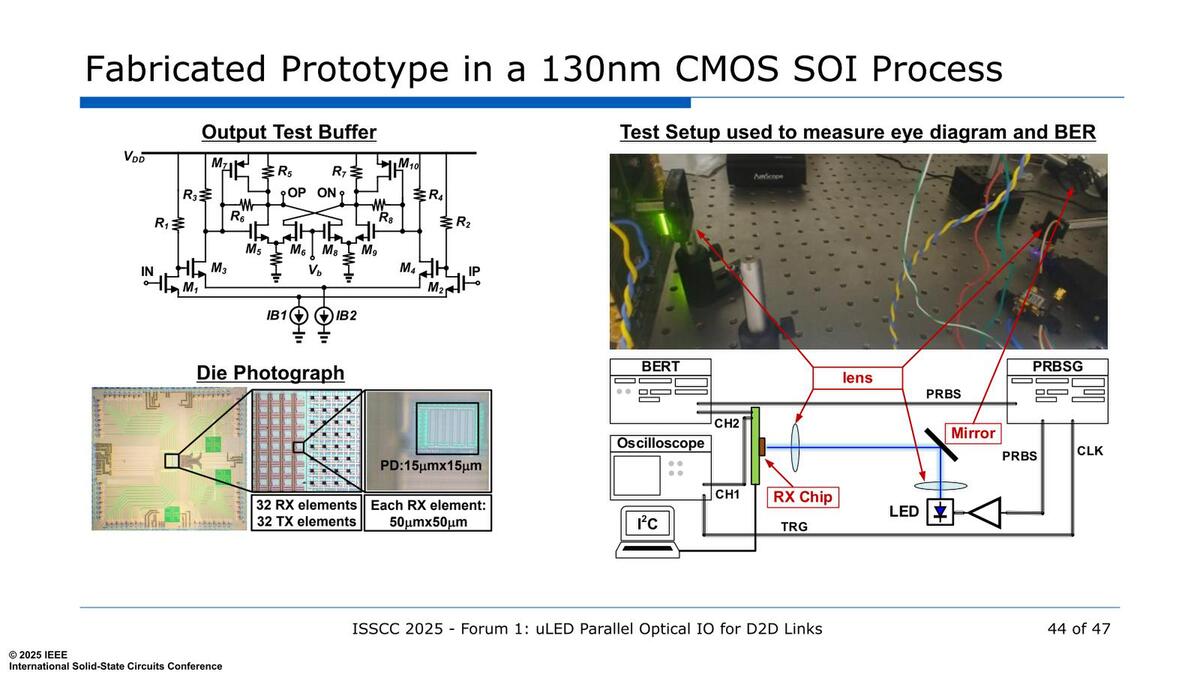

下の画像は実際の試作した送受信部であるが、PD(Photo Detector)そのものは15μm角、そのPDを含む1ch分の受光部全体は50μm角になっている。

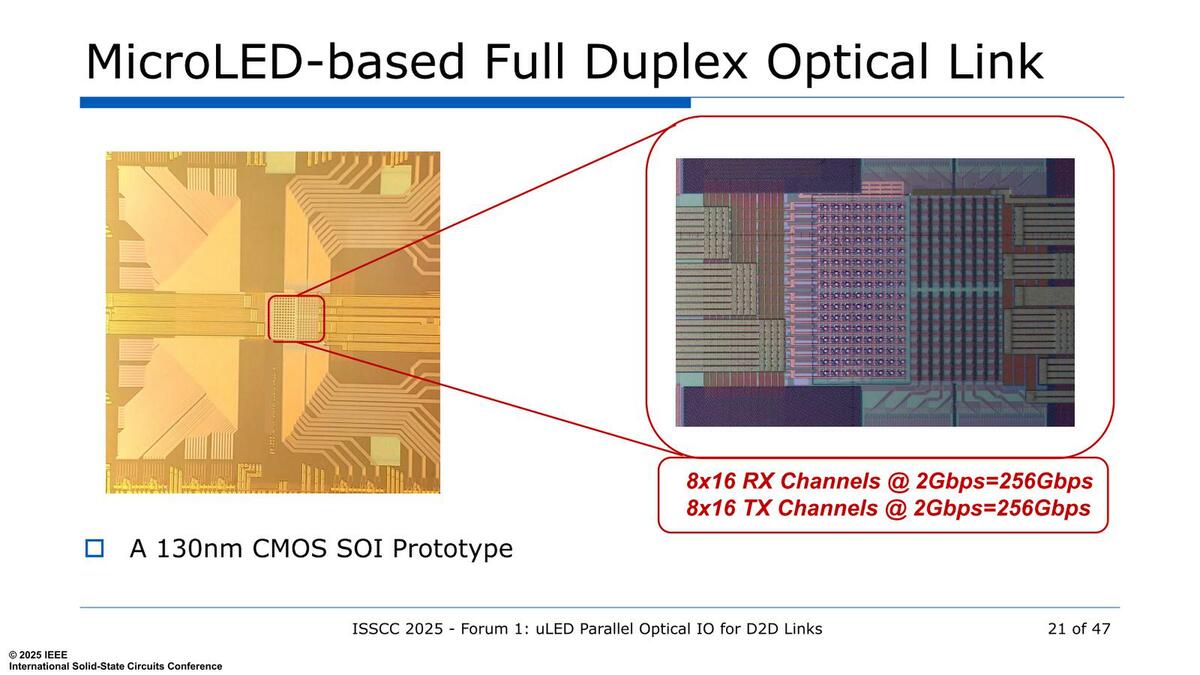

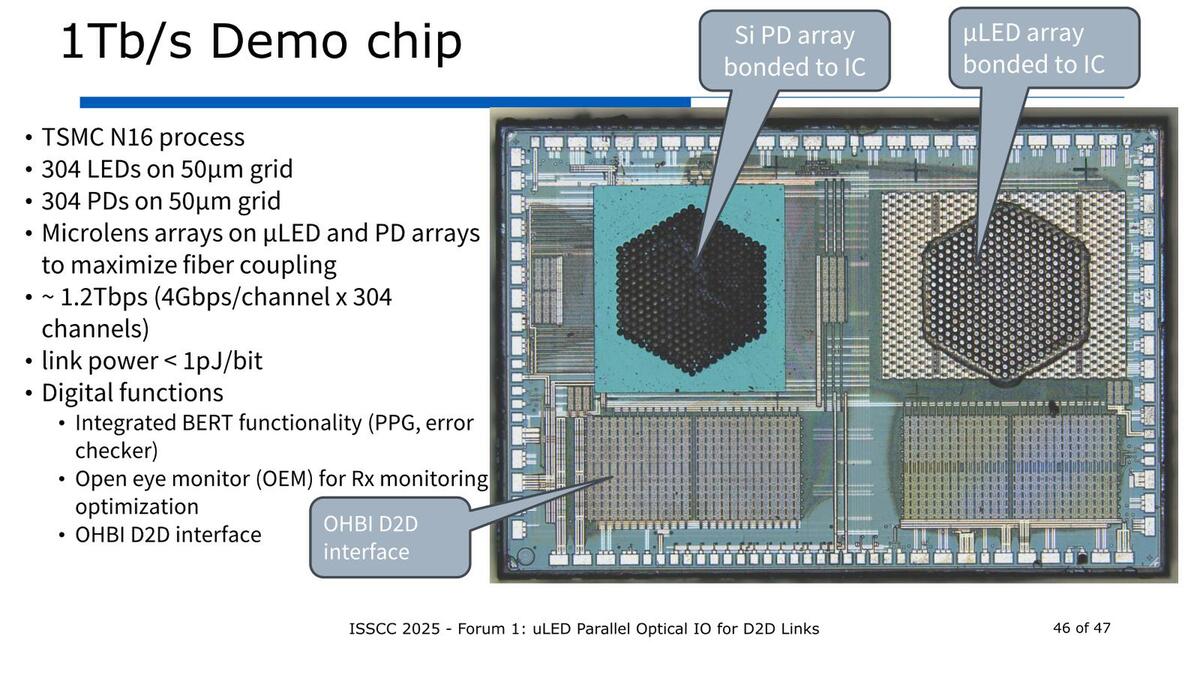

さて上3つの画像は8×4で32ch構成だが、他にも128ch構成や304ch構成の試作もされており、こちらではトータルで256Gbpsや1.2Tbpsの通信が可能になっている。

この1.2TbpsのものはOHBI(Open High Bandwidth Interconnect)という、OCP(Open Compute Project:Metaが主導を取って結成されている、サーバーの規格などを定める標準団体)に提案されたI/Fであまり一般的とは言えないのだが、あくまで研究用と考えればそれほどおかしくないし、今後他のI/Fに切り替えるのも容易だろう。

そもそも上の画像のものはTSMCのN16プロセスだから、既存のロジックCMOS用プロセスで製造されているわけで、例えばSOICを使って既存のSoCのダイの上に、直接このMicroLEDの送受信ダイを3次元積層するなんてことも技術的には可能であろう。このあたりはこの先なんとでもなる話であり、将来的にはロジックダイに直接これを仕込むことも十分可能だろう(その場合、今度は2つのチップレットの間の光の送受信の経路をどう構築するかという問題が出てくる)。

論文ではさらに、それほど回路を複雑化させずにBERを引き下げるための方法論や送信/受信の回路構成の提案などをしているが、さすがにこのあたりは細かい話になるので割愛する。ただ、従来の光イーサネットなどに使われる技法に比べるとかなりシンプルなもので、消費電力やレイテンシーが無駄に増えることもなさそうな見通しである。

あくまでも将来技術の1つの候補でしかないのだが、Die-to-Dieの光接続の可能性を見せてくれる話であった。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります