第817回

実現困難と思われていたUCIe互換のチップレット間インターコネクトをTSMCとAMDが共同で発表 ISSCC 2025詳報

2025年03月31日 12時00分更新

UCIeの仕様を満たす結果を残し

不可能な数値ではないことを立証

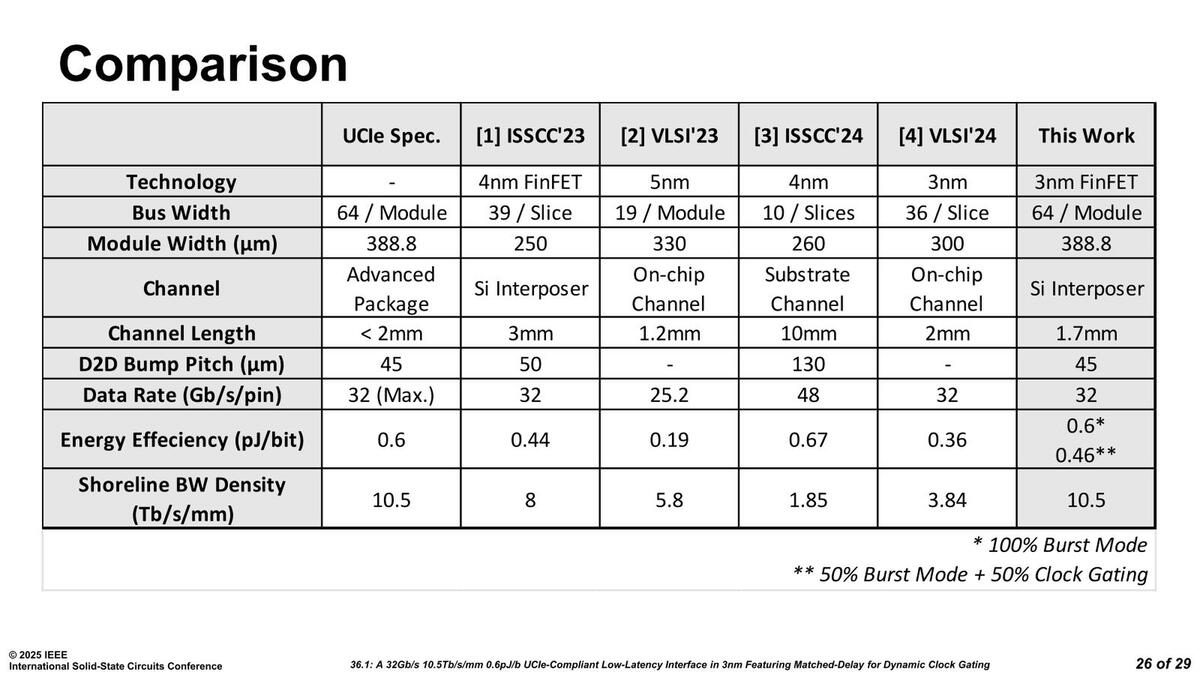

消費電力の内訳が下の画像だ。消費電力が一番大きいのは送信そのものではなく、送信側のSerDesとFFE/Deskewなどの伝達エラーを改善するための仕組みであり、次いで受信側の信号補正とDeSerとなり、送信そのものは3番目というのはなかなか興味深い。これでBurst Modeで0.6pJ/bitというUCIeの仕様を満たす結果が実現できることを実証したのは素晴らしい。

消費電力の内訳。ちなみに0.6pJ/bitは0.7V動作で16GT/秒以上の場合。12GT/秒以下では0.5pJ/bit、0.5V動作ならそれぞれ0.25pJ/bit、0.3pJ/bitと定義されており、次はこうしたケースの実証に移るのかもしれない

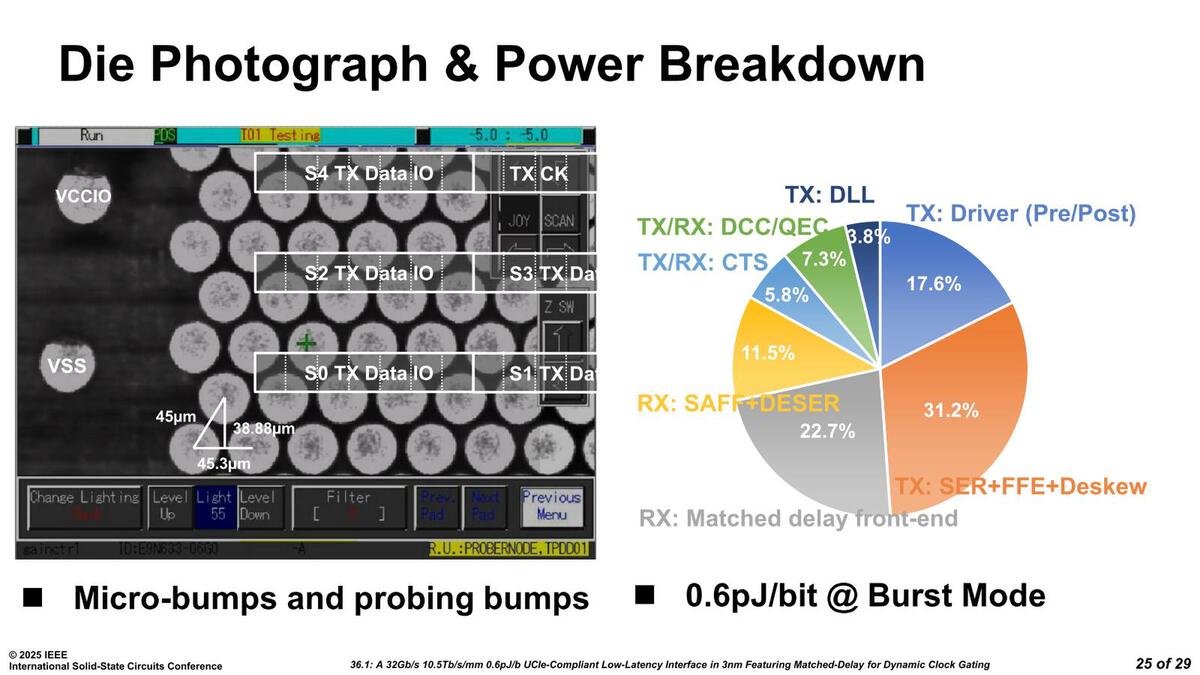

下の画像が今回のまとめである。ちなみに消費電力はClock Gatingを使うと0.46pJ/bitとなり、これは12GT/秒以下の場合の0.5pJ/bitを満足する値である。少なくともTSMCの3nmを利用したダイを利用することで、UCIe 1.1に定義されたAdvanced Packageの仕様を満たすことが可能、という実例を示せたのはかなり大きな成果であろう。

UCIeのI/F IPを提供開始したという発表は複数社(Alphawave Semi/Avery/Cadence/Synopsys)が行なっているのだが、Standard PackageはともかくAdvanced Packageに関しては消費電力が厳しいだけに、どこまで実現できるか疑わしいところもあったのだが、実際に動作させた結果が示されたわけで、実現困難/不可能な数値ではないことが立証できたのは喜ばしいことではある。

ただ逆説的に言えば、UCIeを利用してChipletを構築しようとすると、TSMC N3以降が必要になる、ということかもしれない。Computeチップレットはそれでもいいのだろうが、IOチップレットなどはTSMCのN5やN6を使うケースが多い。こうしたものでも今回と同等のことが可能なのか、それとももっとスピードを落とさないとだめなのか、はまだ議論の余地がありそうだ。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります