第817回

実現困難と思われていたUCIe互換のチップレット間インターコネクトをTSMCとAMDが共同で発表 ISSCC 2025詳報

2025年03月31日 12時00分更新

クロック信号の品質補正回路はデジタル回路で構成し

Clock Gatingの解除に即時対応する必要がある

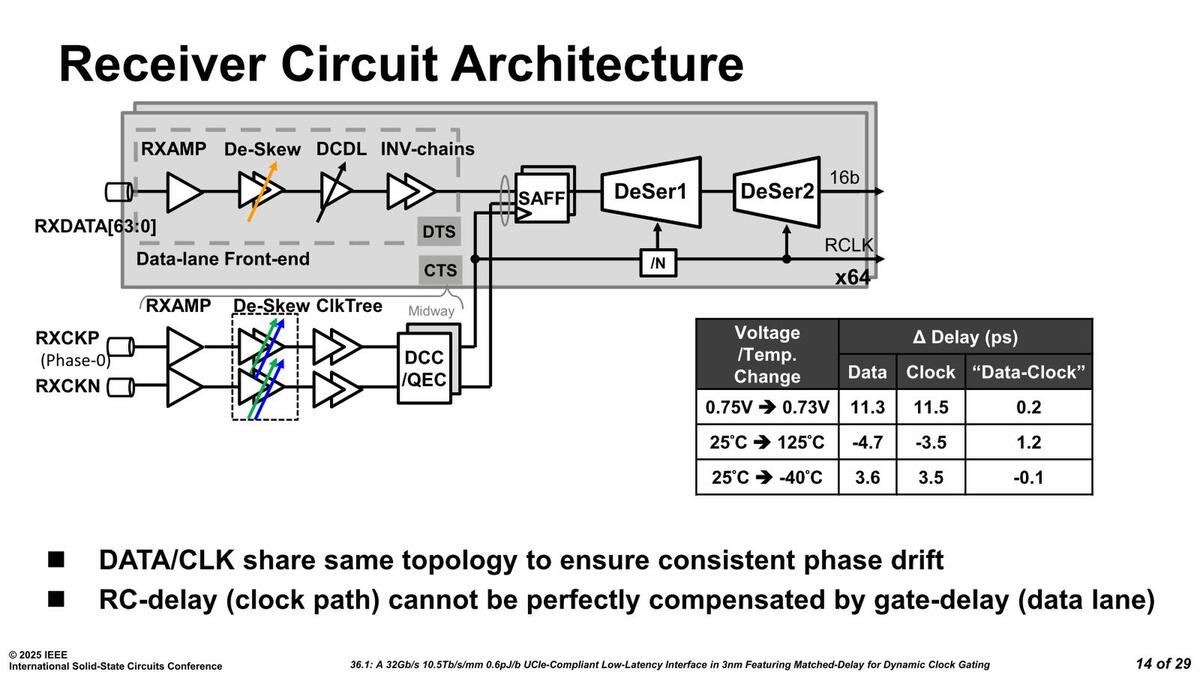

一方受信側回路が下の画像である。ここでのポイントはクロック信号の受信回路である。Clock Gatingが行なわれているケースで、Gatingが解除された場合、解除された直後の最初のクロック信号で直ちにデータを受信できるような仕組み(論文ではこれをMatched-delay Architectureとしている)が必要である。

このために、DCC(Duty Cycle Corrector)およびQEC(Quadrature Error Corrector)というクロック信号の品質補正回路は、アナログではなくデジタル回路で構成され、Clock Gatingの解除に即時対応できるようにする必要がある、としている。

ちなみにこのDCCとQECでは、Duty Cycle Errorを0.3%未満、直交位相エラーを330fs以下に抑えられるように設計されているとのことだ。特に、激しい電圧降下が起きた場合、これはClock Preamble(クロック信号の先頭部分に付く特別な信号)だけではリカバリーできず、32GT/秒のレシーバー側のDLL(Delay Locked Loop:タイミング調整回路)でカバーできる能力を超えるとされる。

こうした状況への対策として、受信側はフロントエンドを通した後のSAFF(Sense Amp Flip Flop)でRXCKP/RXCKNのクロック信号でタイミングを同期させることで、クロック信号とデータ信号の位相を一致させるように工夫している。右の表は電圧あるいは温度変化があった場合のクロック信号とデータ信号のズレを測定したもので、例えば20mVの電圧変動があると11ps以上の遅れが発生するが、ズレそのものは0.2psに抑えられる。

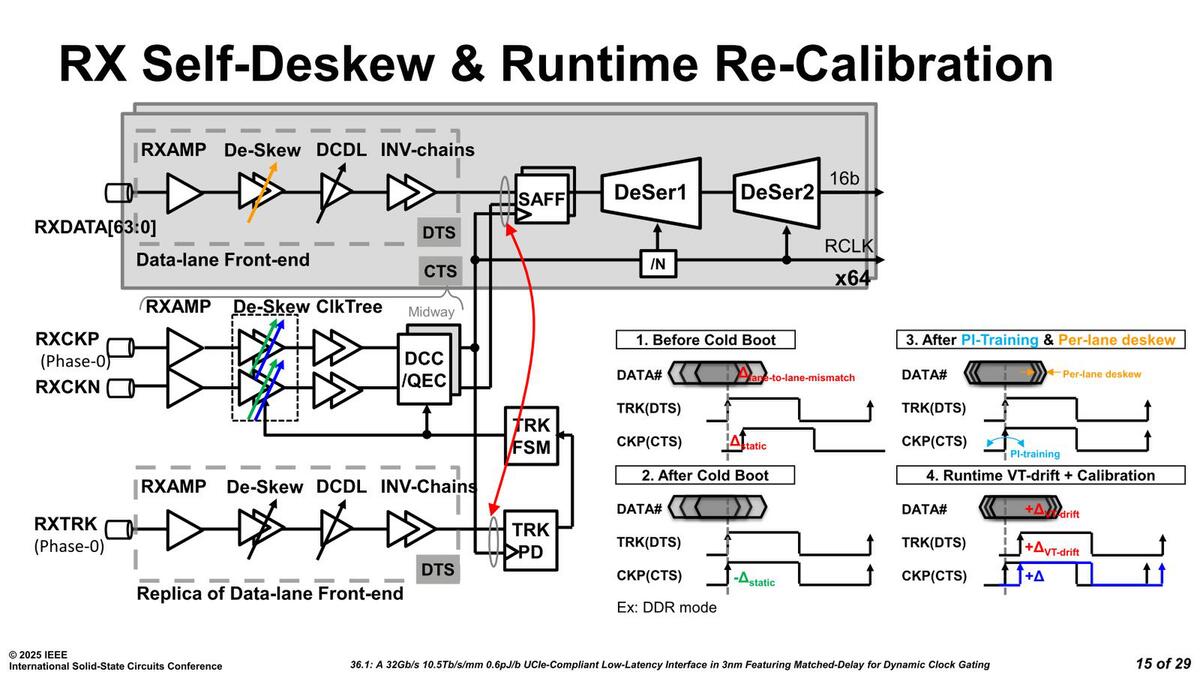

また受信側は、Self-DeskewおよびRuntime Re-Calibration(自動でのタイミング調整と、動的な校正機能)を搭載しており、これによってさらにズレを抑え込める。

具体的には、以下のことが実行される。

- コールドブート、つまり初めて電源を入れたときには、各レーンごとに設けられたSKEW調整用のバッファを通して、クロック信号をTRK(Track信号)に合わせることで、データ信号とクロック信号の静的ミスマッチを最小限に抑える。それが終わった後は、De-Skew機能を利用して、ずれを最小限に抑える。

- After PI-Training & Per-lane deskewは、最初のタイミング調整が終わったら、データレーンごとにSKEW調整をして、個々のレーンに用意されたBIST(Build In Self Test)機能を利用しながらData Eyeを最大になるように自動調整する。

- Runtime VT-drift + Calibration、つまり実際にデータを送受信している間に再びCKPとTRKの不一致が確認された場合、Clock信号のDe-Skewバッファを一致するように自動調整する。

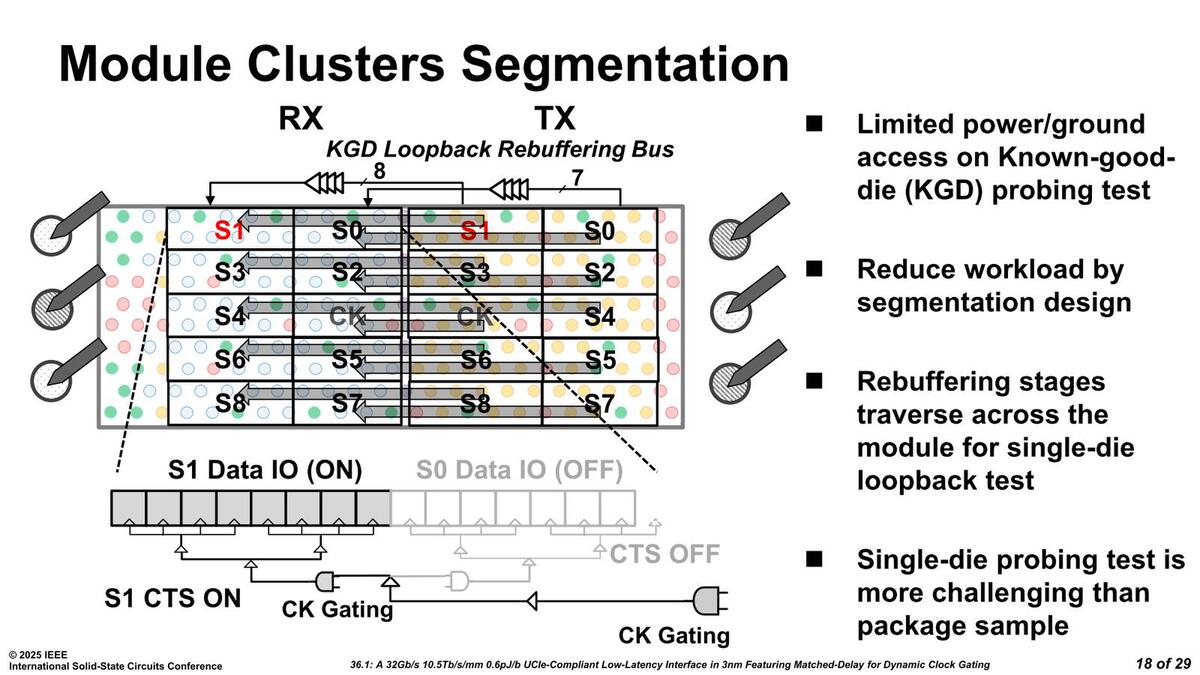

下の画像がインターポーザー(とその上に重なるSoCダイ)の物理的な配置である。問題としてKGD(Known Good Die:良品ダイ)の選別が品質テストには不可欠だが、バンプピッチが小さいため、電源/GNDのバンプへのアクセスが制限されることが挙げられているが、これをどう克服したかの説明はない。

ちなみに最大で32GT/秒の高速テストを、IRドロップや電源変動の影響を最小に抑えながら実施するため、信号はS0~S8まで9つのセグメントに分割され、BER(Bit Error Rate)のテスト時には1つのセグメントのみをアクティブにするように実施されたとのことである。

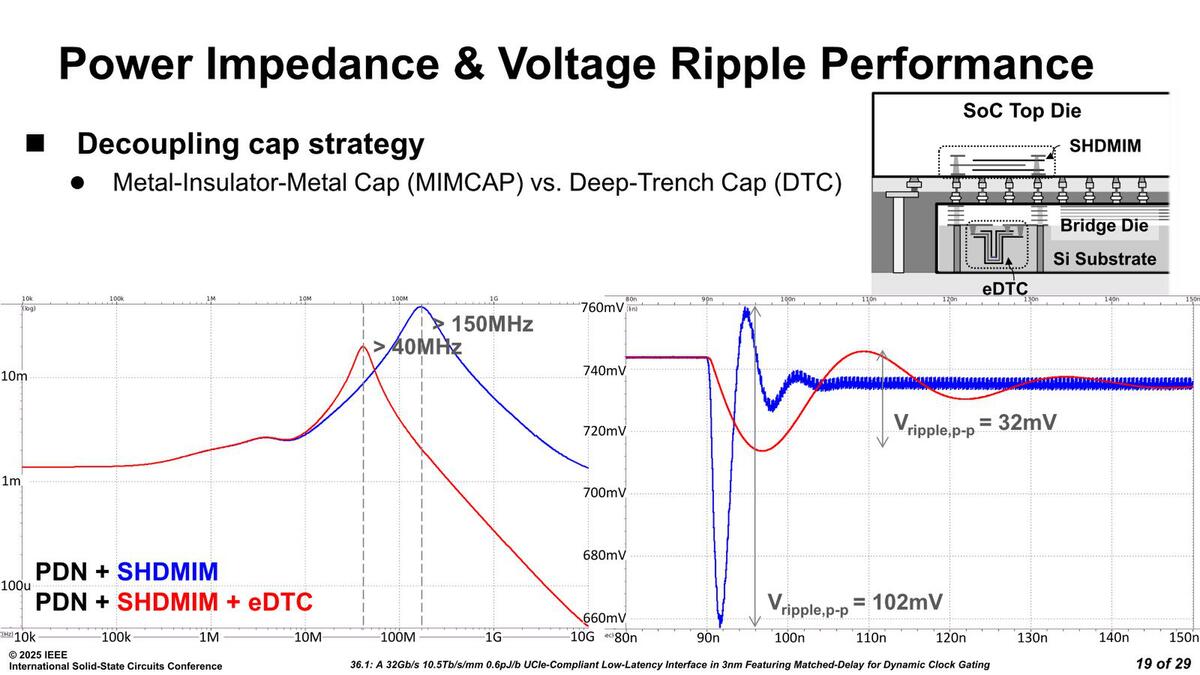

電源供給に関しては、SHDMIM(Super High-Density Metal-Insulator-Metal)コンデンサーをインターポーザーの上に配した場合と、これに加えてeDTC(embedded Deep Trench Capacitor)を組み合わせた場合の両方を比較し、eDTCを利用することで大幅にリップルを低減できた(102mV→32mV)ことを確認している(下のグラフの右側)。

左のグラフはインピーダンス特性で、SHDMINは1mm2あたり50nF程度の容量しかないため、電源インピーダンスを軽減できるのは150MHz以上だが、eDTCは1mm2あたり1100nFの容量を確保できるため、40MHz以上の電源インピーダンスを軽減できるとしている

そもそもシリコンインターポーザーは表に露出しない(ダイかパッケージの下に隠れている)ので、シリコンインターポーザーの真上にSHDMINを載せることはできず、パッケージを経由して載せる格好になる。したがってeDTCよりも効果が薄いのは理解できるが、逆に言えばシリコンインターポーザーにeDTCを埋め込む(これは当然高コストになる)のがUCIeで安定動作を望む場合は必須ということかもしれない。

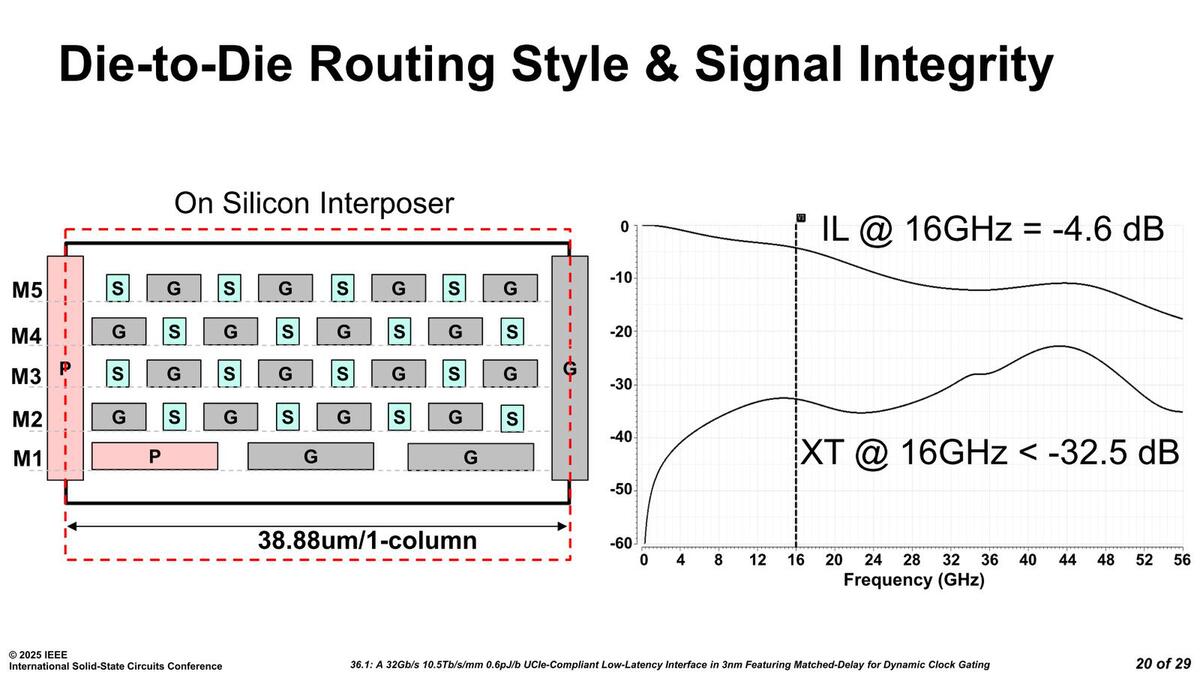

そのシリコンインターポーザーを横から見た断面図が下の画像で、5層の配線層を持つ構造となっている。Sが信号、GがGND、PがPower(電源)で、信号配線をGNDで囲うように配することで配線クロストークノイズ(信号同士の相互干渉)を最小限に抑えたとする。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります