第817回

実現困難と思われていたUCIe互換のチップレット間インターコネクトをTSMCとAMDが共同で発表 ISSCC 2025詳報

2025年03月31日 12時00分更新

ISSCCのSession 36は"Ultra-High-Density D2D and High-Performance Optical Transceivers"というセッションで、名前の通りチップレット向けの高速インターコネクトに関する論文なのだが、その冒頭の36-1はTSMCとAMDが共同で発表した"A 32Gb/s 10.5Tb/s/mm 0.6pJ/b UCIe-Compliant Low-Latency Interface in 3nm Featuring Matched-Delay for Dynamic Clock Gating"というものである。要するにUCIeの仕様に互換となるチップレット間インターコネクトを試作してその特性を確認した、というものだ。

TSMCは当然ながら、顧客がUCIeを利用したチップレットを製造することがあり得るため、事前にその検証をしておく必要があるのだが、そこにAMDが協力しているのがおもしろい。少なくとも論文を読む限り、次世代で積極的にUCIeを自社製品に取り込むとわけではなく、UCIeが普及する時代に備えて自社でもUCIeに関する技術的な蓄積をしておきたかった、というのが目的のようだ。

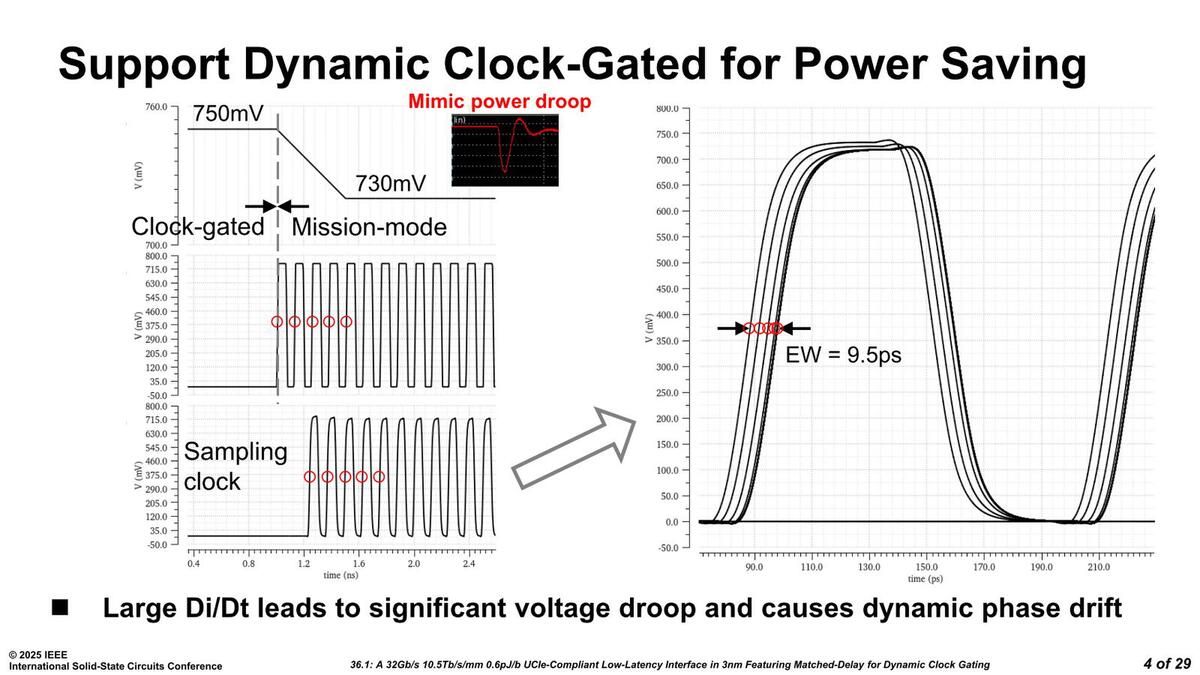

省電力モードからフル稼働モードに切り替わる際に

供給電圧が大幅に下がる可能性がある

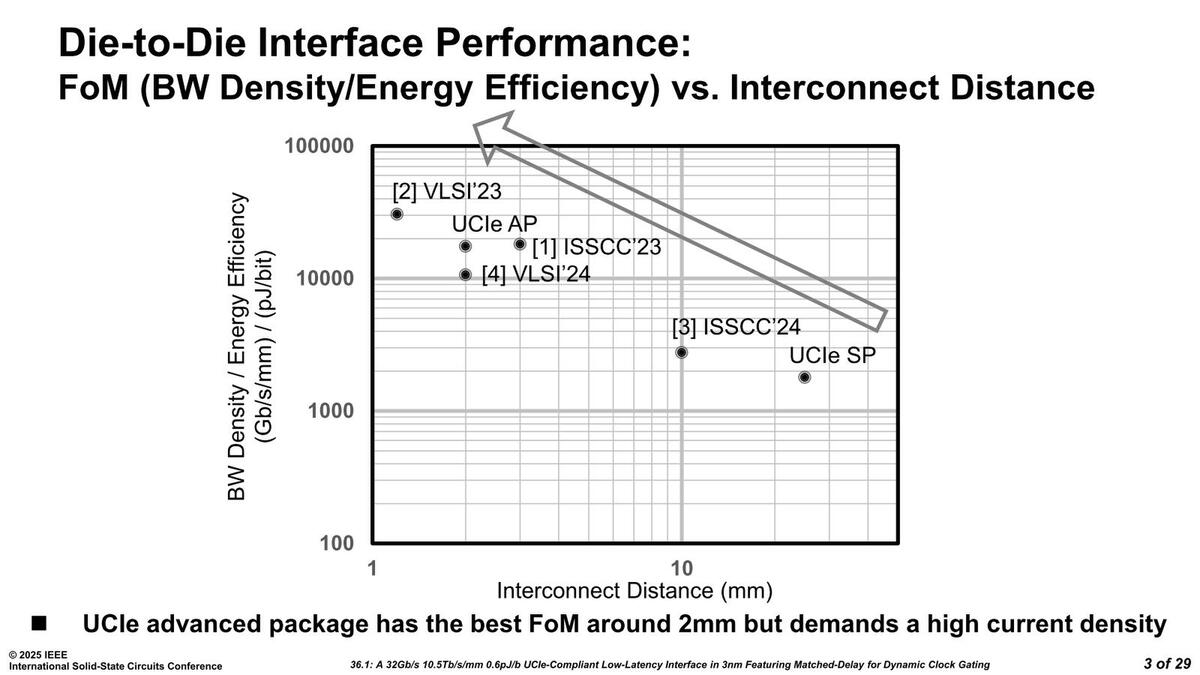

チップレットを利用する研究動機は明白で、より大量の帯域をより低い電力で利用できるようにしないと、チップレットの構想そのものが破綻する。UCIeではStandard PackageとAdvanced Packageの2種類の接続I/Fを定義しており、Standard Packageが10~25mm、Advanced Packageでは2mm以内の接続の場合の仕様を定義している。

ここで問題になるのがClock Gatingである。Clock Gatingそのものに関してはUCIeの仕様書でもきちんと定義されており、具体的にClock Gatingを行なう場合のプロトコルなどが定義されているのだが、Clock Gating ModeからNon-Gating Modeへの移行、つまり省電力モードからフル稼働モードに切り替わる際に、瞬間的に電流サージが発生し、これにともない供給電圧の大幅なドロップの可能性があるとされる。

電圧ドロップが発生すると、これにともない位相の遅れが発生するケースがあることも示されている(上図右側)。チップレット間で安定して通信するためには、こうした電圧ドロップや位相遅れをなるべく減らす必要がある。

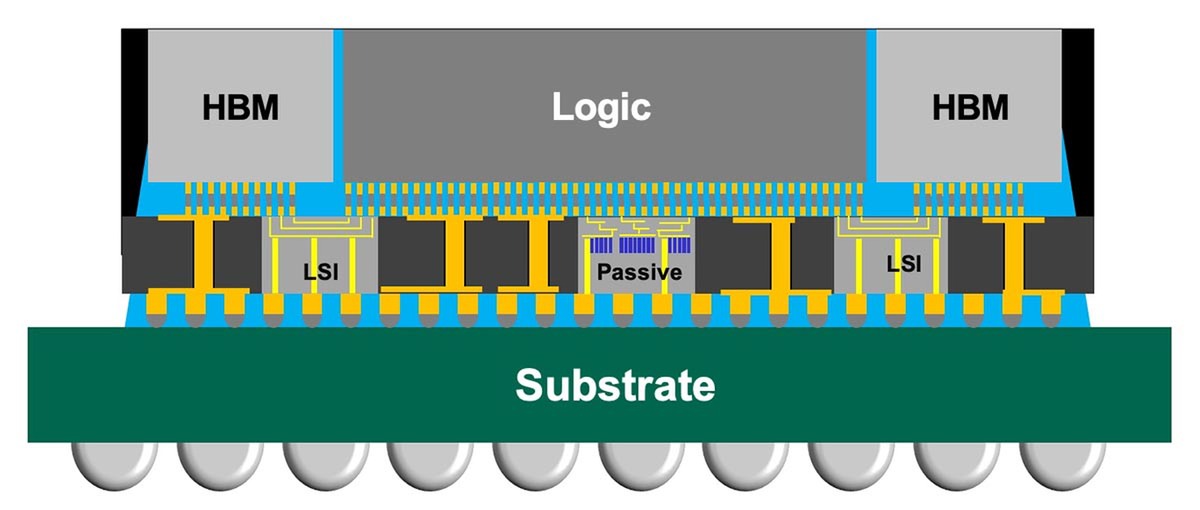

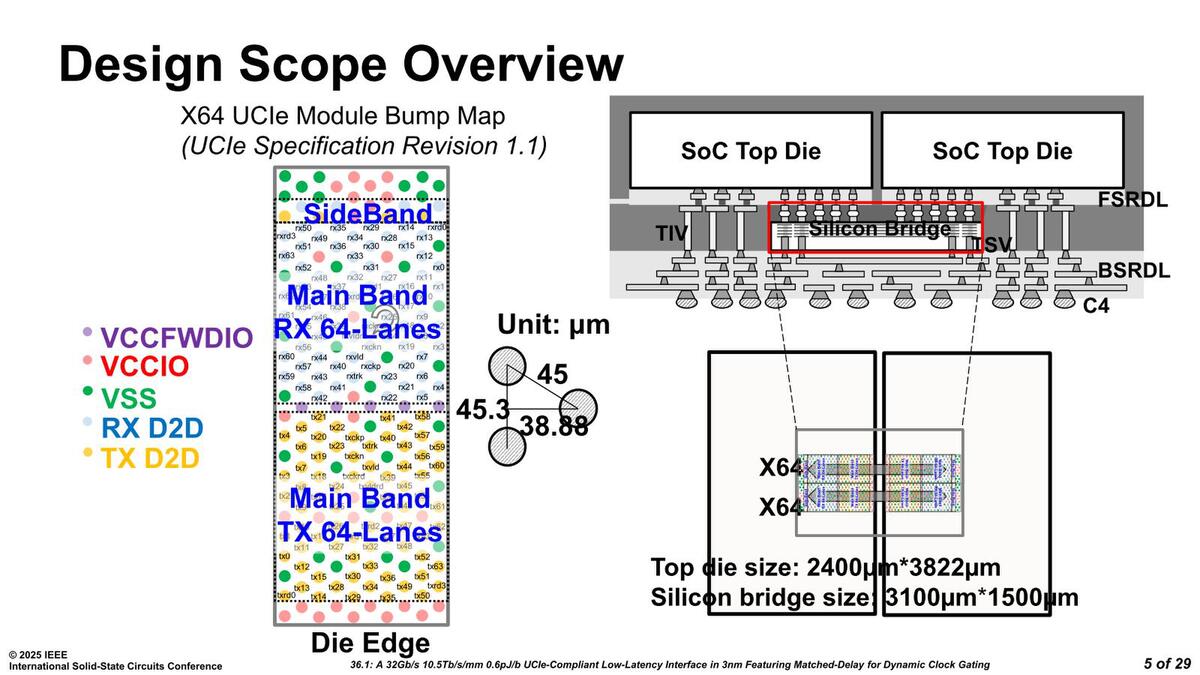

今回テストでは、2つのチップを1つのシリコンブリッジで接続する実装を利用している。要するにCoWoS-Lである。

2つのSoCチップの間を2組のx64レーンでつなぐ方式。実際にはこれに加えてSidebandやFW-CLK、Valid Trackといった信号と、あと電源/GNDも入る。バンプの配置はUCIeの仕様書の中の10-column x64 Advanced Package Bump Mapに準拠した構造で、バンプピッチは45μmである

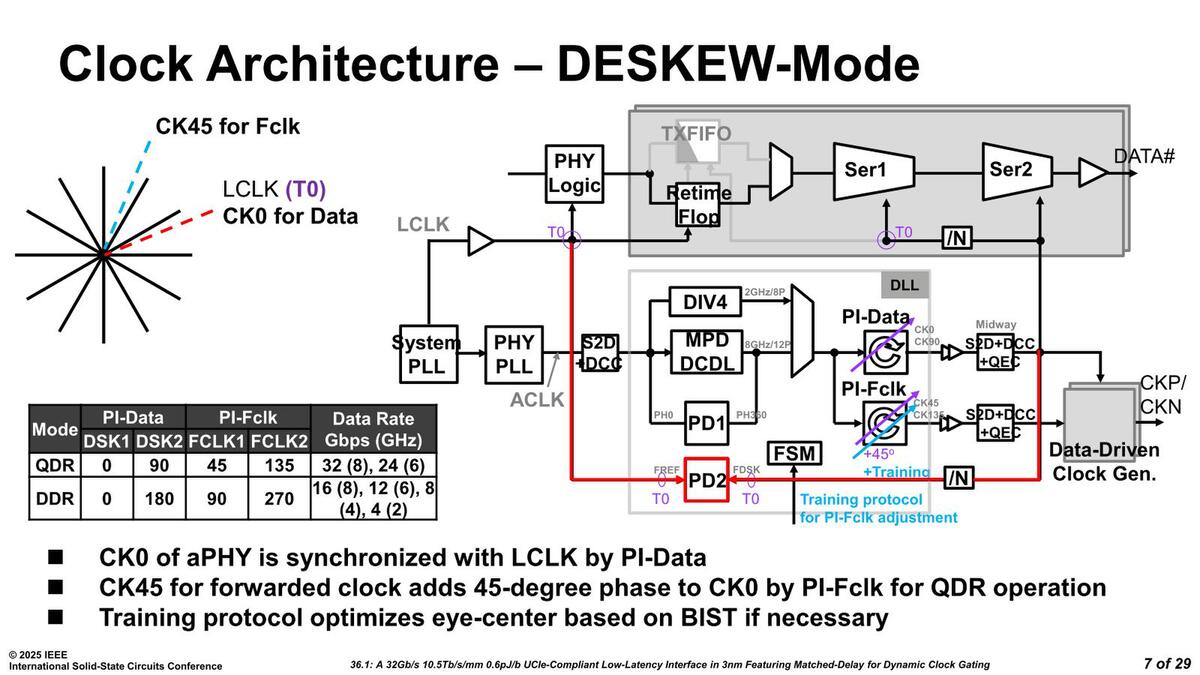

この上で回路設計にいろいろ工夫を凝らした。まずClocking。UCIeは本質的にパラレルバスなので、全部の信号はクロック信号に同期する形で送受信される。基本は送信側がクロック信号を生成し、これを受信側にデータと一緒に送信。受信側はそのクロック信号を利用して受信することになる。

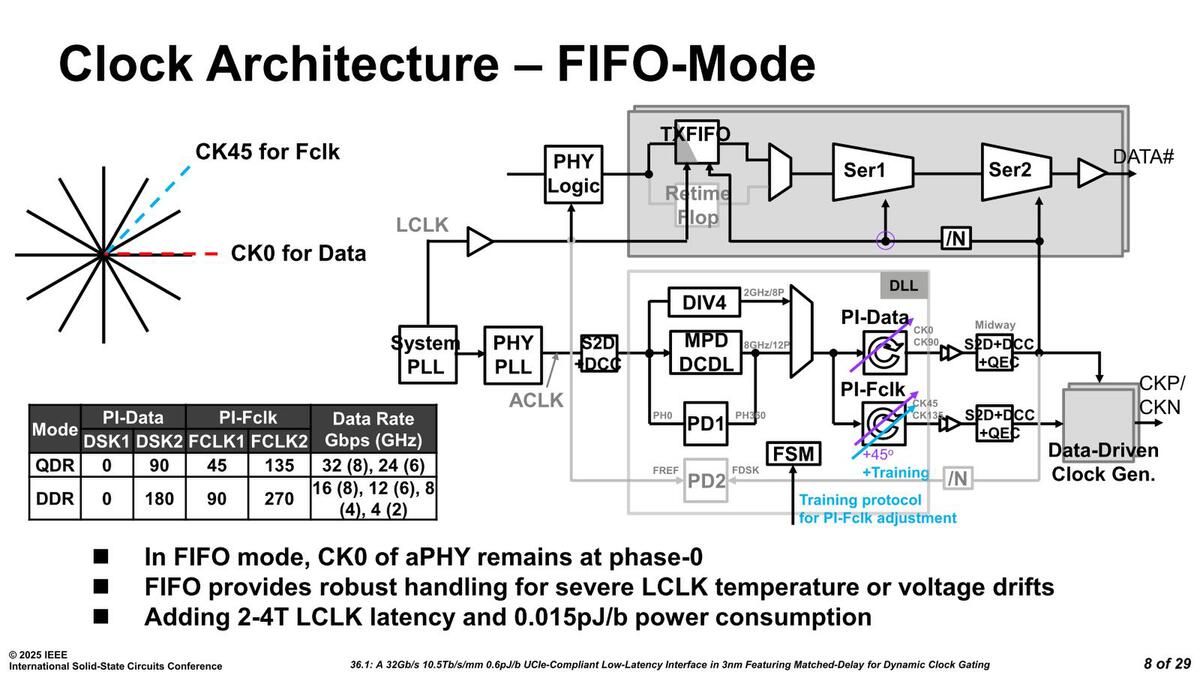

クロック生成には、Flip-Flopをベースにした低レイテンシーのDESKEW-Modeと、温度や電圧の変動が激しい場合に対応するFIFO-Modeの2種類の動作モードが用意されている。DESKEWモードでは、図中で赤く表示された部分が有効化される。

FIFO-Mode。FIFOで長めにバッファを構成するため、レイテンシーが2~4クロック分余分にかかるうえ、若干ではあるが消費電力も増える。それでも、変動が激しくなると通信に支障が出るので、それに比べれば許容範囲ということなのだろう

ここのPD2というのはPhase Detectorの意味で、LCKLとACLKの位相のズレを早いタイミングで検出して、補正を掛ける仕組みである。一方FIFOモードではこのフィードバックがなくなっている。その代わりに、長めにFIFOのキューを取り、ここでクロックの変動を吸収する仕組みだ。

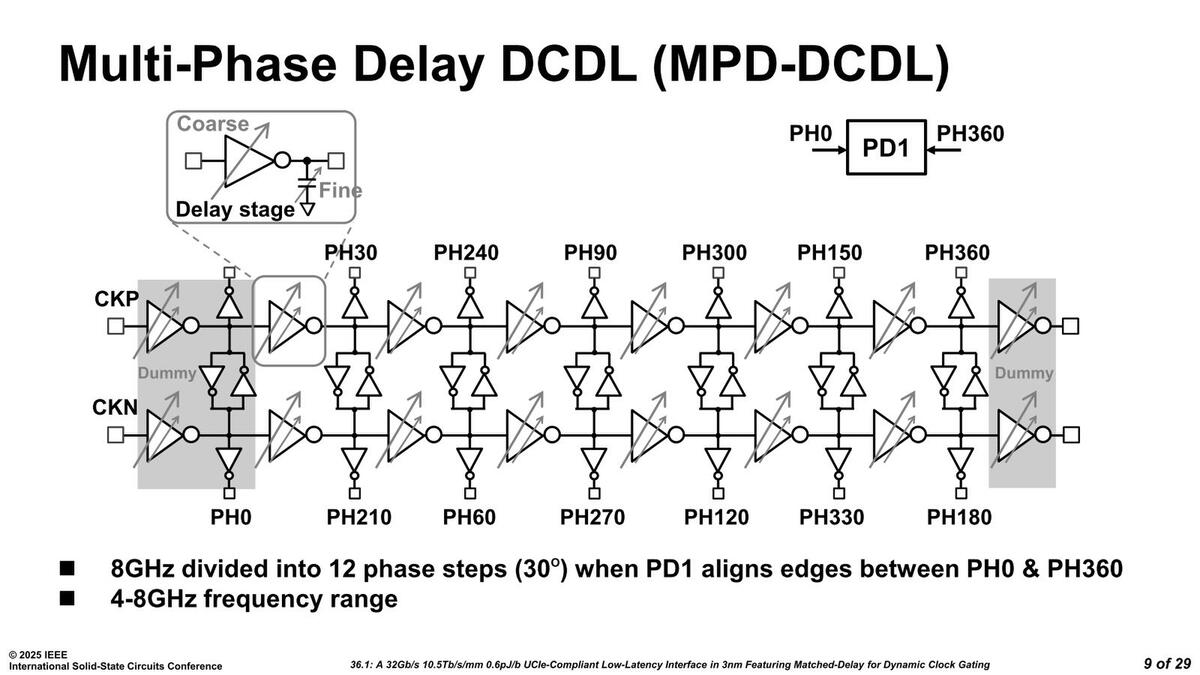

上の画像で出てきたMPD DCDLの中身が下の画像だ。12個のインバーターを並べており、おのおのが30度の位相を変更するので、トータルで360度の位相変更となる。この際に細かくタイミングを調整することで、4~8GHzのクロック信号を正確に生成できるようにしている。

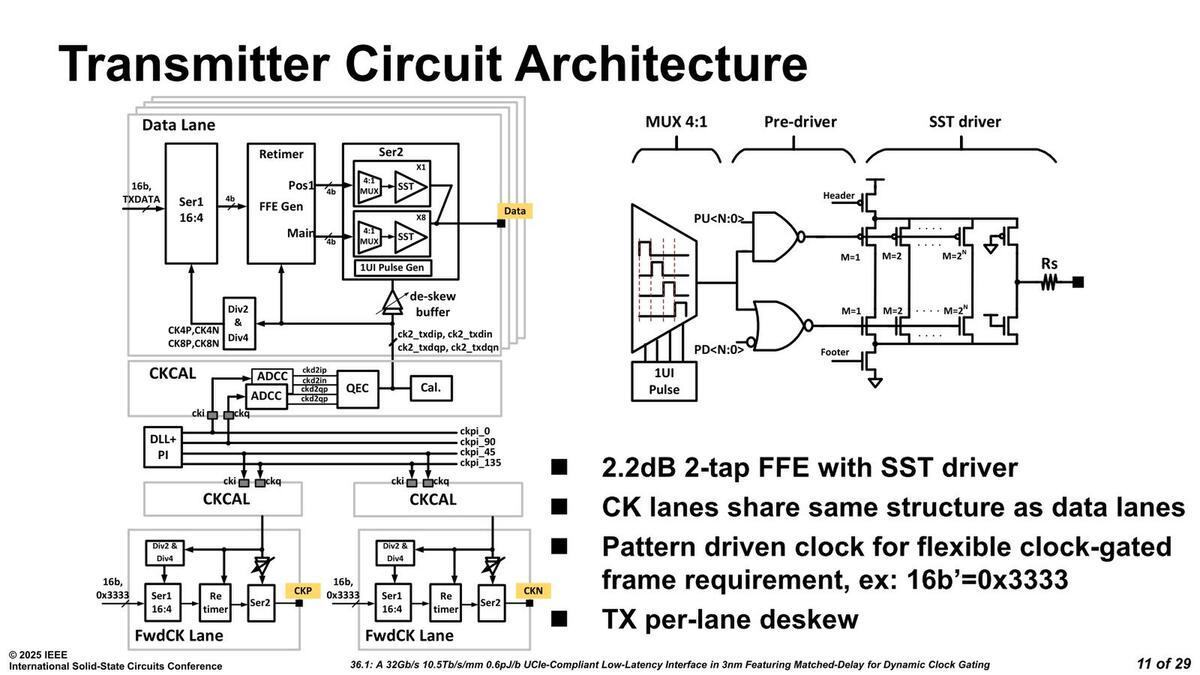

送信側回路は、16bitで来たデータをまず16:4で4倍速の信号にし、次いでこれを4:1でトータル16倍速にする仕組みである。信号経路は2mm未満とはいえ、最大32GT/秒の信号になるので、多少は挿入損失が発生する。これに対処するために、2tapのFFE(Feed Forward Equalizer)が実装されており、これで2.2dB程度の損失をカバーする仕組みだ。

ここで、DLL+PIから4本のクロック信号(ckpi_0/45/90/135)が出ていることに注意されたい。データおよび受信側へ転送するクロック信号は、この4つのクロック信号(それぞれ位相が0/45/90/135度になっている)を利用して遅延と同期を一致させるように構成されている。

図の下の方に2つのFwdCKレーンとして構成されているのが、受信側に転送するクロック信号生成ブロックであるが、ここに入力されるパターン(ここでは0x3333が例として示されている)を利用してClock Gatingができるようになっている。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります