第813回

Granite Rapid-DことXeon 6 SoCを12製品発表、HCCとXCCの2種類が存在する インテル CPUロードマップ

2025年03月03日 12時00分更新

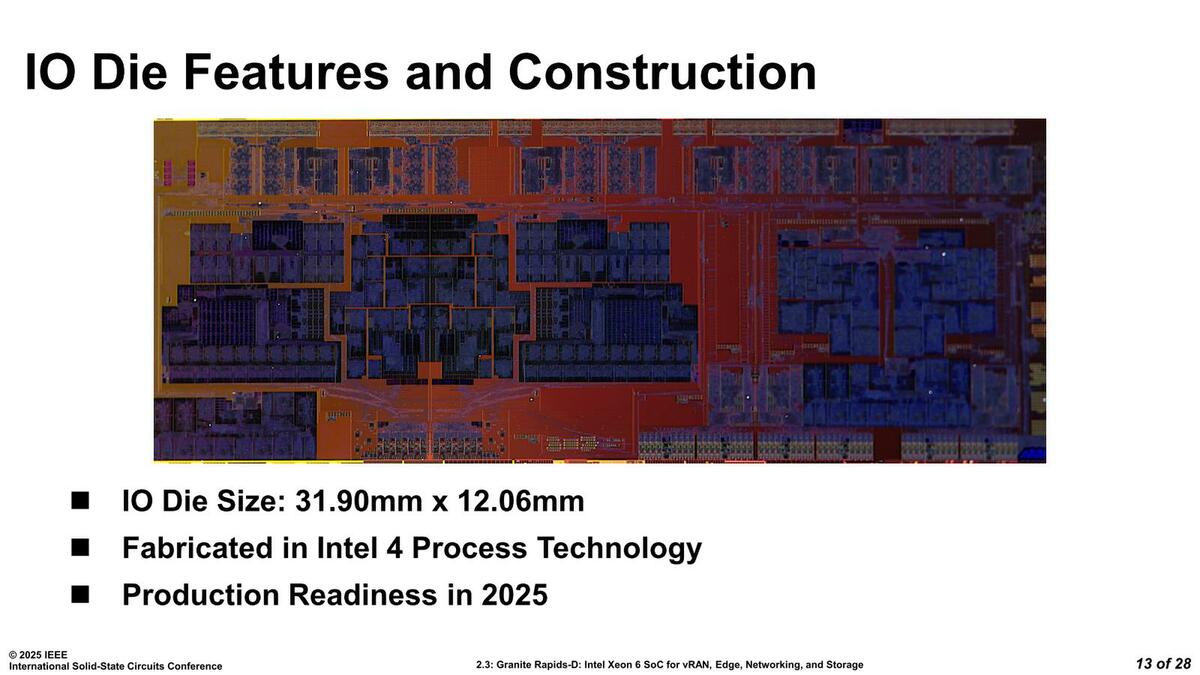

IOタイルはIntel 4で製造

統合電圧レギュレーターFIVRも復活していた

IOタイルに関しては新規なわけだが、その中身が紹介された。一番驚いたのは、このIOタイルがIntel 4で製造されていたことだ。

Meteor Lakeの生産が一段落したことで、IrelandのFab 34をどうするつもりなのかという疑問があった(当初はIntel 3に転換するのでは? と思ったのだが、昨年6月に同社はFab 34に関連する合弁事業体の持ち分の資産の49%をApollo Global Managementに売却している)。

インテルは51%の資産を保有しており、所有権と運営管理はインテルが引き続き保持するものの、合弁事業体はFab 34で自身のウェハ―を製造する権利を持っており、つまりインテル以外の企業がFab 34を利用して独自のウェハ―を製造することが可能となる。

こういう状況では、製造装置の入れ替えは(不可能ではないが)なかなか大変になるわけで、引き続きIntel 4を利用する「なにか」を製造しないといけないのだが、その1つがXeon向けのIOタイルだったわけだ。今年から量産開始ということなので、試作はあるいはOregonのD1で行なわれていたのかもしれない。

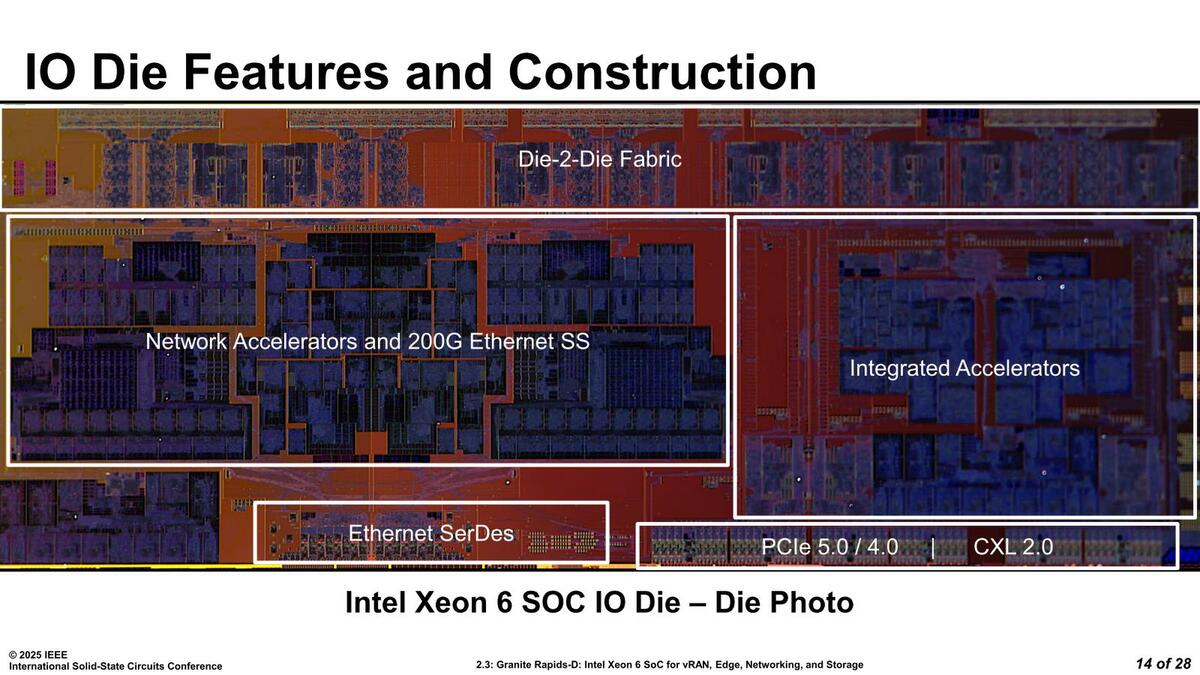

そのIOタイルの中身が下の画像だ。多分横幅はEMIBを利用したDie-2-Die Fabricの幅で規定されてしまうためだろうか? 内部的にはみっちりというよりはかなり間隙が目立つ、ゆったりしたレイアウトに思える。

一番大きいのがイーサネットアクセラレーターとイーサネットのMAC/PHYとなっている。中央がアクセラレーターで、その両脇に200Gイーサネットが4ポートづつ配される格好だろうか? イーサネットのMACからPHYへの配線に結構苦労している感がある

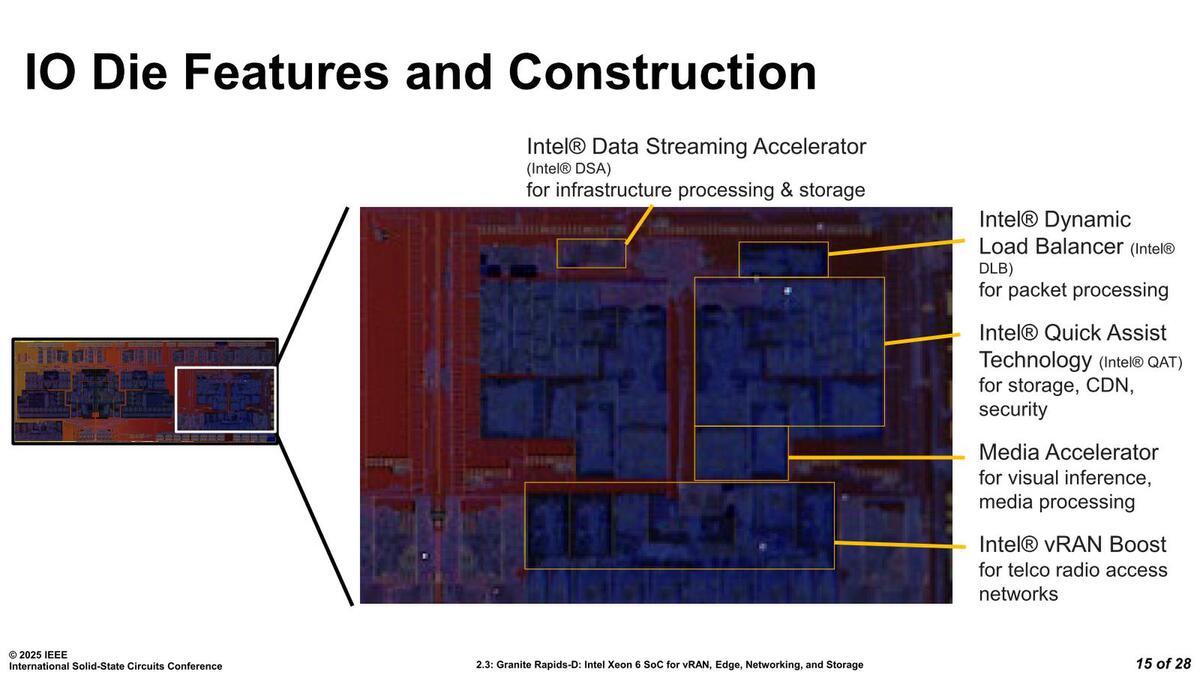

そのアクセラレーター部が下の画像だ。DLBおよびDSAに関しては非対称だが、QATとメディア・アクセラレーターは左右対称構造になっている。最初のページで示した表のQATやDLB、DSAの数は"デフォルト"である。要するに連載695回で説明したIntel On Demandで、後から利用するアクセラレーターの数を変更できる(あるいは無効化していたアクセラレーターを有効化できる)という機能がXeon 6には搭載されており、それは今回のGranite Rapids-Dでも同じである。

実はIntel Arkには今回から追加されたメディア・アクセラレーターの数が記載されていない(ので表にも反映していない)のだが、これもデフォルトは1、最大2が可能なのではないかと思われる。

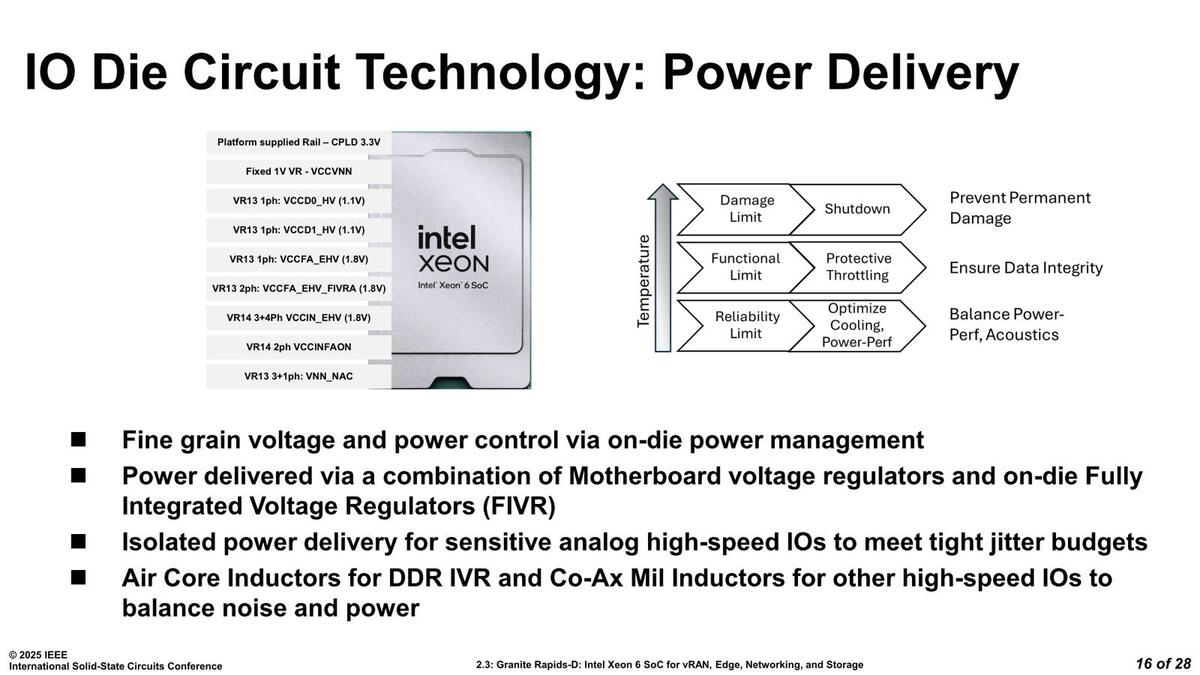

細かいところでは、今回からFIVR(Fully Integrated Voltage Regulator)が復活している。電源変動に素早く対応するためには、なるべく消費しているところ(つまりCPUコア)の近くに電源レギュレーターを置くのが好ましい。通常では基板上にレギュレーターが置かれるが、例えばRyzenではLDO(Low Drop Out)レギュレーターをオンダイで搭載している。

LDOは反応速度こそ早いものの効率は悪いので、あんまり大きな電圧変換をさせると無駄に消費電力が増える。なので通常はLDO以外の外部のレギュレーターと組み合わせ、例えば12V→1.5Vは外部のレギュレーターに任せ、1.5Vを1.45Vや1.43Vなど、細かくニーズに合わせて微調整する部分だけを担う格好になる。

ただこれは大きな消費電力変動には追従しきれない公算が高い。インテルも、特に低消費電力時にFIVRの効率が悪すぎるということで一旦省いたが、多分Granite Rapids-Dのような常時稼働する製品には使えると判断したのかもしれない。ただこれ、コンピュートタイルに統合しているのか、IOタイルに統合しているのかは不明である(なんとなくIOタイルっぽいが)。

説明は他にI/O周りの回路などについても行なわれたが、このあたりは割愛する。重要なのは、Xeon向けに真っ当な機能分割をしたチップレットのアーキテクチャーを投入し始めたということかと思う。この路線を真っ当に突き進んでほしいと祈るばかりである。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります