第813回

Granite Rapid-DことXeon 6 SoCを12製品発表、HCCとXCCの2種類が存在する インテル CPUロードマップ

2025年03月03日 12時00分更新

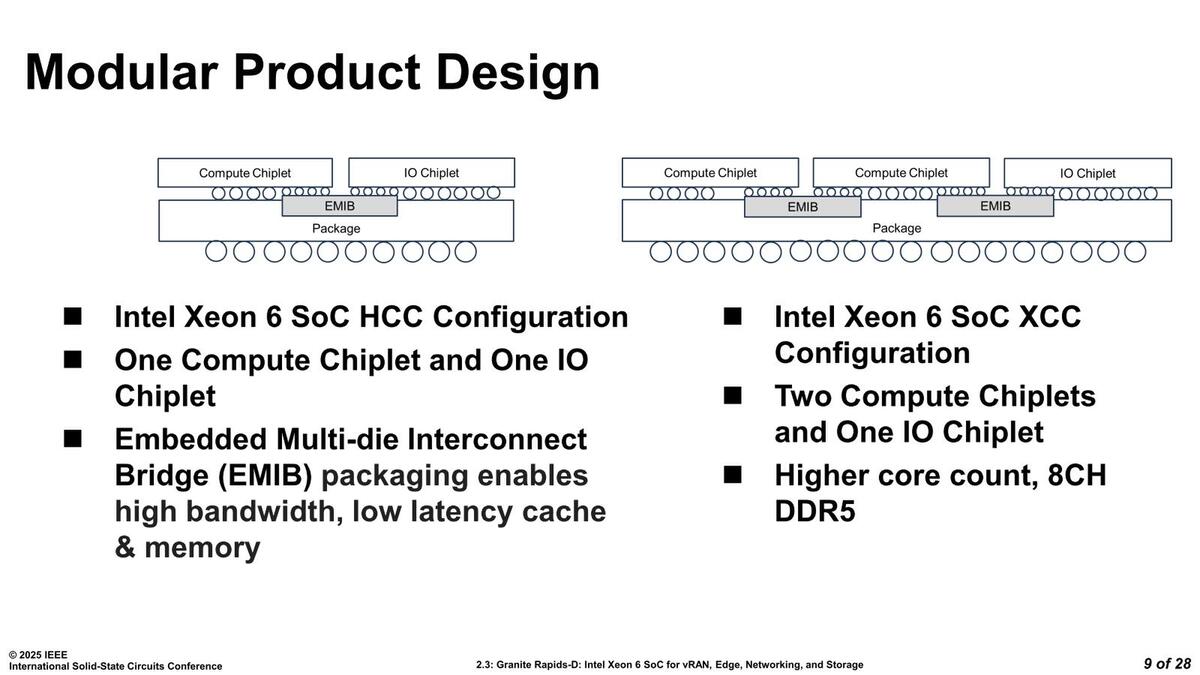

Granite Rapid-DにはHCCとXCCの2種類が存在する

さてこのあたりから、発表と実際の製品の間に微妙なミスマッチがある。今回発表されているのは最大42コアだが、実際には今後もっとコア数の多い製品も予定しているらしい。そうなるとコンピュートタイル(下の画像では今度は"Compute Chiplet"に名前が変わっている。統一してほしいと強く思う)が1つだけではカバーしきれない。

一方で最小は12コアだから、こちらはコンピュートタイルが一つで十分足りる。そこで、以下の2バージョンの構成を用意したとしている。

| HCC | コンピュートタイル×1+IOタイル |

|---|---|

| XCC | コンピュートタイル×2+IOタイル |

この場合、間は上の画像のようにEMIBでつなぐかたちだ。で、どうも2月に発表されたものはHCCの構成だけであり、XCC製品は今後投入されることになるようだ。

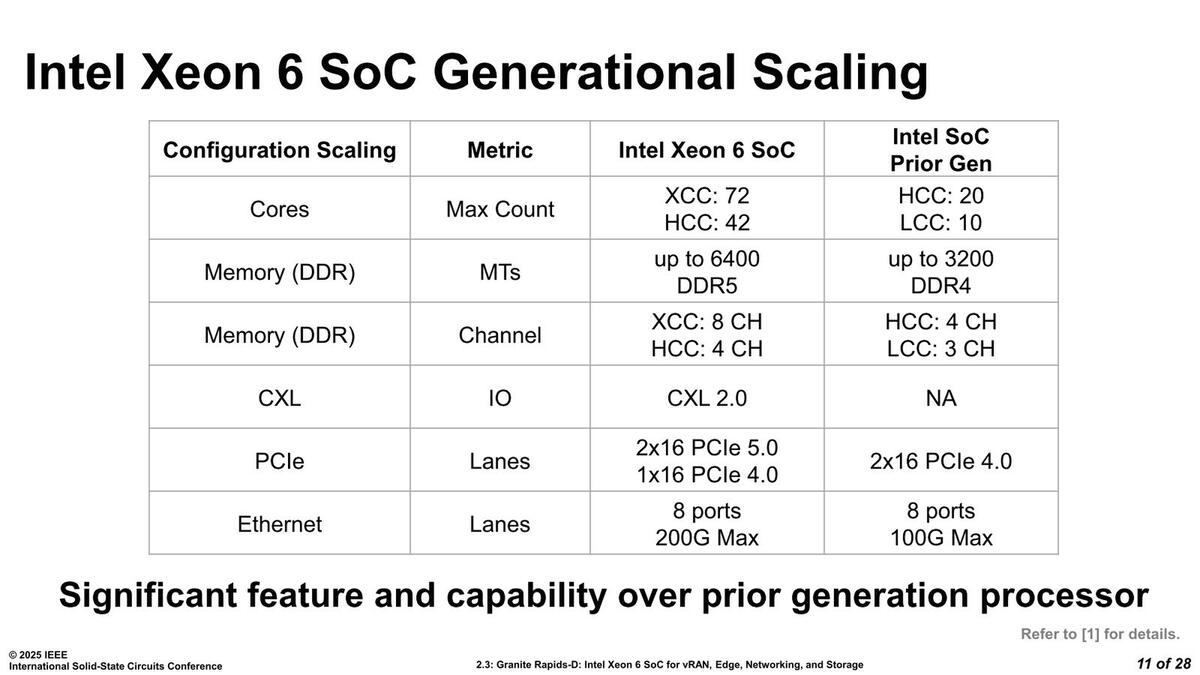

もう少し詳細な構成が下の画像である。今回発表の製品はすべてHCCに属しており、これとは別に8ch DDR5を利用可能で最大72コアのXCC SKUも一応用意はあるらしい(本当に出荷するかどうかはまだ不明だが)。

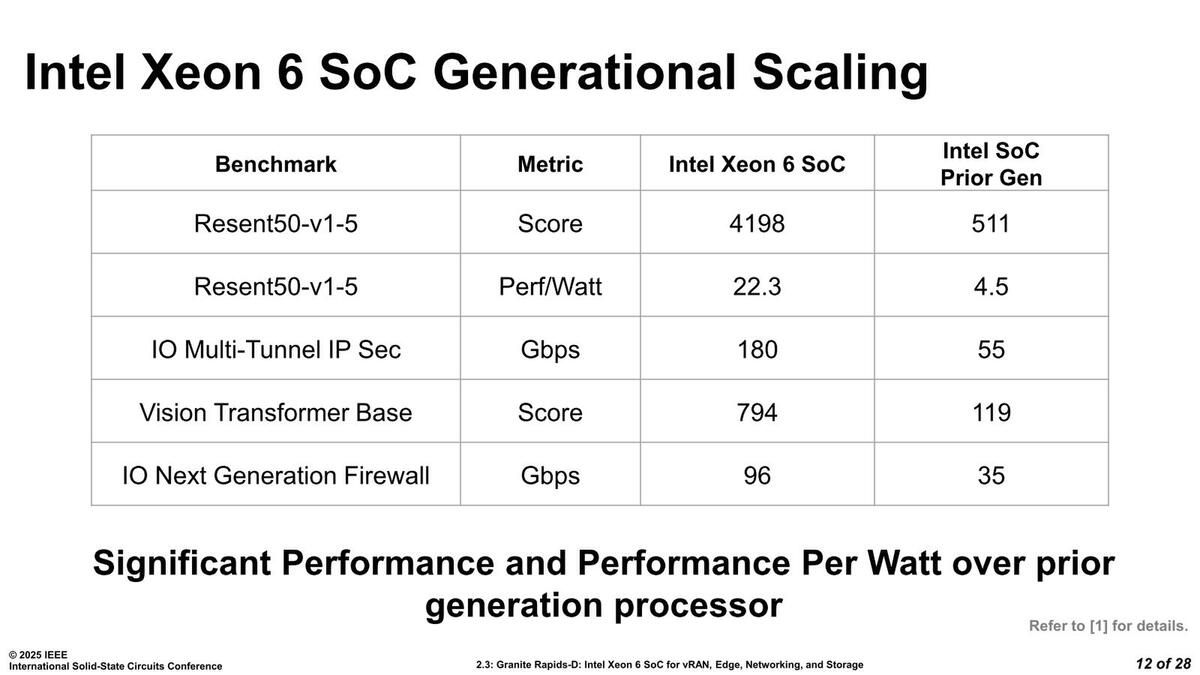

その前世代製品と性能を比較したのが下の画像である。例えばResNet-50では性能8倍、性能/消費電力比5倍となっており、他の性能もやはり3倍や5倍など、結構な性能向上が見られるとしている。

もっともこれ比較対象がXeon D 2899NTで、比較対象の性能が低すぎる感は否めない

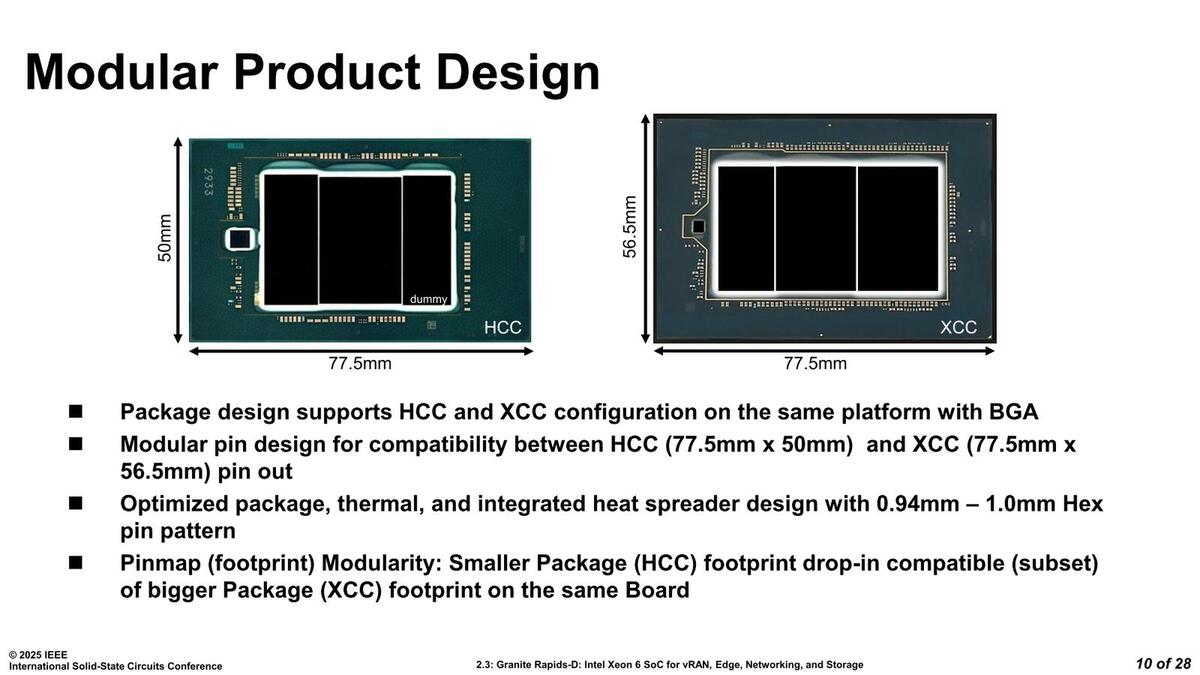

ちなみにHCCとXCCの実際のパッケージ写真が下の画像だ。HCCとXCCではそもそもパッケージが異なる、という話は連載787回で説明したが、見事に違っているのがわかる。

そもそも表に示されているように、今回発表のGranite Rapids-DはFCBGA4368なのに対し、通常のGranite RapidsはFCLGA4710が利用されている。つまり6.5mmの幅の差が342ピン分のコンタクトの差であり、この342ピンがDDR5 4ch分の信号ピン(+多少は電源や制御信号もありそうだが)になる。

一応このHCCとXCCではフットプリントに互換性があるという話なのだが、もう1つ注意すべきは"FCLGA4368"ではなく"FCBGA4368"なことだ。つまりソケットに搭載するのではなく、直接基板にリフローではんだ付けすることが前提になっているわけだ(通信機器向けでは珍しい話ではない)。

ただ、そうなると将来登場するかもしれないXCCもやはりBGAでの提供なのか、それともXCCはそのパターンの上にソケットを搭載し、そこに搭載する形になるのか、現状ではわからない。

さて上の画像でコンピュートタイルの大きさは、パッケージの対比からおよそ18.5×31.2mmと推察される。このコンピュートタイルはおそらく昨年9月に発表されたPコアXeonのものをそのまま利用しているのだろう。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります